Цифровыеустройства. Технология idl

Скачать 3.16 Mb. Скачать 3.16 Mb.

|

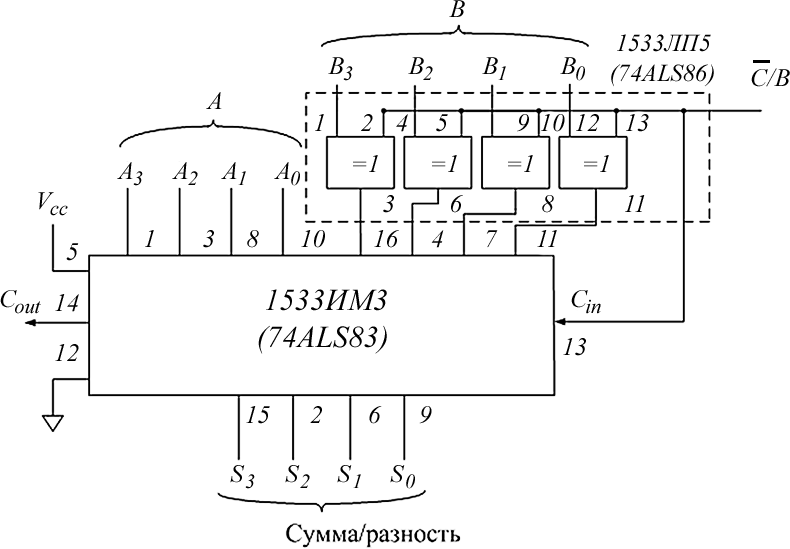

Суммирование/вычитание в системе счисления с дополнительным кодомВычитание двоичных чисел может осуществляться с использованием полных двоичных вычитателей, однако этот метод используется редко. Вза- мен этого вычитания обычно используется арифметика в системе счисления с дополнительным кодом, и тогда только двоичные сумматоры используются для выполнения операций суммирования и вычитания. Даже с учетом того, что потребуется еще и схема для получения дополнения, этот метод является предпочтительным. Обычно используется комбинированная суммирующая/вычитающая схема, в которой вид выполняемой операции (суммирование или вычитание) зависит от управляющего сигнала. Рассмотрим схему рис. 3.9, в которой параллельный сумматор соеди- нен таким образом, чтобы выполнять или суммирование, или вычитание.  Когда управляющий сигнал имеет низкий уровень (лог. 0) на входе Сiп, то и на одном из входов схем ИСКЛЮЧАЮЩЕЕ ИЛИ также лог.0, по- этому биты числа B передаются на входы сумматора без изменения. Схема работает как сумматор. Когда управляющий сигнал имеет низкий уровень (лог. 0) на входе Сiп, то и на одном из входов схем ИСКЛЮЧАЮЩЕЕ ИЛИ также лог.0, по- этому биты числа B передаются на входы сумматора без изменения. Схема работает как сумматор.Рис. 3.9. Сумматор/вычитатель Когда управляющий сигнал имеет высокий уровень, на вход Сiпода- ется лог.1 и каждая схема ИСКЛЮЧАЮЩЕЕ ИЛИ инвертирует биты числа В. Таким образом осуществляются инвертирование каждого бита числа Ви прибавление 1 (по входу Сiп).В результате выполняется операция дополне- ния с числом В. При этом суммирование числа Ас дополнением числа Врав- носильно вычитанию числа В из числа А. ПОРЯДОК ВЫПОЛНЕНИЯ ЛАБОРАТОРНОЙ РАБОТЫ Оборудование и компоненты: универсальная лабораторная установка IDL-800; ИС 1533ЛП5(74АLS86) – четыре логических элемента ИСКЛЮЧАЮЩЕЕ ИЛИ; ИС 1533ЛИ1(74АLS08) – четыре логических эле- мента 2И; ИС 1533ЛЛ1(74АLS32) – четыре логических элемента 2ИЛИ; ИС 1533ИМ3(74АLS83) –четырехразрядный сумматор; ИС 1533ЛН1 (74АLS04) – шесть инверторов. Исследование сумматоровПолусумматор Используя логические элементы, собрать схему полусумматора (см. рис. 3.2). Изменяя состояния входов Аи В, исследовать работу полусумматора, получить таблицу истинности полусумматора (см. табл. 3.1). Полныйсумматор Используя логические элементы, собрать схему полного сумматора (см. рис. 3.4). Изменяя состояния входов А, В, С 1,исследовать работу полного сумматора, получить таблицу истинности полного сумматора (см. табл. 3.2). |