Answer 1 Вопросы к зачету АЭВМиВС_2021. Электронная вычислительная машина

Скачать 1.84 Mb. Скачать 1.84 Mb.

|

|

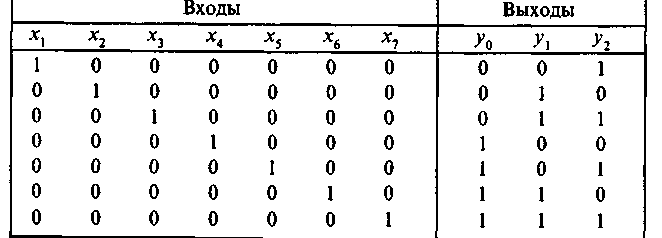

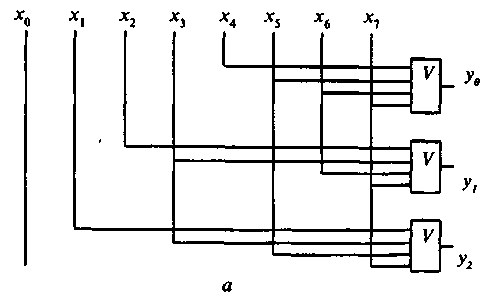

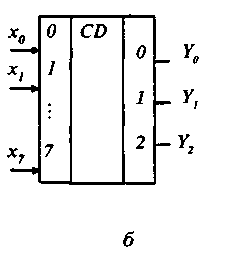

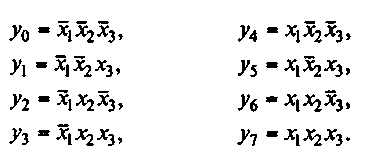

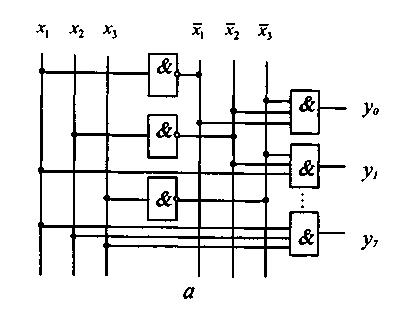

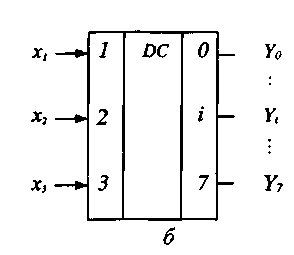

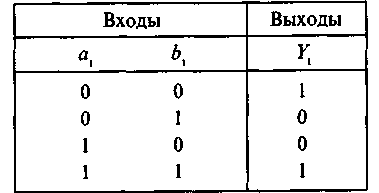

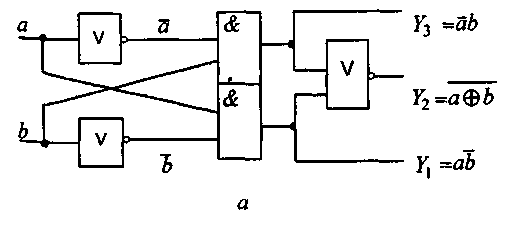

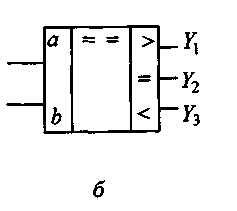

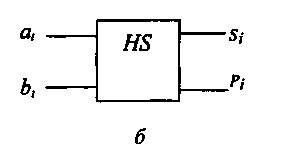

К формирующим элементам относятся различные формирователи, усилители, усилители-формирователи и т.п. Данные элементы служат для выработки определенных электрических сигналов, восстановления их параметров (амплитуды, полярности, мощности, длительности). В каждой ЭВМ имеются специальные блоки, формирующие сигналы тактовой частоты, серии синхронизирующих и управляющих сигналов, которые координируют работу всех схем ЭВМ. Интервал времени между импульсами основной частоты называется тактом. Длительность такта является важной характеристикой ЭВМ, определяющей ее потенциальную производительность. Время выполнения любой операции ЭВМ связано с определенным числом тактов. Простейшие логические элементы преобразуют входные сигналы в соответствии с элементарными логическими функциями. В свою очередь, полученные сигналы могут формировать следующий уровень сигналов и т. д. Сложные преобразования в соответствии с требуемыми логическими зависимостями могут приводить к построению многоуровневых схем. Каждая такая схема представляет собой композицию простейших логических схем. Запоминающим элементом называется элемент, который способен принимать и хранить код двоичной цифры (единицы или нуля).. Элементы памяти могут запоминать и сохранять исходные значения некоторых величин, промежуточные значения обработки и окончательные результаты вычислений. Комбинационные схемы. Шифраторы. Комбинационные схемы (КС) — это схемы, у которых выходные сигналы Y= (у1, у2,.... yj) в любой момент дискретного времени однозначно определяются совокупностью входных сигналов X=(x1 х2,..., хп), поступающих в тот же момент времени . Реализуемый в КС способ обработки информации называется комбинационным потому, что результат обработки зависит только от комбинации входных сигналов и формируется сразу же при поступлении входных сигналов. Поэтому одним из достоинств комбинационных схем является их высокое быстродействие. Логические функции и соответствующие им комбинационные схемы подразделяют на регулярные и нерегулярные структуры. Регулярные структуры предполагают построение схемы таким образом, что каждый из ее выходов строится по аналогии с предыдущими. В нерегулярных структурах такая аналогия отсутствует. Шифратор (ШР) решает задачу, обратную схемам ДШ, т. е. по номеру входного сигнала формирует однозначную комбинацию выходных сигналов. \ Таблица истинности шифратора  Логические зависимости шифратора: Y2=x1vx3vx5vx7, Y1=x2vx3vx6vx7, Y0=x4vx5vx6vx7.   Рис. 3.3. Структурная схема шифратора (а) и обозначение дешифратора на принципиальных электрических схемах (б) Комбинационные схемы. Дешифратор. Дешифраторы (ДШ) — это комбинационные схемы с п входами и т = 2n выходами. Единичный сигнал, формирующийся на одном из т выходов, однозначно соответствует комбинации входных сигналов. Например, разработка структуры ДШ для n=3, позволяет получить таблицу истинности (табл. 3.1) и логические зависимости. Таблица истинности дешифратора  Логические зависимости дешифратора:  структурная схема ДШ, построенная в базисе (И, НЕ), и условное ее обозначение на принципиальных электрических схемах ЭВМ. Кружочки у линий, выходящих из логических элементов, указывают на инверсию функций, реализуемых элементами.   Рис. 3.2. Структурная схема дешифратора (а) и обозначение дешифратора на ' принципиальных электрических схемах (б) Комбинационные схемы. Компаратор. Схемы сравнения, или компаратор, обычно строятся как поразрядные. Они широко используются и автономно, и в составе более сложных схем, например при построении сумматоров. Таблица истинности (табл. 3.3) отражает логику работы I-го разряда схемы сравнения при сравнении двух векторов — А и В. На рис. 3.4 показана структурная схема компаратора. Таблица 3.3 Таблица истинности компаратора  Логическая зависимость компаратора: На схеме 3.4, помимо выхода У2, фиксирующего равенство значений разрядов, показаны выходы У1, и У2, соответствующие сигналам «больше» и «меньше».   Рис. 3.4. Структурная схема компаратора (а) и обозначение компаратора на принципиальных электрических схемах (б) Сумматор обеспечивает сложение двух двоичных цифр а, и b\, считая, что переносы из предыдущего разряда не поступают. Этой логике отвечает сложение младших разрядов двоичных чисел. Процесс сложения описывается таблицей истинности и логическими зависимостями (см пред. лекцию)  Схемы с памятью. Более сложным преобразователем информации являются схемы с памятью. Наличие памяти в схеме позволяет запоминать промежуточные состояния обработки и учитывать их значения в дальнейших преобразованиях. Выходные сигналы Y=(yi,y2,...,ym) в схемах данного типа формируются не только по совокупности входных сигналов X = (xl,x2,...,xn), но и по совокупности состояний схем памяти Q = (q},q2,...,qk)- ПРИ этом различают текущий дискретный момент времени tи последующий (t+1) момент времени (рис, 3.8).  Рис. 3.8. Обобщенная структура схемы с памятью Передача значения Qмежду моментами времени tи (t+1) осуществляется обычно с применением двухступенчатой памяти и синхронизирующих импульсов (СИ). В качестве простейшего запоминающего элемента в современных дрМ используют триггеры. В связи с успехами микроэлектроники в схемах основных устройств ЭВМ (процессоров и оперативной памя-ти) перестали применяться в качестве запоминающихся элементов схемы, использующие остаточную намагниченность — ферритовые сердечники. Проблемы развития элементной базы. Одним из главных факторов достижения высокого быстродействия, а значит, и высокой производительности ЭВМ является построение их на новейшей элементной базе. Смена поколений ЭВМ в значительной степени связана с переходами на новые поколения элементной базы, знаменующие достижения новых частотных диапазонов работы схем в рамках доступных технологий. Все современные ЭВМ строятся на микропроцессорных наборах, основу которых составляют большие (БИС) и сверхбольшие интегральные схемы (СБИС). Технологический принцип разработки и производства интегральных схем действует уже более четверти века. Он заключается в послойном изготовлении частей электронных схем по циклу «программа — рисунок — схема». По программам на напыленный фоторезисторный слой наносится рисунок будущего слоя микросхемы. Затем рисунок протравливается, фиксируется, закрепляется и изолируется от новых слоев. На основе этого создается пространственная твердотельная структура. Степень микро-мини-атюризации, размер кристалла ИС, производительность и стоимость технологии напрямую определяются типом литографии. До настоящего времени доминирующей оставалась оптическая литография, т.е. послойные рисунки на фоторезисторе микросхем наносились световым лучом. В настоящее время ведущие компании, производящие микросхемы, реализуют кристаллы с размерами примерно 400—600 мм2 Минимальный топологический размер (толщина линий) при этом составляет 0,25—0,135 мкм. Для сравнения можно привести такой пример. Толщина человеческого волоса составляет примерно 100 мкм. Значит, при таком разрешении на толщине 100 мкм требуется вычерчивать более двухсот линий. Дальнейшие успехи микроэлектроники связываются с электронной (лазерной), ионной и рентгеновской литографией. Это позволяет выйти на размеры 0,13; 0,10 и даже 0,08 мкм. Вместо ранее используемых алюминиевых проводников в микросхемах повсеместно начинают применять медные соединения, что позволяет повысить частоту работы. Такие высокие технологии порождают целый ряд проблем. Микроскопическая толщина линий, сравнимая с диаметром молекул, требует высокой чистоты используемых и напыляемых материалов, применения вакуумных установок и снижения рабочих температур. Новые заводы по производству микросхем представляют собой уникальное оборудование, размещаемое в «чистых помещениях класса 1», микросхемы в которых транспортируются от оборудования к оборудованию в замкнутых сверхчистых мини-атмосферах класса 1000. Мини-атмосфера создается, например, сверхчистым азотом или другим инертным газом при высоком давлении. Уменьшение линейных размеров микросхем и повышение уровня интеграции заставляют проектировщиков искать средства борьбы с потребляемой Wnи рассеиваемой Wpмощностью. При сокращении линейных размеров микросхем в 2 раза, их объемы изменяются в 8 раз. Пропорционально этим цифрам должны меняться и значения Wnи Wp, в противном случае схемы будут перегреваться и выходить из строя. Напряжение питания современных микросхем составляет 3 — 2V. Появились схемы с напряжением питания, близким к 1V, что выходит за рамки принятых стандартов. Дальнейшее понижение напряжения нежелательно, так как всегда в электронных схемах должно быть обеспечено необходимое соотношение «сигнал-шум», гарантирующее устойчивую работу ЭВМ. Протекание тока по микроскопическим проводникам сопряжено с выделением большого количества тепла. Поэтому, создавая сверхбольшие интегральные схемы, проектировщики вынуждены снижать тактовую частоту работы микросхем. Таким образом, переход к конструированию ЭВМ на СБИС и ультра СБИС должен сопровождаться снижением тактовой частоты работы схемы. Дальнейший прогресс в повышении производительности может быть обеспечен либо за счет архитектурных решений, либо за счет новых принципов построения и работы микросхем. Так как микросхемы СБИС не могут работать с высокой тактовой частотой, то в ЭВМ будущих поколений их целесообразно комплексировать в системы. При этом несколько СБИС должны работать параллельно, а слияние работ в системе должно обеспечивать сверхскоростные ИС (ССИС), которые не могут иметь высокую степень интеграции. Внедрение новых технологий производства микропроцессоров испытывает и экономические проблемы. Например, строительство нового завода по производству микросхем с 0,13-микронной технологией обходится от 2 до 4 млрд долл. Это заставляет искать новые альтернативные пути построения будущих ЭВМ. Интенсивные поиски идут по многим направлениям. Наиболее перспективными из них следует считать: • создание молекулярных и биокомпьютеров (нейрокомпьютеров); • разработку квантовых компьютеров; • разработку оптических компьютеров. Общие принципы функциональной и структурной организации ЭВМ. Принципы функционирования ЭВМ могут быть реализованы по-разному: · аппаратными, · программно-аппаратными · программными средствами. При аппаратной и программно-аппаратной реализации могут быть применены: 1. регистры, 2. дешифраторы, 3. сумматоры; 4. блоки жесткого аппаратного управления или микропрограммного с управлением подпрограммами (комплексами микроопераций); 5. устройства или комплексы устройств, реализованные в виде автономных систем (программируемых или с жестким управлением). При программной реализации могут быть применены различные виды программ. Будем считать, что способы реализации функций ЭВМ составляют структурную организацию ЭВМ. Тогда элементная база, функциональные узлы и устройства ЭВМ, программные модули различных видов являются структурными компонентами ЭВМ Организация функционирования ЭВМ с магистральной архитектурой. ЭВМ представляет собой совокупность устройств, выполненных на больших интегральных схемах, каждая из которых имеет свое функциональное назначение. Комплект интегральных схем, из которых состоит ЭВМ, называется микропроцессорным комплектом. В состав микропроцессорных комплектов входят: системный таймер, микропроцес-сор (МП), сопроцессоры, контроллер прерываний, контроллер прямого доступа к памяти, кон-троллеры устройств ввода-вывода. Все устройства ЭВМ делятся на центральные и периферийные. Центральные устройства — полностью электронные, периферийные устройства могут быть либо электронными, либо электромеханическими с электронным управлением. В центральных устройствах основным узлом, связывающим микропроцессорный комплект в единое целое, является системная магистраль. Она состоит из трех узлов, называемых шинами: шина данных (ШД), шина адреса (ША), шина управления (ШУ). Логика работы системной магистрали, количество разрядов (линий) в шинах данных, адре-са и управления, порядок разрешения конфликтных ситуаций, возникающих при одновременном обращении различных устройств ЭВМ к системной магистрали, образуют интерфейс системной шины. В состав центральных устройств ЭВМ входят: центральный процессор, основная память и ряд дополнительных узлов, выполняющих служебные функции: контроллер прерываний, таймер и контроллер прямого доступа к памяти (ПДП). Периферийные устройства делятся на два вида: внешние ЗУ (НМД, НГМД, НМЛ) и устройства ввода-вывода (УВВ): клавиатура, дисплей, принтер, мышь, адаптер каналов связи (КС) и др. Управляющая работой ЭВМ программа перед началом выполнения загружается в основ-ную память (ОП). Адрес первой выполняемой команды передается микропроцессору и запомина-ется в счетчике команд. Начало работы процессора заключается в том, что адрес из счетчика команд выставляется на шину адреса системной магистрали. Одновременно на шину управления выдается команда «Выборка из ОП», которая воспри-нимается основной памятью. Получив с шины управления системной магистрали команду, основная память считывает адрес с шины адреса, находит ячейку с этим номером и ее содержимое выставляет на шину дан-ных, а на шину управления выставляет сигнал о выполнении команды. Процессор, получив по шине управления сигнал об окончании работы ОП, вводит число с шины данных на внутреннюю магистраль МП и через нее пересылает введенную информацию в Регистр команд. В регистре команд полученная команда разделяется на кодовую и адресную части. Код команды поступает в блок управления для выработки сигналов, настраивающих МП на выполнение заданной операции и для определения адреса следующей команды (который сразу за-носится в счетчик команд). Адресная часть команды выставляется на шину адреса системной магистрали (СМ) и со-провождается сигналом «Выборка из ОП» на шине управления. Результат выполнения операции выставляется микропроцессором на шину данных, на ши-ну адреса выставляется адрес ОП, по которому этот результат необходимо записать, а на шину управления выставляется команда «Запись в ОП». Процессор, получив этот сигнал о выполнении операции, начинает выборку очередной ко-манды: выставляет адрес из счетчика команд на шину адреса, формирует команду «Выборка из ОП» на шине управления и т.д. В каждом цикле, получив команду в регистр команд и выделив код операции, процессор определяет, к какому устройству она относится. Если команда должна выполняться процессором, организуется ее выполнение по описанному циклу. Если же команда предназначена для выполне-ния в другом устройстве ЭВМ, ЦП передает ее соответствующему устройству. Взаимодействие МП с внешними устройствами предусматривает выполнение логической последовательности действий, связанных с поиском устройства, определением его технического состояния, обменом командами и информацией. Эта логическая последовательность действий вместе с устройствами, реализующими ее, получила название интерфейс ввода-вывода. В IBM PC есть два стандартных интерфейса для связи ЦП с внешними устройствами: па-раллельный (типа Centronics) и последовательный (типа RS-232). Если при обращении ЦП к внешнему устройству продолжение выполнения основной про-граммы центральным процессором возможно только после завершения операции ввода-вывода, то ЦП, запустив внешнее устройство, переходит в состояние ожидания. Такой режим работы получил название однопрограммного — в каждый момент времени все устройства находятся в состоянии ожидания, и только одно устройство выполняет основную (и единственную) программу. Для ликвидации таких простоев внешние устройства сделаны автономными: получив от ЦП необходимую информацию, они самостоятельно организуют свою работу по обмену данными. Такой режим работы ЭВМ называется многопрограммным. Организация работы ЭВМ при выполнении задания пользователя. Организация процессов ввода, преобразования и отображения результатов относится к сфере системного программного обеспечения. Это сложные процессы, которые чаще всего делаются «прозрачными», т.е. незаметны-ми для пользователя. Один из них — реализация задания пользователя: профессиональный пользователь (программист) пишет задание для ЭВМ в виде программы на алгоритмическом языке. Напи-санное задание (программа) представляет собой исходный модуль, сопровождаемый управля-ющими предложениями, указывающими операционной системе ЭВМ, на каком языке написа-на программа и что с ней надо делать. Исходный модуль перед исполнением должен быть переведен на внутренний язык ма-шины. Эта операция выполняется специальной программой — транслятором. Трансляторы выполняются в виде двух разновидностей: интерпретаторы и компи-ляторы. Интерпретатор после перевода на язык машины каждого оператора алгоритмического языка немедленно исполняет полученную машинную программу. Компилятор же сначала полностью переводит всю программу, представленную ему в виде исходного модуля (ИМ), на язык машины. Получаемая при этом машинная программа представля-ет собой объектный модуль (ОМ). Результат работы компилятора может быть записан в библио-теку объектных модулей (БОМ) или передан другим программам для дальнейшей обработки, по-скольку полученная машинная программа не готова к исполнению по двум причинам. * Во-первых, она содержит неразрешенные внешние ссылки (т.е. обращение к про-граммам, которые не содержатся в исходном модуле» но необходимы для работы основной программы, например к стандартным программам алгоритмического язы-ка, таким, как извлечь ние корня квадратного, вычисление тригонометрических функций и т.д.). * Во-вторых, объектный модуль представляет собой машинную программу в услов-ных адресах — каждый объектный модуль начинается с адреса Oh, тогда как для исполнения программа должна быть «привязана» к конкретным физическим адре-сам основной памяти. Недостающие программы должны быть взяты из библиотек компилятора (которые могут быть написаны в виде исходных либо в виде объектных модулей) и добавлены к основной про-грамме. Эту операцию выполняет редактор связей. В результате работы редактора связей образу-ется загрузочный модуль (ЗМ), который помещается в соответствующую библиотеку программ (БЗМ). В загрузочном модуле все ссылки разрешены, т.е. он содержит все необходимые стандарт-ные программы, но привязки к памяти у загрузочного модуля нет. Привязка к памяти загрузочного модуля производится программой выборки, которая пере-носит загрузочный модуль из библиотеки загрузочных модулей (обычно хранящейся на магнит-ном носителе) в основную память, и инициирует его выполнение. Если программа только отлаживается, то получение загрузочного модуля и обращение к программе выборки будут лишними операциями. В этом случае применяется загрузчик — про-грамма, сочетающая в себе функции редактирования связей и загрузки полученной машинной программы в основную память для исполнения. Особенности управления основной памятью ЭВМ. Алгоритмы распределения, использования, освобождения ресурсов и представления к ним доступа предназначены для наиболее эффективной организации работы всего комплекса устройств ЭВМ. Рассмотрим их на примере управления основной памятью. Для выполнения программы при ее загрузке в основную память ей выделяется часть машинных ресурсов — они необходимы для размещения команд, данных, управляющих таблиц и областей ввода-вывода, т.е. производится трансляция адресного пространства откомпилированной про-граммы в местоположение в реальной памяти. Выделение ресурсов может быть осуществлено самим программистом (особенно, если он работает на языке, близким к машинному)» но может производиться и операционной системой. Если выделение ресурсов производится перед выполнением программы, такой процесс называется статическим перемещением, в результате которого программа «привязывается» к определенному месту в памяти ЭВМ. Если же ресурсы выделяются в процессе выполнения программы, это называется динами-ческим перемещением, и в этом случае программа не привязана к определенному месту в реальной памяти. Динамический режим можно реализовать только с помощью операционной системы. При статическом перемещении могут встретиться два случая: * Реальная память больше требуемого адресного пространства программы. В этом случае загрузка программы в реальную память производится, начиная с 0-го адреса (рис. 4.2). Загружаемая программа является абсолютной программой, так как ника-кого изменения адресов в адресном пространстве, подготовленном компилятором, при загрузке в основную память не происходит. * Реальная память меньше требуемого адресного пространства программы (рис. 4.3). В этом случае программист (или операционная система) вынужден решать пробле-му, как организовать выполнение программы. Методов решения проблемы суще-ствует несколько: можно создать оверлейную структуру (т.е. разбить программу на части, вызываемые в ОП по мере необходимости), сделать модули программы реен-терабельными (т.е. допускающими одновременную работу модуля по нескольким обращениям из разных частей программы или из различных программ). При работе в мультипрограммном режиме может сложиться ситуация, когда между про-граммами образуются незанятые участки памяти. Общий объем незанятой памяти, составляющий 50 Кбайт, достаточен, чтобы загрузить программу, находящуюся в ожидании. Но ее не удается загрузить, так как свободные участки памяти не являются смежными. Та-кое состояние называется фрагментацией реальной памяти. Оно характерно для систем со стати-ческим перемещением. В системах с динамическим перемещением программ перемещающий загрузчик размещает программу в свободной части памяти и допускает использование ее несмежных участков. Виртуальная память. Виртуальная память - это использование вторичного хранилища в качестве дополнительной первичной памяти. В этом случае программист работает так, как будто ему предоставлена реальная память максимально допустимого для данной ЭВМ объема, хотя имеющаяся реальная память значительно меньше по объему. Такой режим работы называется режимом виртуальной памяти. Теоретически доступная пользователю основная память, объем которой определяется только разрядностью адресной части команды и которая не существует в действительности, называется виртуальной памятью. Загрузить программу в виртуальную память — значит переписать несколько программных страниц из внешней страничной памяти в основную память. Если в процессе выполнения программы система обнаружит, что требуемой страницы нет в реальной памяти, она должна переслать копию этой страницы из внешней страничной памяти в реальную память. Этот механизм называется принудительным страничным обменом. Система прерываний ЭВМ. Прерывание - это механизм, с помощью которого такие модули, как ввод-вывод или память, могут прерывать нормальную обработку процессором. Для того чтобы ЦП, выполняя свою работу, имел возможность реагировать на события, происходящие вне его зоны внимания, и наступления которых он «не ожидает», существует система прерываний ЭВМ. В зависимости от места нахождения источника прерываний они могут быть разделены на: внутренние (программные и аппаратные) и внешние прерывания (поступающие в ЭВМ от внешних источников, например от клавиатуры или модема). Совокупность значений наиболее существенных информационных элементов называется вектором состояния или словом состояний процессора Каждое событие, требующее прерывания, сопровождается специальным сигналом, который называется запросом прерывания. Программа, затребованная запросом прерывания, называется обработчиком прерывания. Аппаратные прерывания вырабатываются устройствами, требующими внимания микропроцессора: Запросы на логические прерывания вырабатываются внутри микропроцессора при появлении «нештатных» ситуаций: Запрос на программное прерывание формируется по команде «INT n», где n — номер вызываемого прерывания. Запрос на аппаратное или логическое прерывание вырабатывается в виде специального электрического сигнала. Центральные устройства ЭВМ. Основная память. Основная память (ОП) содержит оперативное (RAM — Random Access Memory) и постоянное (ROM — Read Only Memory) запоминающие устройства. Оперативное запоминающее устройство (ОЗУ) предназначено для хранения информации (программ и данных), непосредственно участвующей в вычислительном процессе в текущий интервал времени. ОЗУ — энергозависимая память: при отключении напряжения питания информация, хранящаяся в ней, теряется. Основу ОЗУ составляют микросхемы динамической памяти DRAM. Это большие интегральные схемы, содержащие матрицы полупроводниковых запоминающих элементов - полупроводниковых конденсаторов, наличие заряда в конденсаторе обычно означает «1», отсутствие заряда- «О». Конструктивно элементы от оперативной памяти выполняются в виде отдельных модулей памяти - небольших плат с напаянными на них одной или, чаще, несколькими микросхемами. Эти модули вставляются в разъемы - слоты на системной плате. На материнской плате может быть несколько групп разъемов (банков) для установки модулей памяти; в один банк можно ставить только блоки одинаковой емкости; блоки разной емкости можно устанавливать в разных банках. Модули памяти характеризуются конструктивом, емкостью, временем обращения и надежностью работы. Важным параметром модуля памяти является его надежность и устойчивость к возможным сбоям. Модули памяти бывают с контролем четности (parity) и без контроля четности (поп parity) хранимых бит данных. Существуют следующие типы модулей оперативной памяти: · DIP; · SIP; · SIMM; · DIMM; · RIMM. Динамическое ОЗУ. Центральные устройства ЭВМ. Динамическое ОЗУ. Что означает DRAM? DRAM расшифровывается как “динамическая оперативная память”, и это особый тип оперативной памяти (оперативная память). Все компьютеры имеют оперативную память, и DRAM - это один из видов оперативной памяти, который мы видим в современных настольных компьютерах и ноутбуках. DRAM была изобретена в 1968 году Робертом Деннардом и выпущена на рынок Intel® в 70-х годах. Что делает DRAM? Все типы оперативной памяти, включая DRAM, представляют собой энергозависимую память, которая хранит биты данных на транзисторах. Эта память также расположена ближе к вашему процессору, поэтому ваш компьютер может легко и быстро получить к ней доступ для всех выполняемых вами процессов. Когда вы используете свой компьютер, он должен вызывать данные и программный код для обработки процессором. Оперативная память позволяет компьютеру использовать, перезаписывать и временно сохранять эти данные и код в режиме реального времени. Однако, поскольку для работы транзисторов требуется электричество, все, что хранится здесь, исчезает, когда вы выключаете компьютер. Вот почему он считается “изменчивым”. Типы DRAM Память DRAM - это всего лишь один из видов оперативной памяти. И в категории DRAM есть несколько типов, которые нужно знать. 1. SDRAM-ПАМЯТЬ Синхронный DRAM, или SDRAM, повышает производительность благодаря своим выводам, которые синхронизируются с соединением для передачи данных между основной памятью и микропроцессором. Компьютеры используют эту функцию синхронизации с середины 1990-х годов. 2. Память DDR SDRAM DDR SDRAM обладает функциями SDRAM, но с удвоенной частотой передачи данных. Вот почему он называется “SDRAM с двойной скоростью передачи данных”. 3. ECC DRAM-ПАМЯТЬ Этот тип DRAM может находить поврежденные данные, а иногда даже исправлять их, благодаря своему коду исправления ошибок (ECC). Центральные устройства ЭВМ. Принципы организации основной памяти в современных компьютерах. Основная память представляет собой следующий уровень иерархии памяти. Основная память удовлетворяет запросы кэш-памяти и служит в качестве интерфейса ввода/вывода, поскольку является местом назначения для ввода и источником для вывода. Для оценки производительности основной памяти используются два основных параметра: задержка и полоса пропускания. Традиционно задержка основной памяти имеет отношение к кэш-памяти, а полоса пропускания или пропускная способность относится к вводу/выводу. В связи с ростом популярности кэш-памяти второго уровня и увеличением размеров блоков у такой кэш-памяти, полоса пропускания основной памяти становится важной также и для кэш-памяти. Задержка памяти традиционно оценивается двумя параметрами: временем доступа (access time) и длительностью цикла памяти (cycle time). Время доступа представляет собой промежуток времени между выдачей запроса на чтение и моментом поступления запрошенного слова из памяти. Длительность цикла памяти определяется минимальным временем между двумя последовательными обращениями к памяти. Основная память современных компьютеров реализуется на микросхемах статических и динамических ЗУПВ (Запоминающее Устройство с Произвольной Выборкой). Микросхемы статических ЗУВП (СЗУПВ) имеют меньшее время доступа и не требуют циклов регенерации. Микросхемы динамических ЗУПВ (ДЗУПВ) характеризуются большей емкостью и меньшей стоимостью, но требуют схем регенерации и имеют значительно большее время доступа. Увеличение разрядности основной памятиКэш-память первого уровня во многих случаях имеет физическую ширину шин данных соответствующую количеству разрядов в слове, поскольку большинство компьютеров выполняют обращения именно к этой единице информации. В системах без кэш-памяти второго уровня ширина шин данных основной памяти часто соответствует ширине шин данных кэш-памяти. Удвоение или учетверение ширины шин кэш-памяти и основной памяти удваивает или учетверяет соответственно полосу пропускания системы памяти. Реализация более широких шин вызывает необходимость мультиплексирования данных между кэш-памятью и процессором, поскольку основной единицей обработки данных в процессоре все еще остается слово. Память с расслоением. Наличие в системе множества микросхем памяти позволяет использовать потенциальный параллелизм, заложенный в такой организации. Для этого микросхемы памяти часто объединяются в банки или модули, содержащие фиксированное число слов, причем только к одному из этих слов банка возможно обращение в каждый момент времени. Как уже отмечалось, в реальных системах имеющаяся скорость доступа к таким банкам памяти редко оказывается достаточной. Следовательно, чтобы получить большую скорость доступа, нужно осуществлять одновременный доступ ко многим банкам памяти. Одна из общих методик, используемых для этого, называется расслоением памяти.Обобщением идеи расслоения памяти является возможность реализации нескольких независимых обращений, когда несколько контроллеров памяти позволяют банкам памяти (или группам расслоенных банков памяти) работать независимо. Использование специфических свойств динамических ЗУПВКак упоминалось раньше, обращение к ДЗУПВ состоит из двух этапов: обращения к строке и обращения к столбцу. При этом внутри микросхемы осуществляется буферизация битов строки, прежде чем происходит обращение к столбцу. Размер строки обычно является корнем квадратным от емкости кристалла памяти: 1024 бита для 1Мбит, 2048 бит для 4 Мбит и т.д. С целью увеличения производительности все современные микросхемы памяти обеспечивают возможность подачи сигналов синхронизации, которые позволяют выполнять последовательные обращения к буферу без дополнительного времени обращения к строке. Имеются три способа подобной оптимизации: блочный режим (nibble mode) - ДЗУВП может обеспечить выдачу четырех последовательных ячеек для каждого сигнала RAS. страничный режим (page mode) - Буфер работает как статическое ЗУПВ; при изменении адреса столбца возможен доступ к произвольным битам в буфере до тех пор, пока не поступит новое обращение к строке или не наступит время регенерации. режим статического столбца (static column) - Очень похож на страничный режим за исключением того, что не обязательно переключать строб адреса столбца каждый раз для изменения адреса столбца. Центральные устройства ЭВМ. Постоянное запоминающее устройство. Кроме оперативной памяти, под термином "память" мы будем подразумевать постоянную и CMOS - память. К постоянной памяти относят постоянное запоминающее устройство, ПЗУ (в англоязычной литературе - Read Only Memory, ROM, что дословно перводится как "память только для чтения"), перепрограммируемое ПЗУ, ППЗУ (в англоязычной литературе – Programmable Read Only Memory, PROM), и флэш-память (flash memory). Название ПЗУ говорит само за себя. Информация в ПЗУ записывается на заводе-изготовителе микросхем памяти, и в дальнейшем изменить ее значение нельзя. В ПЗУ хранится критически важная для компьютера информация, которая не зависит от выбора операционной системы. Программируемое ПЗУ отличается от обычного тем, что информация на этой микросхеме может стираться специальными методами (например, лучами ультрафиолета), после чего пользователь может повторно записать на нее информацию. Эту информацию будет невозможно удалить до следующей операции стирания информации. |