Лекции_Вычислительные машины_new. Лекция История развития вычислительной техники

Скачать 5.16 Mb. Скачать 5.16 Mb.

|

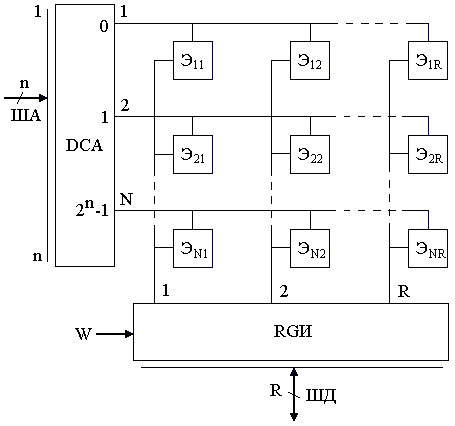

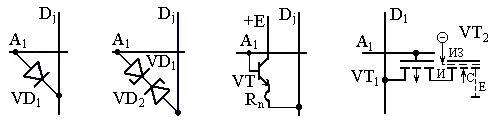

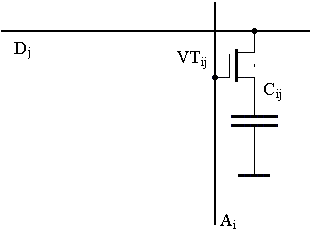

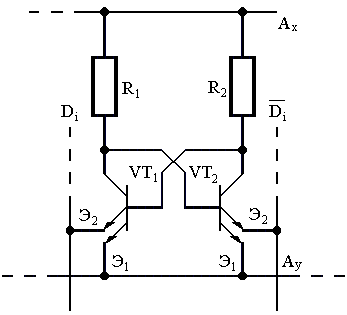

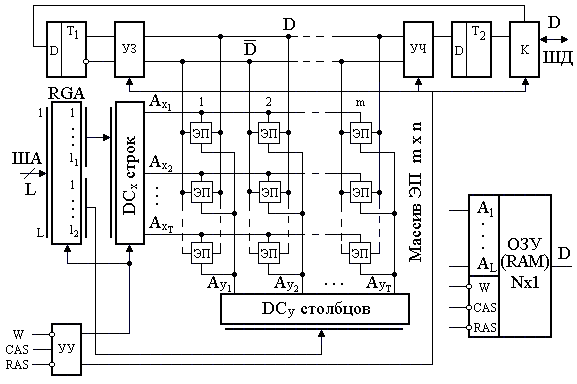

ТЕМА 5. Организация памяти в ЭВМЛекция 12: Классификация и параметры запоминающих устройств Запоминающие устройства (ЗУ) предназначены для записи, хранения и выдачи информации в ЭВМ. Они позволяют сохранять (фиксировать) данные, промежуточные вычисления, константы, коды команд. Фиксация предполагает запись информации в ЗУ, после чего она там хранится, а при необходимости по запросам извлекается или считывается, т.е. осуществляется чтение ЗУ. Сохраняемая в ЗУ информация кодируется в 2 СС одинарными, двойными, счетверенными словами или байтами. Каждый байт содержит 8 бит. Бит – наименьшая емкость двоичной памяти, способной хранить только «0» или «1». В слове можно разместить 2 байта, двойное слово содержит 4 байта, счетверенное – 8 байт. Все ЗУ разбивается на отдельные ячейки. Каждая ячейка имеет возможность (доступ) осуществлять запись, хранение и считывание информации величиной, равной ее разрядности, за одно обращение. По способам поиска информации различают адресные и ассоциативные ЗУ. В адресных ЗУ каждая ячейка имеет свой номер – адрес, по которому осуществляется обращение к ней. В ассоциативных ЗУ поиск ячейки ведется по некоторым закодированным признакам – запросам, т.е. «по содержанию». Таким признаком может быть, например, содержание части разрядов любой ячейки, передаваемой в ЗУ как ключ для обнаружения тех ячеек, где он имеется [12]. Адресные ЗУ для поиска одной искомой ячейки используют дешифраторы. Ассоциативные осуществляют поиск по всему массиву ЗУ схемами сравнения. По способу доступа к отдельным ячейкам ЗУ различают: - с последовательным доступом, при котором информация как записывается, так и считывается последовательно (ЗУ на магнитных лентах, перфолентах, линиях задержки, CD-ROM); - с циклическим доступом, при котором место чтения или записи периодически повторяется (НГМД, НЖМД, магнитные барабаны); - с произвольным (прямым) доступом, при котором чтение и запись могут осуществляться в любой момент времени в любую ячейку (ПЗУ, ППЗУ, ОЗУ и кэш). По способу хранения и возможности записи информации различают: - ПЗУ – постоянные ЗУ с неизменяющейся в процессе всей эксплуатации информацией; - ППЗУ – полупостоянные ЗУ с возможностью многократного перепрограммирования содержания ячеек; - ОЗУ – оперативные ЗУ с обменом в режиме записи / считывания по запросу системной шины; - СОЗУ – сверхоперативные ЗУ – регистровая память на триггерах с высоким быстродействием. По типу используемых элементов памяти ЗУ классифицируются на полупроводниковые, магнитные и оптические. По внутренней организации ЗУ бывают: - 2D – в 2 измерениях, когда массив памяти имеет N ячеек и адресных шин. Каждая ячейка возбуждается одной своей адресной шиной, а каждый разряд подключен к своей информационной шине; - 3D – «куб памяти» – память в трех измерениях, в которой имеется по оси Х и Y адресные шины и два дешифратора DCX и DCY, каждый разряд представляет собой однобитный массив памяти, подключенный к своей информационной шине; - 2.5 D – по структуре эта память является промежуточной между 2D и 3D, имеет один DCX, а число DCY равно числу разрядов. Каждый разряд размещается в своем массиве, подключенном к одной информационной шине. Основными параметрами ЗУ является емкость, быстродействие и стоимость. Емкость ЗУ выражается в битах, байтах, килобайтах (Кб), мегабайтах (Мб), гигабайтах (Гб) и терабайтах (Тб). Быстродействие ЗУ определяется временем считывания данных в цикле чтения tЦЧ и временем передачи в цикле записи tЦЗ. В общем виде tЦЧ, tЦЗ можно вычислить по формулам: tЦЗ = tП + tС + tЗ; tЦЧ = tП + tЧ + tР, где tП – время, затрачиваемое в ЗУ на поиск ячейки; tС – время стирания предыдущей информации, если она может исказить записываемую; tЗ – время записи данных в ячейку; tЧ – время извлечения информации на ШД; tР – время регенерации данных (подзарядка конденсаторов в DRAM). Промежуток времени от начала обращения к ЗУ до момента появления нужной информации на ШД называется временем выборки и определяется по формуле: tВ = tП + tЧ. Быстродействие ЗУ измеряется в наносекундах (1нс = 10-9 с), микросекундах (1мкс = 10-6 с) или миллисекундах (1мс = 10-3 с). Стоимость ЗУ (С) чаще всего оценивается приведенной стоимостью (СП), которая определяется из выражения: Сп = С / V (руб/бит). Величина приведенной стоимости используется для выбора наиболее дешевой памяти, для комплектации или проектирования ЭВМ. Для новых ЗУ характерно постоянное увеличение быстродействия, емкости V и уменьшение СП. 2. Постоянные и полупостоянные запоминающие устройства Постоянные и полупостоянные ЗУ используются в ЭВМ как долговременная память для хранения констант, программ BIOS, POST, конфигурации ЭВМ и параметров устройств. ПЗУ и ППЗУ (флэш-память) могут строиться по структуре 2D емкостью до нескольких десятков Кб по схеме [1], показанной на рис. 3.1. При подаче двоичного кода физического адреса <ФА (1,n)> на ША и сигнала чтения дешифратором адреса DCA возбуждается одна из адресных (горизонтальных) шин Ai с номером i{1, 2,...,N}, равным адресу ячейки. Шина Ai «подключает» элементы памяти Эi1, Эi2, ..., ЭiR к информационным (вертикальным) шинам массива {Эi,j}. Если j‑й элемент памяти хранит «1», то он возбуждает вертикальную шину Dj и устанавливает в «1» j-й разряд информационного регистра RGИ (j) = 1. Если он хранит «0», то j-й разряд RGИ обнуляется. С появлением сигнала чтения W = 1 содержимое регистра передается на шину данных, т.е. выполняется микрооперация ШД (1,R) = RGИ (1,R).  RGИ R R n N n Э11 Э12 Э1R1 Э21 Э22 Э2R ЭNR ЭN2 ЭN1 n W Рис. 3.1. Схема ЗУ типа 2D Режим чтения характерен для ПЗУ, элементы памяти которого не изменяют своего состояния в процессе эксплуатации и программируются один раз. Наиболее просто программирование можно осуществить распайкой диодов (рис. 3.2, а). Наличие диода VD1 между шинами Ai и Dj создает однонаправленную гальваническую связь от Ai к Dj и кодируется как «1» в j‑м разряде i-й ячейки. Отсутствие диода (разрыв связи) программируется как «0». Недостатком способа ручной распайки является значительная трудоемкость «программирования», и поэтому он уже нигде не применяется. Для автоматизации «прошивки» ПЗУ используются элементы памяти, показанные на рис. 3.2, б, в. Эти элементы при изготовлении ИС имеются на всех пересечениях адресных и информационных шин. В процессе программирования на адресной шине Ai и информационных шинах Dj последовательно устанавливается такое напряжение, когда пробивается и закорачивается один из стабилитронов (состояние логической «1») или сгорает, образуя разрыв, плавкая перемычка Rn (состояние «0»). Режим программирования путем пережигания плавких перемычек используется в ИС серии К 556 РТ, где, например, К 556 РТ5 имеет емкость 4096 бит с организацией N R = 512 8 и временем выборки 70 нс.  а б в г Рис. 3.2. Элементы памяти ПЗУ и ППЗУ: а – диодное ПЗУ, б – ПЗУ на стабилитронах, в – ПЗУ с плавкими перемычками, г – ПЗУ на транзисторах с изолированным затвором Отличие ИС ППЗУ от ПЗУ заключается в том, что они позволяют изменять в процессе эксплуатации состояния элементов памяти от нескольких десятков до нескольких тысяч раз, а в новых БИС от 100 тысяч до 1 млн циклов перезаписи. Программирование осуществляется занесением объемного заряда электронов (-) в область плавающего затвора диэлектрика, находящуюся около изолированного затвора ИЗ. Этот процесс можно пояснить с помощью рис. 3.2, г. При подаче высокого напряжения Е к p-n переходу стока (С) либо истока (И) происходит инжекция электронов в область плавающего затвора. После снятия потенциала Е этот заряд из-за отсутствия проводимости в диэлектрике остается длительное время и притягивает дырки, создавая проводящим слой между И-С. При отсутствии заряда связи между И-С не будет. Если после программирования все стоки транзисторов VT2 подключить к нулевому потенциалу (), то с возбуждением шины Ai транзисторы VT1 откроются и передадут состояние (потенциал) истока транзисторов VT2 (при наличии заряда на Dj будет «0», при отсутствии заряда – «1»). Для повторного программирования ППЗУ стирание зарядов осуществляется либо электрически (ИС КР 558 РР), подачей высоких напряжений обратной полярности, либо ультрафиолетовым облучением диэлектрика ИС через кварцевую крышку в корпусе (ИС КР 573 РФ). Процесс электрического стирания вызывает значительный ток от утекания заряда из области плавающего затвора под действием повышенного обратного напряжения более 10 В. Чтобы кристалл не разогревался выше допустимой температуры, ток ограничивают уменьшая число одновременно стираемых ячеек. Основной причиной ограничения числа циклов перезаписи и уменьшения времени эксплуатации ППЗУ является аккумулируемый после каждой перезаписи износ плавающего затвора транзистора, который происходит от многократного воздействия повышенного напряжения более 10 В при стирании информации. При этом происходит нарушение оксидного слоя либо накопление электронов в плавающем затворе. Стирание информации выполняют в несколько циклов. При этом переходы И-С всех транзисторов VT2 становятся непроводящими и все ячейки содержат «1». Перепрограммирование ИС ведется последовательно отдельно для каждой ячейки. Сначала передается ее адрес, затем передается код записываемых данных в RGИ (1, R). Затем возбуждается шина Е в разрядах, где кодируется «0», и пропускаются информационные разряды, где кодируются «1». Так как накопление заряда идет медленно, запись осуществляется циклами. Длительность каждого цикла около 0.5 мс, число циклов (около 100) определяется необходимым временем занесения заряда в ИС. Принцип с ультрафиолетовым стиранием и электрической записью информации используется в ИС КР 573 РФ2 емкостью 2 Кб (N R = 2048 8 (бит)) с временем выборки 0.9 мкс, временем хранения заряда 104 час и возможностью до 10 раз перезаписи данных. Функционально ППЗУ (ПЗУ) представляет собой шифратор, который преобразует унитарный код с адресной шины в позиционный, подключаемый к информационной шине. В зависимости от способа объединения элементов памяти, показанных на рис. 3.2, г, шифратор может реализовываться на схемах И – НЕ или ИЛИ – НЕ (Dj = (А1х1j VА2х2j V...V АNxNj), j=1, R; где хij – содержимое j-го разряда, i‑й ячейки). Схемы ИЛИ – НЕ обеспечивают высокое быстродействие, но имеют меньшую емкость, чем ППЗУ на И – НЕ. 3. Оперативные запоминающие устройства Для построения ОЗУ большой емкости используются элементы статической или динамической памяти, которые строятся на простейших элементах транзисторно-транзисторной логики (ТТЛ), инжекционной логики (И2Л), эмиттерносвязной логики (ЭСЛ) и других технологий [5]. В основе динамических ОЗУ (DRAM) используется заряд межэлектродных конденсаторов Cij емкостью менее 0.1 пФ и током заряда менее 10-10 А. Схема i-го разряда ячейки памяти динамического ОЗУ (DRAM) представлена на рис. 3.3. Для записи логической “1” в элемент памяти активизируются информационная шина Dj и адресная шина Аi. При этом униполярный (полевой) транзистор открывается и через него конденсатор Cij заряжается. При отсутствии открывающего напряжения на шине Аi транзистор закрыт, конденсатор Cij заряжен и хранит информацию. При подаче напряжения чтения на шину Аi транзистор VTij открывается и напряжение конденсатора Cij подается на шину Dj, и он разряжается. Ток разряда Cij усиливается и фиксируется в информационном регистре ОЗУ.  Dj VTij Cij Ai Рис. 3.3. Элемент динамического ОЗУ Для устранения искажений информации в результате утечки заряда с конденсатора элементы памяти периодически, через 2 мс или более, в зависимости от типа ИС, необходимо перезаряжать в цикле регенерации. Преимуществом динамических ОЗУ является высокая степень интеграции элементов памяти и малая потребляемая мощность. Недостатком их является большое время доступа 50-70 нс по сравнению со статической памятью, где оно равно менее 15 нс. Статическая оперативная память (SRAM) строится на быстродействующих биполярных транзисторах, например, двухэмиттерных транзисторах TTL (рис. 3.4). В режиме хранения информации между шинами Аx и Аy поддерживается минимальное напряжение (около 0.2 В), сохраняя один из транзисторов открытым (логический “0”), другой закрытым (логическая “1”). На обоих проводах информационной парафазной шины (  Рис. 3.4. Элемент статического ОЗУ В режиме чтения информации шины Аx и Аy возбуждаются и на них подаются потенциалы, обеспечивающие быстрое чтение разных токов, поступающих с эмиттеров Э2 на провода в усилитель чтения. В зависимости от величины токов в проводах, после их усиления триггер Т2 (см. рис. 3.5, а) информационного регистра ОЗУ устанавливается в “1” или “0”. При этом состояние ЭП не изменяется и он может быть переведен в режим хранения предыдущего состояния. Для записи информации в бистабильный ЭП возбуждаются адресные шины Аx и Аy и соответствующий один провод На статических и динамических ЭП изготавливают ИС различной емкости и разрядности. На рис. 3.5, б приведена типичная ИС емкостью N = 2L = m n (бит). Массив ЭП состоит из n строк и m столбцов. Каждый ЭП хранит один бит информации.  а б Рис. 3.5. Структура ИС ОЗУ: а – 1- битная схема ОЗУ, б – обобщенная схема ОЗУ Адрес ЭП, участвующего в операции чтения /записи, определяется L-разрядным двоичным кодом, поступающим с шины адреса ША в регистр адреса RGA. Младшие l1 разряда адреса в режиме чтения или записи информации в ОЗУ с появлением сигнала выборки строки RAS поступают на дешифратор строк DCx. Старшие l2 разряда адреса с появлением сигнала выборки столбца CAS поступают на дешифратор столбцов DCy. В соответствии с двоичным кодом адреса каждый из дешифраторов возбуждает только одну выходную шину. На пересечении возбужденных шин Аx и Аy соответствующий ЭП подключается к внутренней информационной парафазной шине В режиме записи (W=0, CAS=0, RAS=0) УУ включает усилитель записи (УЗ) и подсоединяет его к шине В режиме чтения (W=1, RAS=0, CAS=0) УУ отключает УЗ от шины При хранении информации (CAS=RAS=1) коммутатор К отключает от ШД ОЗУ. На всех шинах Аx, Аy, |