Лекции_Вычислительные машины_new. Лекция История развития вычислительной техники

Скачать 5.16 Mb. Скачать 5.16 Mb.

|

|

4. Характеристики обмена и типы оперативной памяти Оперативная память постоянно используется МП в процессе решения задач, предоставляя ему коды команд, данные и адреса операндов и устройств. Основными характеристиками ОЗУ является быстродействие и емкость памяти. Чем быстрее протекает обмен между ОЗУ и МП, тем скорее ЭВМ вычисляет. Этот обмен может происходить в цикле записи или цикле чтения данных. Цикл записи состоит из следующих микроопераций: - передача адреса ячейки из МП по ША в регистр адреса ОЗУ (время выполнения микрооперации равно tA); - передача операнда из МП по ШД в информационный регистр ОЗУ (tИ); - дешифрация адреса в ОЗУ, возбуждение и стирание содержимого ячейки памяти (tД); - запись из информационного регистра в ячейку памяти (tЗ). ИС памяти обычно имеют меньшее число выводов, как показано в табл. 3.1, чем разрядность ШД или ША. Поэтому часто одни и те же адресные входы в них используются для передачи адресов строк в старшие разряды регистра адреса под управлением сигнала RAS (время tAR) и для передачи адресов столбцов элементов памяти в младшие разряды регистра адреса под управлением сигнала CAS (время tAC). В таких ИС n-разрядный физический адрес ФА (1, n) разбивается на адрес строки (страницы) АR (1, nR) и адрес столбца (ячейки внутри страницы) АС (1, nC) таким образом, чтобы выполнялось условие ФА (1, n) = <<AR (1, nR)>, <AC (1, nC)>>. Тогда передача двоичных кодов <АR (1, nR)> и <АС (1, nC)> осуществляется последовательно, т. е. путем мультиплексирования адресов строки и столбца. При отсутствии средств параллельного выполнения микроопераций время, требуемое на осуществление цикла записи, может быть вычислено по формуле: tЦЗ = tAR + tAC + tД + tИ + tЗ. и составлять длительность, с учетом ожидания выполнения более длительных из них, до 5 и более периодов (тактов) работы генератора, синхронизирующего обмен по ШД. Обычно коды <АR (1, nR)> и <АС (1, nC)> передаются по одной и той же шине, тогда tAR = tAC = tA. Сумма tД + tИ + tЗ уменьшается несколькими способами: - передача данных и адреса выполняется параллельно по разным шинам (tИ = 0); - используется режим чередования памяти, когда передача осуществляется поочередно в две ячейки памяти, находящиеся в разных ИС, что приводит к параллельному выполнению в двух ячейках микроопераций стирания и записи, тогда tД = 0 или tÇ = 0; - осуществляется запись в несколько ближайших ячеек, т. е. используется способ разбивки памяти на страницы и режим пакетной или страничной передачи (tAC = 0 или tAR = 0); - улучшается технология, с применением которой уменьшается время стирания и записи в динамических ОЗУ. В идеальном случае при использовании всех способов параллельного выполнения микроопераций время, необходимое на запись в 4 ячейки памяти, может занимать 5 тактов работы генератора, что соответствует схеме: 2 – 1 – 1 – 1. В первых двух тактах передается адрес строки, а затем адрес столбца и операнд. В следующих трех происходит передача на запись еще трех кодов пакета без изменения адреса строки. Цикл чтения включает микрооперации: - передача из МП адреса ячейки памяти в регистр адреса ОЗУ; - дешифрация адреса, возбуждение и чтение содержимого ячейки памяти в информационный регистр ОЗУ (tД1); - передача данных по ШД в МП (tИ1); - регенерация данных, т. е. восстановление искаженного в результате чтения содержимого ячейки путем записи в нее данных из информационного регистра (tЗ). Время, затрачиваемое на цикл чтения, можно вычислить по формуле: tЦЧ = tAR + tAC + tД1 + tИ1 + tЗ. Обычно tД = tД1, а tИ = tИ1, и время, затрачиваемое на циклы чтения и записи при обмене одним операндом, в DRAM почти одинаковое. В SRAM отсутствует режим регенерации информации в цикле чтения (tЗ = 0) и стирание информации в цикле записи данных в ячейку (tД = 0). Наибольшее время, затрачиваемое на циклы чтения и записи информации, определяет быстродействие ИС ОЗУ, которое накладывает ограничение на частоту синхронизации системных шин ISA и PCI. Емкость ОЗУ определяется типом ИС и их параметрами. ИС изготавливаются обычно в пластмассовых корпусах с выводами по обоим сторонам (DIP корпус) с небольшим числом выводов. Типы ИС могут отличаться друг от друга емкостью, разрядностью и другими показателями [18], приведенными в табл. 3.1. Таблица 3.1 Типы ИС ОЗУ

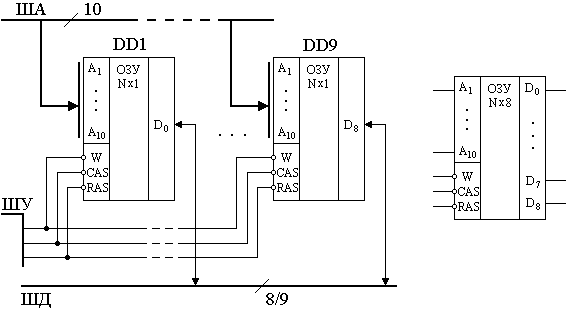

Общая емкость ИС ОЗУ определяется числом ячеек N, их разрядностью R и числом обособленных внутри массивов b элементов по формуле: V = N R b (бит). Каждый массив b стробируется (регенерируется) в ИС своим сигналом, используя один и тот же информационный регистр для обмена с ШД. Для увеличения разрядности ячеек ОЗУ, равной разрядности ШД, ИС объединяют в блоки (банки), собирая их на отдельных миниплатах с ножевым разъемом (SIMM или DIMM) или штырьковым (SIP). Эти платы затем устанавливаются в слоты на системной плате ЭВМ. На рис. 3.6, а показана схема банка ОЗУ, имеющего 8- разрядную ШД и один разряд для контроля информации на четность. Банк собран на 30 - контактном SIMM - модуле по байтной структуре на 9 ИС ОЗУ емкостью N 8 бит. Емкость банка соответствует ИС, блок-схема которой показана на рис. 3.6, б. Если nR = nC = 10, то V = N R b = 2020 8 1 бит = 1 Mб. Для обращения к банку адрес ячейки подается по ША дважды: сначала в первом такте передается <AR (1, 10)> и по сигналу RAS = 0 он запоминается старшими разрядами регистра адреса: RGA (11, 19) = ША (1,10) RAS. Затем во втором такте передается адрес столбца, который стробируется импульсом CAS: RGA (1, 10) = ША (1, 10) CAS. При отсутствии сигнала записи W = 1 в следующих тактах содержимое 8 бит с информационных выходов D0 D7 передается по ШД в МП. Девятый информационный выход ИС D8 используется для контроля данных на четность и в некоторых банках отсутствует при высокой надежности ИС.  ОЗУ Nx1 A1 . . . А10 W CAS RAS D0 ОЗУ Nx1 A1 . . . А10 W CAS RAS D8 ОЗУ Nx1 A1 . . . А10 W CAS RAS D0 . . . D7 D8          а б Рис. 3.6. Схема наращивания разрядности ОЗУ: а – схема объединения 1- разрядных ИС в 8-разрядную шину данных, б – схема 8-разрядного ЗУ С увеличением разрядности ШД 30 - контактные однобайтные блоки SIMM занимают много места для установки в слоты системной платы и с появлением Pentium заменены на 72 - контактные 36-битовые модули (D0 D31) с байтной организацией и с контролем каждого байта на четность или на сдвоенные модули DIMM с 64 разрядной ШД. Модули SIMM обозначаются как 256 К 36, 512 К 36, 1 М 36, 2 М 36, 4 М 36, 8 М 36, 16 М 36, что соответствует емкости 1, 2, 4, 8, 16, 32 и 64 Мб. Каждая ИС ОЗУ маркируется. Обычно, в соответствии с табл. 3.1, в ее обозначение включают наименование, разрядность, емкость и быстродействие в десятках нс. Например, маркировка ИС МК44256Р-8 означает: МК4 – память ОЗУ, 4 – четырехразрядная с N = 256 К, Р – корпус пластмассовый, 8 – быстродействие ИС, равное 80 нс. В зависимости от технологии изготовления, структуры и способов увеличения быстродействия DRAM ИС ОЗУ в компьютерах в качестве системной памяти используются PM, FRM, EDO, BEDO, SDRAM [7,14]: PM DRAM – динамическое ОЗУ со страничной выборкой (также регенерацией) содержимого ячеек в информационный статический регистр ИС при последовательной подаче адреса строки AR и сигнала RAS; адреса АС и сигнала CAS. PM позволяет после первого обмена осуществлять дополнительные передачи данных только с изменением младших адресов АС и повторением сигнала стробирования CAS. FRM DRAM – быстрая PM, позволяет осуществлять, в отличие от PM DRAM, последующие передачи без повторения сигнала стробирования CAS: на ША выставляются лишь адреса столбцов. EDO DRAM – динамическое ОЗУ со страничной выборкой и встроенным конвейером вывода – усовершенствованная технология PM DRAM. Данные в конвейере (буферном регистре вывода) запоминаются и поэтому процесс вывода не критичен к длительности и времени подачи сигнала CAS, выборка может быть сокращена на 1-2 такта за счет сокращения тактов ожидания и перекрываться во времени. Однако EDO не допускает чередования адресов AR, порождающих конфликты на ШД, общей для всех банков памяти обычных SIMM-модулей. BEDO DRAM – пакетная EDO с длинной пакета при передаче в четыре двойных / счетверенных слова (Pentium). При доступе к ОЗУ формируется только стартовый адрес <AR>/<АС> в первом обращении. Дальнейшие <АС> - адреса генерирует встроенный в ИС счетчик. Преимуществом BEDO является возможность сцепления пакетов в конвейере в одной и той же странице и инкремента ФА следующего пакета. Внутренний конвейер BEDO при чтении отсрочивает вывод данных на один CAS-цикл в целом удлиняя первую передачу на два такта. Это позволяет осуществлять обмен пакетной передачи по схеме Х – 1 – 1 – 1 системных тактов (400 Мб/с на 64-разрядной ШД). Эффективность использования BEDO увеличивается с увеличением разрядности пакета. SDRAM – синхронная динамическая память, которая работает по принципу, что и BEDO, но рассчитана на передачу от одного двойного слова до полной страницы. В основе SDRAM лежит трехступенчатая конвейерная архитектура с доступом к 2 блокам ИС с чередованием адресов. В конвейере используется быстродействующий буфер I/O, что позволяет увеличить частоту синхронизации до 200 МГц и обеспечить скорость обмена данными до 640 Мб/с по 64-разрядной ШД. Системная память собирается из набора ИС на миниплатах, которые затем вставляются в разъемы ОЗУ и объединяются в банки. Обычно под банком понимаются миниплаты (СБИС) емкостью 2, 4, 8, 16 Мб с набором ИС и разрядностью, соответствующей ШД МП, имеющей свой один RAS-сигнал и несколько CAS-сигналов. Различают S – SIMM и S – DIMM миниплаты с 1 общим сигналом RAS и D – SIMM и D – DIMM миниплаты с 2 независимыми сигналами RAS. Все S - и D - миниплаты имеют одинаковое число CAS сигналов. Если разрядность одной (нескольких) миниплаты соответствует разрядности ШД системной шины МП, то S – миниплаты будут образовывать один банк данных, а D – два банка. С увеличением емкости памяти в одной ИС, для своевременной регенерации строки (время регенерации 15.6 мкс), разработчики разбивают память на отдельные массивы b с 1, 2, 4, 8 Кб регенерацией. Каждая такая ИС имеет по одному регистру адреса и информационному буферному регистру и не допускает одновременного обращения к нескольким массивам. ЭВМ с процессорами Pentium, как правило, оснащаются EDO и SDRAM ОЗУ, устанавливаемыми в DIMM миниплатах. Для определения конфигурации и характеристик ОЗУ в миниплату впаивается ППЗУ EEPROM емкостью 256 байт. Информация с ППЗУ считывается BIOS для автоматической настройки режима обмена ОЗУ с системной шиной. Обмен осуществляется с коррекцией ошибок по способу ECC, для чего разрядность шины данных ОЗУ доведена до 80 бит. С увеличением частоты системной шины с 66 до 75 МГц и более все виды памяти DRAM достигают своего предела, кроме SDRAM с длительностью такта около 8 нс. SDRAM, хотя и имеет 5 тактов начальной стартовой передачи операнда, в последующих пакетных передачах 64-битные данные передаются за 1 такт. Для адресации пакетов в SDRAM используется счетчик с автоинкрементом адреса и специальный буферный регистр режимов. Пакет содержит данные из разных массивов длиной 2, 4, 8 слов или целую страницу. Режим обмена СБИС SDRAM, имеющий средства саморегенерации, можно перепрограммировать. Маркировка СБИС ОЗУ SDRAM изготовителей ведущих фирм емкостью 64 Мбит с внутренней организацией V = N R b = 2 М 8 4 бит, соотношением разрядности строки / столбца равным nR / nC = 11 / 10, поддерживаемых чипсетами 430 TX, 430VX и 440 LX, приведена в табл. 3.2. Таблица 3.2 Маркировка ОЗУ фирм изготовителей SDRAM

В режиме пакетной передачи четырех двоичных слов быстродействие обмена для различных типов ОЗУ может характеризоваться на частоте 66 МГц следующим образом: SRAM (линейный кэш-2) – 3 - 2 - 2 - 2; динамическая память FPM – 5 - 3 - 3 - 3; EDO – 5 - 2 - 2 - 2, BEDO и SDRAM – 5 - 1 - 1 - 1. Эти соотношения показывают, что для быстрой обработки данных с применением BEDO и SDRAM становятся эффективным в составе ЭВМ только тыльный кэш-2. |