ТехнКомпЭВС. Практикум По дисциплине Технология компонентов эвс

Скачать 40.57 Mb. Скачать 40.57 Mb.

|

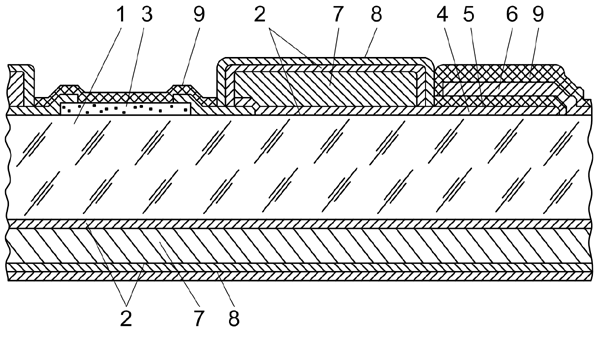

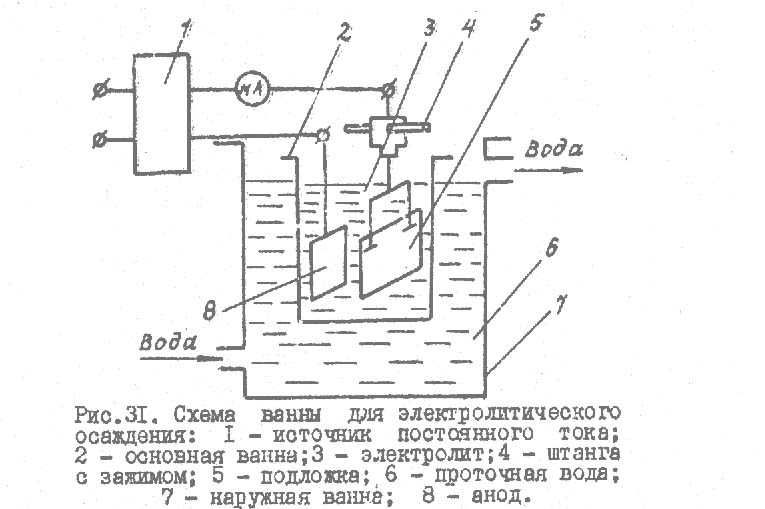

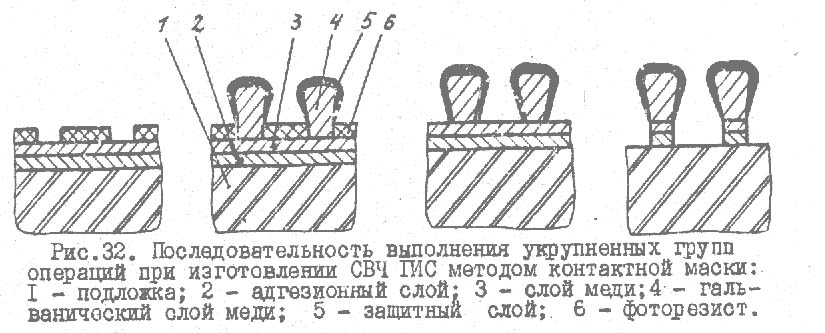

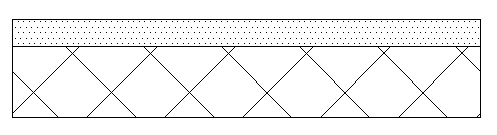

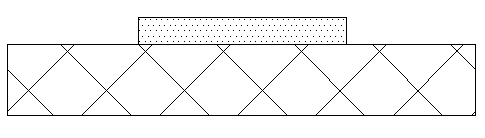

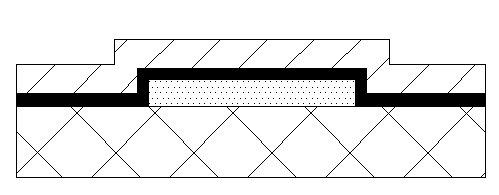

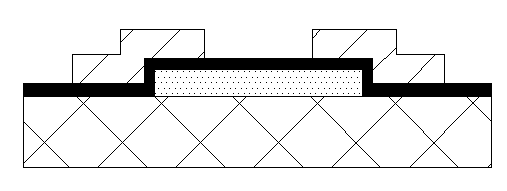

Технология СВЧ ГИСОсновным элементом СВЧ ГИС является МПЛ. Толщина пленочных проводников МПЛ выбирается в зависимости от рабочей частоты и составляет 2÷5 скин-слоя. На практике толщина пленочных проводников МПЛ составляет 5÷20 мкм. Поперечное сечение микрополосковой платы схематически изображено на рис.26.  Рис. 26. Фрагмент структуры микрополосковой платы СВЧ ГИС Рис. 26. Фрагмент структуры микрополосковой платы СВЧ ГИС1 – диэлектрическая подложка; 2 – адгезионный подслой; 3 – резистор; 4 – нижняя обкладка конденсатора; 5 – диэлектрик конденсатора; 6 – верхняя обкладка конденсатора; 7 – проводящий слой номинальной толщины; 8 – антикоррозионное покрытие; 9 – защитное покрытие. Слои 2, 7, 8 образуют проводники МПЛ и заземляющую плоскость. Технология изготовления СВЧ ГИС и МСБСВЧ ГИС и МСБ могут быть реализованы по тонко- и толсто- пленочной технологии. Их различие заключается не в толщине пленок, а в способе их нанесения. По толстопленочной технологии изготавливаются в основном схемы, работающие на частотах f < 1 ГГц., и схемы, для которых требования к точности изготовления и электрическим характеристикам не очень высоки. Тонкопленочная технология предпочтительна в более высокочастотном диапазоне (f > 1 ГГц) для изготовления высокоточных схем, а большая плотность монтажа позволяет получить схемы меньших размеров по сравнению с толстопленочными. Формирование пассивных пленочных элементов с сосредоточенными параметрами (R,C) производят известными методами тонкопленочной технологии. Остановимся на особенностях создания проводящих элементов с распределенными параметрами (МПЛ и элементов на их основе). Для этого используют два технологических маршрута – с использованием метода технологической коммутации и метода контактной маски. В  первом технологическом маршруте после напыления тонкого проводящего слоя толщиной 1–2 мкм проводится фотолитография, в результате формируется обобщенная конфигурация проводящих элементов, соединенных технологическими проводниками, которые удаляются после электролитического наращивания толстого (3–20 мкм) слоя проводящих элементов (рис.27) Рис. 27. Схема ванны для электролитического осаждения: 1 – источник постоянного тока; 2 – основная ванна; 3 – электролит; 4 – штанга с зажимом; 5 – подложка; 6 – проточная вода; 7 – наружная ванна; 8 – анод. В  о втором маршруте (рис.28) после напыления тонкопленочного слоя на нем формируется контактная маска, которая удаляется после электролитического наращивания. Рис. 28. Последовательность выполнения укрупненных групп операций при изготовлении СВЧ ГИС методом контактной маски: 1 – подложка; 2 – адгезионный слой; 3 – слой меди; 4 – гальванический слой меди; 5 – защитный слой; 6 – фоторезист. Для повышения качества СВЧ ГИС и МСБ применяют различные технологические приемы. Так, при электролитическом наращивании пленок для их чистоты используют импульсные токи и реверсирование; при термическом испарении – высокие скорости осаждения и т.д. Выбор способа установки и монтажа навесных компонентов на плату СВЧ ГИС и МСБ зависит от их конструкции. Используют либо поверхностный монтаж, либо монтаж в отверстие платы на основание, соединенное с корпусом. Технологические маршруты изготовления СВЧ ГИС и МСБ отличаются большим разнообразием. По одному из них, приведенному ниже выполнены образцы лабораторных работ. Технологический маршрут изготовления СВЧ ГИС и МСБ

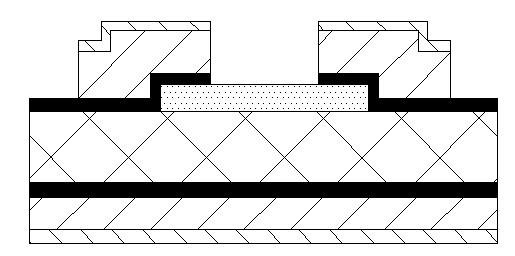

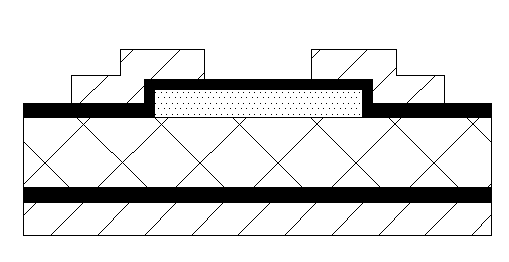

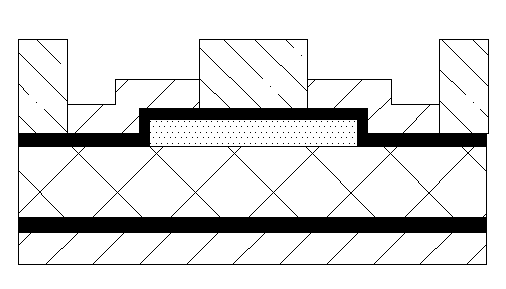

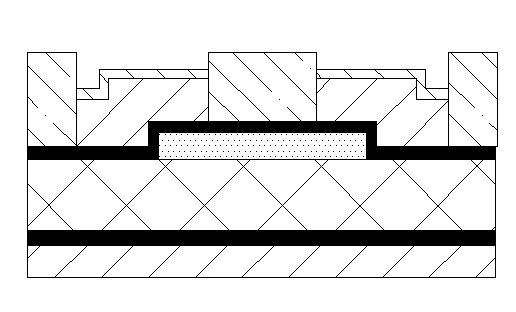

1  . 2   . 3  . 4  . 5  . 6  7. . 8   . 9. Рис. 29. Схема основных этапов технологического процесса изготовления одного из вариантов микрополосковой платы СВЧ-модуля; 1 – очистка поликора; 2 – напыление резистивного слоя; 3 – ФЛ в резистивном слое; 4 – напыление проводящего слоя Cr-Cu; 5 – ФЛ (в слое Cu); 6 – напыление структур Cr-Cu с обратной стороны подложки; 7 – ФЛ в слое фоторезиста перед гальваническим доращиванием Cu и осаждением Au; 8 – гальваническое доращивание Cu и осаждение Au; 9 – удаление ФР и стравливание технологического поля из Cr. |