Микропроцессоры AVR. Реферат Микроконтроллеры avr студента 3го курса Курапова Анатолия Введение

Скачать 0.65 Mb. Скачать 0.65 Mb.

|

|

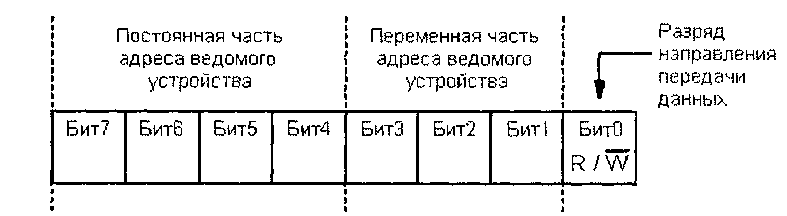

Адресация ведомых устройств Выбор ведомого устройства, с которым хотело бы обмениваться данными ведущее устройство, осуществляется посредством первого байта, который всегда определяется как адрес ведомого устройства – первый байт последовательности данных. Он однозначно сопоставлен определенному устройству, подключенному к шине, и имеет длину 7 бит (разряды от 1 до 7). Теоретически, таким образом можно адресовать до 128 ведомых устройств, однако по определению некоторые адреса ведомых устройств имеют особое значение. Адрес ведомого устройства состоит из двух частей: постоянной и переменной (рис. 7.14).  Рис. 7.14. Формат адреса шины I2C Постоянная часть адреса описывает требования к определенным группам устройств и определяется изготовителем. Его длина определена в результате практического опыта и в большинстве случаев составляет 4 бита. Он будет тем короче, чем больше однотипных устройств в схеме. Постоянная часть адреса жестко "прошита" в интегральной схеме и не может быть изменена пользователем. Переменная часть адреса ведомого устройства служит для выбора определенного устройства из группы однотипных кристаллов, среди которых все имеют постоянную часть адреса ведомого устройства. Благодаря этому, к шине могут быть подсоединены несколько однотипных интегральных схем. Переменная часть в большинстве случаев определяется пользователем с помощью внешних схем (через дополнительные выводы). С помощью разрядов 1-7 адреса ведомого устройства однозначно идентифицируется требуемый ведомый блок. Разряд 0 задает направление передачи данных. Он определяет, должны ли быть приняты или переданы данные. Если разряд направления передачи данных содержит лог. 1 (чтение), то ведущее устройство находится в режиме приемника, а ведомое – в режиме передатчика. Если разряд направления передачи данных содержит лог. 0 (запись), то ведущее устройство будет работать как передатчик, а ведомое – как приемник. Адрес ведомого устройства также подтверждается этим устройством с помощью бита квитирования. Если ведущее устройство после адресации получает отрицательное квитирование, то оно может заключить, что ведомое устройство или вообще отсутствует, или в настоящий момент с ним невозможно установить связь (например, оно занято обработкой заданий, критическими с точки зрения времени). 3. Аналого-цифровое преобразование Число в цифровой форме определяется на основании отношения входного напряжения к полному номиналу напряжения аналого-цифрового преобразователя (АЦП). Например, если на вход АЦП с номинальным напряжением 5 В подать напряжение 1 В„ то на цифровом выходе появится число, соответствующее 1/5=0,2 разрешающей способности преобразователя. Так, если используется АЦП с разрешением 8 бит, то максимальное возможное значение на его выходе 2 - 1 = 255. Таким образом, напряжению 1 В на аналоговом входе соответствует 0,2 - 255 = 51 на цифровом выходе. Встроенные АЦП микроконтроллеров AVR имеют разрешение 10 бит и позволяют считывать напряжение на одном из восьми (в некоторых моделях – пяти) аналоговых входов (обычно – порт А). В микроконтроллерах AVR для управления режимом АЦП используются два регистра: регистр управления ADCSR (рис. 8.1) и регистр мультиплексирования ADMUX (определяет, какие из восьми входов порта А являются аналоговыми).

Рис. 8.1. Регистр ADCSR микроконтроллеров AVR Назначение разрядов регистра ADCSR: ADPS0 – ADPS2 – выбор коэффициента деления тактовой частоты (табл. 8.1); чем выше частота работы АЦП (производная от частоты системной синхронизации), тем ниже эффективное разрешение, поэтому следует устанавливать коэффициент деления; ADIE – разряд маскирования прерывания от АЦП (1 – по окончанию преобразования разрешено прерывание); ADIF – флаг прерывания от АЦП (устанавливается аппаратно по окончанию цикла преобразования); ADFR – лог. 1 в этом разряде переводит АЦП в несинхронизированный режим работы – обычно АЦП работает в режиме прерывания, чтобы процессор каждый раз не ожидал завершения медленно протекающего преобразования, однако в несинхронизированном режиме АЦП выполняет преобразование постоянно, как можно быстрее (на период такого преобразования должны быть запрещены все прерывания); ADSC – флаг начала преобразования; ADEN – флаг разрешения использования АЦП. Таблица 8.1. Выбор коэффициента деления частоты системной синхронизации для тактирования АЦП микроконтроллеров AVR

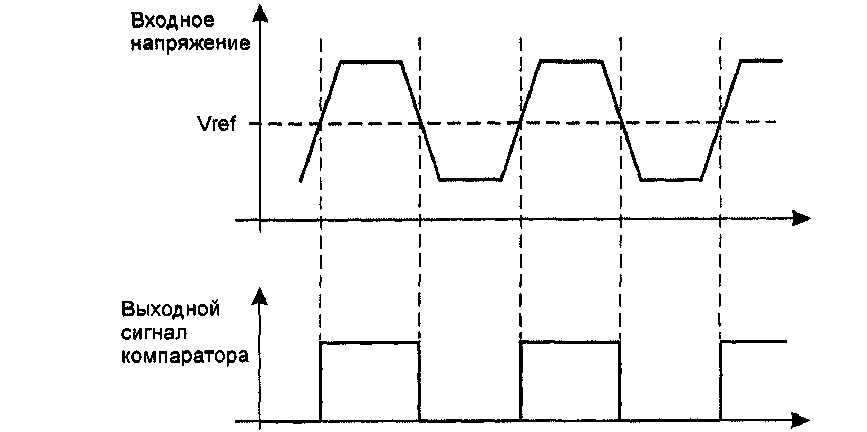

Таким образом, в общем случае процесс аналого-цифрового преобразования в микроконтроллерах AVR протекает следующим образом: установить в лог. 1 разряды регистра ADMUX, соответствующие аналоговым входам; установить разряды 0-2 регистра ADCSR для выбора коэффициента деления частоты системной синхронизации; установить в лог. 1 разряд ADIE для разрешения режима прерывания; установить в лог. 1 разряд ADEN, чтобы разрешить использование АЦП; установить в лог. 1 разряд ADSC, чтобы начать преобразование; результат преобразования сохраняется в регистровой паре ADCL, ADCH; Встроенный аналоговый компаратор В ряде моделей микроконтроллеров AVR используется встроенный аналоговый компаратор напряжения, сравнивающий входное напряжение на двух входах. Как только напряжение на неинвентирующем входе станет больше, чем на инвентирующем, на выходе компаратора устанавливается лог. 1. Часто аналоговый компаратор используют для сравнения некоторого входного напряжения с опорным (рис. 8.4). Для активизации компаратора требуется предварительно перевести соответствующие выводы микроконтроллера в режим входов. Время срабатывания компараторов небольшое, поэтому с их помощью можно быстро формировать ответные реакции на изменение соотношений входных напряжений. В микроконтроллерах AVR входам компаратора AIN0 и AIN1 обычно соответствуют разряды 0/1 или 2/3 порта В. В микроконтроллерах PIC конфигурация входов компаратора (вывода порта А) настраивается с помощью разрядов регистра CMCON, о чем речь пойдет чуть позже. В микроконтроллерах AVR для управления работой аналогового компаратора используется регистр ACSR (рис. 8.5), расположенный в области ввода/вывода по адресу 0x08 (адрес 0x28 в SRAM).  Рис. 8.4. Принцип работы аналогового компаратора напряжений

Рис. 8.5. Регистр ACSR микроконтроллеров AVR Назначение разрядов регистра ACSR: ACD – если установлен в лог. 1, то питание аналогового компаратора отключено; АСО – напрямую связан с выходом аналогового компаратора; ACI – флаг прерываний от аналогового компаратора – устанавливается в лог. 1, когда наступает событие, определенное разрядами ACIS1 и ACIS0; ACIE – разряд разрешения прерывания от аналогового компаратора; ACIC – разряд разрешения захвата на входе аналогового компаратора; для того чтобы можно было вызвать прерывание по захвату, оно должно быть разрешено разрядом TICIE1 в регистре TIMSK; ACIS1, ACIS0 – устанавливают вид события на выходе аналогового компаратора, которое должно вызвать прерывание его работы (табл. 8.3). Таблица 8.3. Вид событий для вызова прерывания от аналогового компаратора

4. Программирование микроконтроллеров AVR семейства Mega Общие сведения В общей сложности микроконтроллеры семейства Mega поддерживают следующие режимы программирования: режим последовательного программирования (по интерфейсу SPI); режим параллельного программирования при высоком напряжении; режим программирования через интерфейс JTAG. Под “высоким” напряжением здесь понимается управляющее напряжение (12 В), подаваемое на вывод RESET микроконтроллера для перевода последнего в режим программирования. Режимы программирования для конкретного микроконтроллера представлены в табл. 9.1. Таблица 14.1. Режимы программирования микроконтроллеров семейства Mega

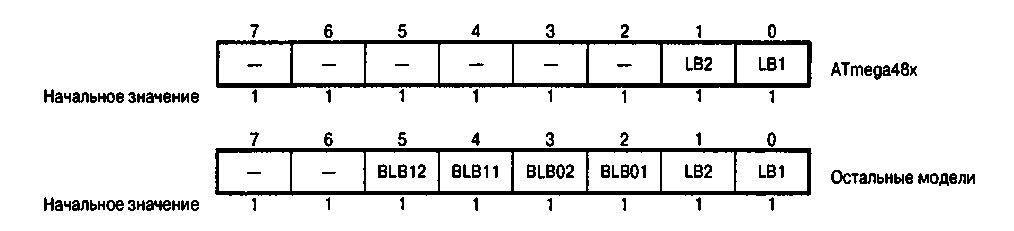

Кроме того, микроконтроллеры семейства Mega имеют возможность самопрограммирования. Под этим термином понимается изменение содержимого памяти программ, управляемое самим микроконтроллером. В процессе программирования могут выполняться следующие операции: стирание кристалла (chip erase); чтение/запись FLASH-памяти программ; чтение/запись EEPROM-памяти данных; чтение/запись конфигурационных ячеек; чтение/запись ячеек защиты; чтение ячеек идентификатора; чтение калибровочного байта. Все модели микроконтроллеров поставляются со стертой памятью программ и памятью данных (во всех ячейках находится число $FF) и пригодны к немедленному программированию. Защита кода и данных Содержимое FLASH-памяти программ, а также содержимое EEPROM-памяти данных может быть защищено от записи и/или чтения посредством программирования ячеек защиты (Lock Bits) LB1 и LB2. Возможные режимы защиты, соответствующие различным состояниям этих ячеек, приведены в табл. 8.2. Таблица 8.2. Режимы защиты

В режимах 2 и 3 запрещается также изменение конфигурационных ячеек. Поэтому включение защиты следует выполнять в самую последнюю очередь, после программирования остальных областей памяти микроконтроллера. Во всех микроконтроллерах семейства, кроме ATmega48x, имеется четыре дополнительные ячейки защиты — BLB02, BLB01, BLB12 и BLB11. Ячейки BLB02:BLB01 определяют уровень доступа из секции загрузчика к коду, расположенному в секции прикладной программы, а ячейки BLB12:BLB11, наоборот, определяют уровень доступа из секции прикладной программы к коду, расположенному в секции загрузчика. Отсутствие указанных ячеек в модели ATmega48x обусловлено отсутствием у последней выделенной секции загрузчика. Возможные режимы защиты, соответствующие различным состояниям этих ячеек, приведены в табл. 9.3 и табл. 9.4 соответственно. Таблица 9.3. Режимы защиты секции прикладной программы

Таблица 9.4. Режимы защиты секции загрузчика

Все перечисленные ячейки защиты сгруппированы в одном байте. Расположение ячеек защиты в нем для разных моделей приведено на Рис. 14.1.  Рис. 9.1. Байт ячеек защиты В исходном (запрограммированном) состоянии во всех ячейках защиты содержится 1, после программирования – 0. Стирание ячеек (запись в них лог. 1) может быть произведено только при выполнении команды “Стирание кристалла”, уничтожающей также содержимое FLASH- и EEPROM-памяти. Конфигурационные ячейки Как следует из названия, конфигурационные ячейки (Fuse Bits) определяют различные параметры конфигурации микроконтроллера. Эти ячейки расположены в отдельном адресном пространстве, доступном только при программировании. Все конфигурационные ячейки сгруппированы в несколько байтов, а состав этих ячеек зависит от конкретной модели микроконтроллера. Наличие тех или иных ячеек в конкретном микроконтроллере можно определить по табл. 9.5, где в столбцах, отмеченных “звездочкой”, указаны состояния конфигурационных ячеек по умолчанию. Краткое назначение всех конфигурационных ячеек приведено в табл. 9.6. Подробное описание их назначений было приведено в соответствующих главах книги. Для изменения содержимого конфигурационных ячеек используются специальные команды программирования. Команда “Стирание кристалла” на состояние этих ячеек не влияет. Напоминаю, что при запрограммированной ячейке защиты LB1 конфигурационные ячейки блокируются. Поэтому конфигурацию микроконтроллера необходимо задавать до программирования ячеек защиты. Таблица 9.5. Конфигурационные ячейки микроконтроллеров семейства

Таблица 9.6. Назначение конфигурационных ячеек

1) Недоступна при программировании по последовательному каналу 2) Изменение состояния этой ячейки вступает в силу сразу же после ее программирования. 3)Только в ATmega48x. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||