Микропроцессоры AVR. Реферат Микроконтроллеры avr студента 3го курса Курапова Анатолия Введение

Скачать 0.65 Mb. Скачать 0.65 Mb.

|

|

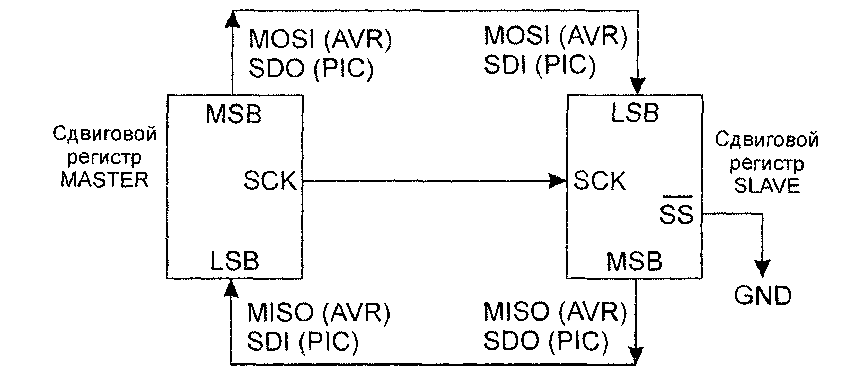

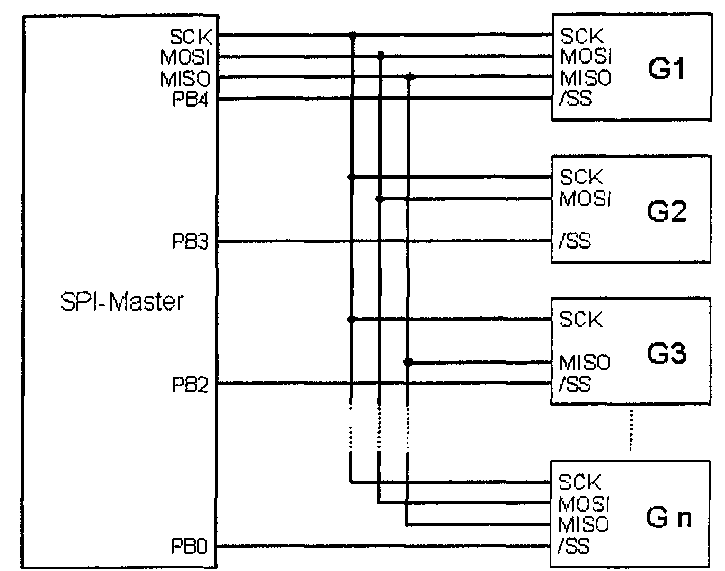

Синхронная передача данных по интерфейсу SPI Интерфейс SPI (Serial Peripheral Interface) служит для обмена данными с периферийными устройствами. В качестве таких устройств могут выступать простые сдвиговые регистры или буквенно-цифровые модули индикации, а также сложные микропроцессорные системы или системы регистрации данных. Многие компании-изготовители предлагают большой выбор устройств с интерфейсом SPI. В случае обмена данными по интерфейсу SPI микроконтроллер работает в режиме ведущего устройства (Master), взаимодействуя с одним или несколькими ведомыми блоками (Slave). Схема передачи данных по интерфейсу SPI микроконтроллеров AVR/PIC показана на рис. 7.6 (MSB – старший разряд, a LSB – младший разряд передаваемого байта).  Рис. 7.6. Схема передачи данных по интерфейсу SPI микроконтроллеров AVR Ведущее устройство берет на себя активную часть обмена данными, вызывая передачу и управляя процессом. Ведомое устройство не может само быть активным. Оно принимает и передает данные только тогда, когда происходит его активизация со стороны ведущего устройства по линии /SS. Ведущее устройство также генерирует такт для передачи по выходной линии SCK. Для ведомого блока вывод SCK является входом, через который он получает от Master-устройства тактирующие сигналы. Если ведомое устройство активизируется ведущим по линии /SS, то начинается обмен данными: Master записывает подлежащий передаче байт в свой сдвиговой регистр данных (для микроконтроллеров AVR – регистр SPDR, для микроконтроллеров PIC – регистр SSPBUF). С помощью каждого выработанного тактового импульса Master перемещает один бит данных на выход MOSI/SDO, a Slave одновременно в обратном направлении передает один бит на вход MISO/SDI ведущего блока. Таким образом, в течение цикла SPI, состоящего из восьми тактовых импульсов, Master и Slave обмениваются байтом данных. По окончании передачи данных в регистре состояния интерфейса SPI устанавливается флаг соответствующего запроса на прерывание. Этот флаг указывает на окончание передачи и вызывает запрос на прерывание после того как в регистре управления SPI будет установлен разряд разрешения на прерывание от интерфейса SPI. В режиме "Master" текущая передача данных может быть преждевременно завершена выдачей в линию /SS сигнала лог. 1. К интерфейсу SPI ведущего устройства можно подключать несколько ведомых устройств (пример для микроконтроллеров AVR – на рис. 7.7), однако активным будет только то из них, на вход /SS которого будет подан уровень лог. 0. Выходы MISO незадействованных ведомых блоков находятся в высокоомном состоянии и не влияют на процесс передачи данных. В примере на рис. 7.7 устройство G2, с точки зрения ведущего устройства, является только блоком передачи (например, ЦАП с интерфейсом SPI), а устройство G3 – только блоком приема.  Рис. 7.7. Подключение нескольких ведомых устройств к одному ведущему по SPI (для AVR) В микроконтроллерах AVR в качестве линий SPI используются выводы порта В (табл. 7.2). В микроконтроллерах PIC для последовательной синхронной передачи данных используется порт MSSP, работающий в режиме интерфейса SPI или I2С. Линиям SPI соответствуют выводы порта А и С (табл. 7.2). Таблица 7.2. Распределение выводов портов для линий интерфейса SPI

Регистры управления и состояния SPI в микроконтроллерах AVR Регистр управления SPCR интерфейса SPI в микроконтроллерах AVR (рис. 7.8) находится в области ввода/вывода по адресу 0x0D (адресу 0x2D в SRAM).

Рис. 7.8. Регистр управления SPCR микроконтроллеров AVR По окончании передачи данных через интерфейс SPI аппаратная часть устанавливает в регистре состояния SPCR разряд SPIF (флаг прерываний от интерфейса SPI). Этот флаг указывает на завершение передачи, и приводит к запросу на прерывание как только в регистре управления SPCR будет установлен разряд SPIE, а в регистре состояния SREG – флаг общего разрешения прерываний I. Разряд SPE активизирует интерфейс SPI (лог. 1) или отключает его (лог. 0). После поступления сигнала сброса этот разряд принимает значение лог. 0, и тем самым система SPI отключается. Если разряд DORD содержит лог. 0, то сначала будет передан старший разряд байта данных. При DORD = 1 первым передается младший разряд. Когда разряд MSTR содержит лог. 0, то система SPI определяется как ведомая (Slave), а при MSTR = 1 она будет определена как ведущая (Master). Когда линия /SS в режиме Master сконфигурирована как вход, то разряд MSTR при низком уровне сигнала на выводе /SS сбрасывается в лог. 0, и тем самым интерфейс SPI определяется как Slave. В этом случае в регистре состояния устанавливается флаг SPIF. Когда разряд CPOL содержит лог. 0, то на выходе SCK в неактивном состоянии находится сигнал низкого уровня. Если CPOL = 1, то на SCK в неактивном состоянии находится сигнал высокого уровня. С помощью этого разряда, а также разряда СРНА (выбор фазы синхронизации) устанавливается один из четырех режимов передачи данных по интерфейсу SPI (табл. 7.3). Разряды SPR1 и SPR0 при работе интерфейса SPI в режиме Master служат для выбора тактовой частоты для линии SCK. Если система SPI сконфигурирована как Slave, то эти разряды не имеют никакого значения. Взаимосвязь между разрядами SPR1, SPR0 и частотой импульсов в линии SCK показана в табл. 7.4. Таблица 7.3. Режимы передачи данных по интерфейсу SPI в МК AVR

Таблица 7.4. Частота импульсов в линии SCK в зависимости от разрядов SPR1, SPR0

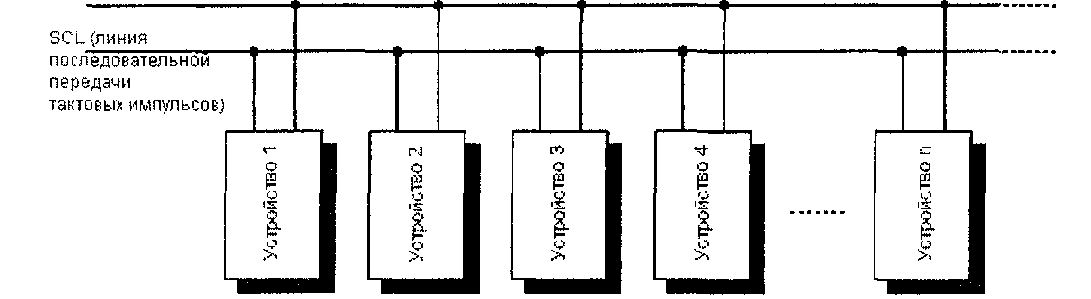

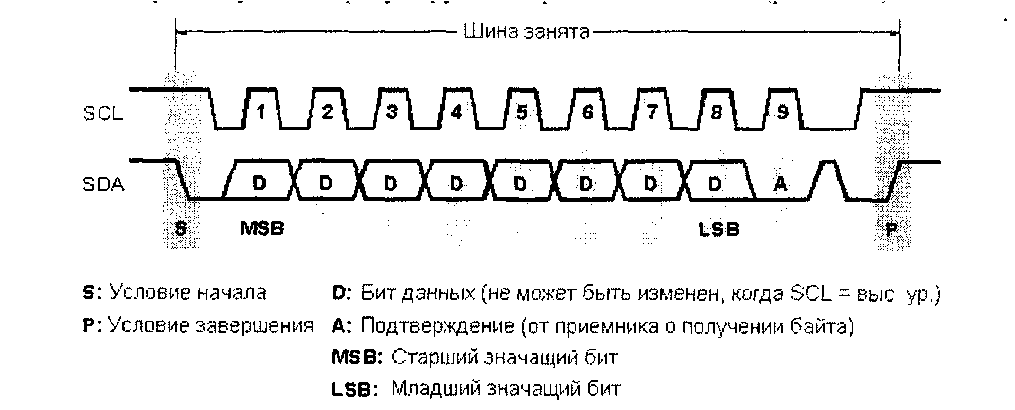

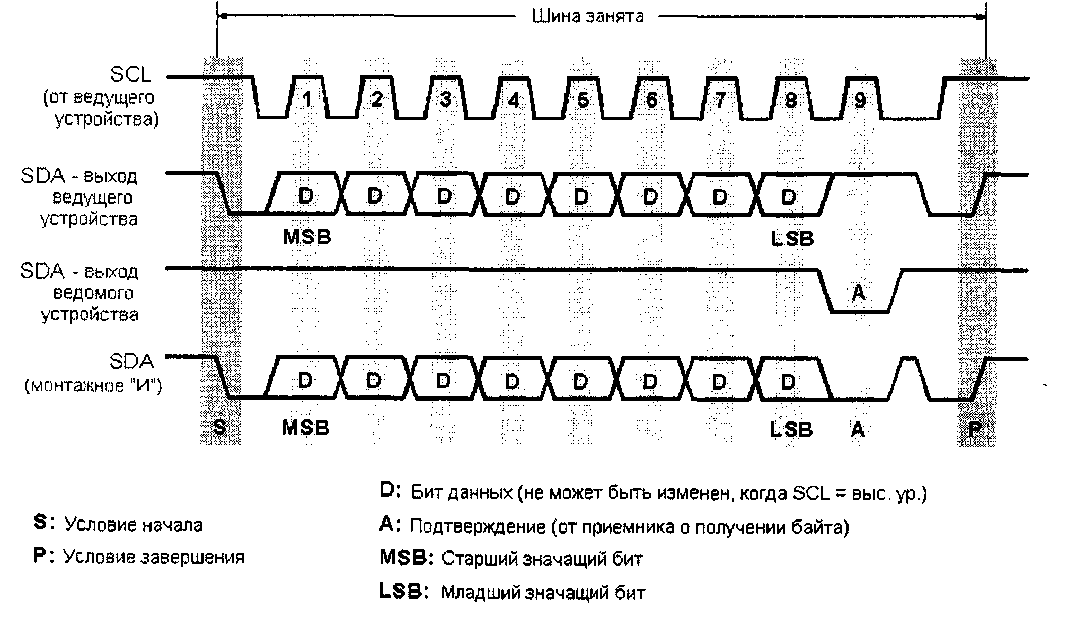

Регистр состояния SPSR интерфейса SPI в микроконтроллерах AVR расположен в области ввода/вывода по адресу 0х0Е (0x2E в SRAM). В этом регистре используются только разряды 6 и 7: разряд 6 – флаг WCOL – устанавливается в том случае, когда во время передачи данных через интерфейс SPI предпринимается попытка записи в регистр данных SPI, что приводит к разрушению только что переданного байта данных. По этой причине текущая передача данных доводится до завершения, а новый байт не записывается в сдвиговый регистр интерфейса SPI. Флаг WCOL должен быть сброшен пользователем вручную посредством считывания регистра состояния и последующего обращения к регистру данных интерфейса SPI; разряд 7 – флаг SPIF – указывает на завершение передачи и вызывает запрос на прерывание, как только в регистре управления SPCR будет установлен разряд SPIE, а в регистре состояния SREG – разряд I. Когда линия /SS в режиме Master сконфигурирована как вход, то при низком уровне сигнала на выводе линии /SS также будет установлен флаг SPIF. Флаг SPIF сбрасывается автоматически аппаратной частью при выполнении подпрограммы обработки прерывания от интерфейса SPI. Альтернативно, сброс может быть выполнен вручную посредством считывания регистра состояния SPSR и последующего обращения к регистру данных интерфейса SPI. Синхронная передача данных по интерфейсу I2С Интерфейс I2С (Inter-integrated Circuit), состоящий только из двух линий (SDA и SCL), предназначен для низкоскоростного последовательного обмена данными с периферийными устройствами, подсоединенных к одной общей шине (рис. 7.11).  Рис. 7.11. Подключение устройств к шине I2C Характеристики шины I2С: работа только с двумя линиями, благодаря чему требуется меньше мест соединения и минимизируются затраты на проводку; зона действия – до 3 м; возможность работать в режиме с одним ведущим блоком (Single-Master) или с несколькими ведущими блоками (Multi-Master). Линия SCL используется для передачи синхроимпульсов. Если данные не передаются, она содержит высокий уровень сигнала. Линия SDA используется для побитной передачи данных. Если данные не передаются, то она имеет высокий потенциал. Передаваемые данные действительны в фазе высокого уровня такта и могут менять свое состояние только в фазе низкого уровня. Каждый блок, подсоединенный к шине, во время передачи данных может быть или приемником или передатчиком, а также ведущим (Master) или ведомым (Slave). Ведущее устройство инициирует передачу данных. В частности, Master занимает шину тем, что генерирует стартовый сигнал на линии SCL и начинает обмен с ведомым устройством. До тех пор, пока на шине работает ведущее устройство, не может быть активным никакой другой Master-блок. Ведомым является устройство, по адресу которого обращается ведущее устройство с требованием передачи данных. Теоретически Master может одновременно снабжать одними и теми же данными несколько ведомых устройств. В роли ведущего устройства в большинстве случаев выступает микропроцессор, оборудованный или специальной аппаратной частью с шиной типа I2С, или контроллером шины, работающим под управлением специального программного обеспечения. Протокол шины I2С Для того чтобы несколько блоков могли обмениваться данными, необходим некоторый протокол, который описывает процесс передачи данных по шине и в любой момент времени не допускает ошибочной интерпретации состояния шины. В случае шины с несколькими ведущими устройствами (что относится и к I2С) необходимо также установить, когда и какое ведущее устройство имеет право занимать шину. Эти условия регулируются протоколом шины (рис. 7.12).  Рис. 7.12. Протокол передачи байта данных через шину I2C Работа шины и ее занятость, определяется условием начала передачи – изменение ведущим устройством состояние линии SDA с высокого уровня на низкий. После наступления условия начала передачи шина будет занята ведущим устройством, создавшим это условие, вследствие чего все другие ведущие устройства будут заблокированы. Условие начала является однозначным состоянием на шине, потому что смена уровня сигнала на линии SDA, как правило, допускается только тогда, когда тактовая линия SCL находится в состоянии низкого уровня. Все устройства, подключенные к шине, должны распознать условие начала передачи и переключаются на прием (ведомое устройство/приемник). Условие начала передачи также учитывается и другим ведущим устройством, которое со своей стороны имело намерение занять шину. В результате оно немедленно отзывает свое требование. Устройство, создавшее условие начала передачи, в данный момент времени является для шины ведущим (Master), а все остальные устройства – потенциальными ведомыми (Slave). Ведущее устройство теперь отвечает за тактовый сигнал и становится передатчиком. После создания условия начала ведущее устройство начинает передачу данных. Оно переводит тактовую шину в состояние низкого уровня и теперь может занять линию передачи данных затребованным информационным разрядом (высокий или низкий уровень в линии SDA). Затем тактовая шина опять переводится в состояние высокого уровня. Изменение в линии SDA может происходить только в фазе низкого уровня сигнала в линии SCL Во время фазы высокого уровня в линии SCL линия SDA должна быть стабильной. Передача данных, как правило, выполняется побайтно, при этом первым передается старший разряд. После передачи полного байта данных, состоящей из восьми тактовых циклов, следует бит подтверждения от приемника. Бит подтверждения (квитирования) – это реакция приемника на принятый байт данных. Он является для передатчика признаком того, что приемник физически присутствует и "прослушивает" линию. Одновременно с этим бит подтверждения можно рассматривать как сигнал синхронизации. Бит подтверждения, как правило, генерируется приемником. Если ведущее устройство принимает от ведомого устройства несколько байтов данных, то оно квитирует каждый отдельный байт битом подтверждения, за исключением последнего. Такое отрицательное квитирование сообщает ведомому устройству, что передача данных завершена, и далее последует условие завершения или новое условие начала передачи. Для передачи бита подтверждения ведущее устройство генерирует на линии SCL дополнительный тактовый импульс (рис. 7.13). Приемник выдает сигнал положительного квитирования, переводя линию SDA в состояние низкого уровня, или отрицательного квитирования, переводя линию SDA в состояние высокого уровня.  Рис. 7.13. Выработка бита квитирования приемником, работающим в режиме ведомого устройства Таким образом, для передачи одного байта данных, как правило, требуется девять тактовых циклов. После передачи одного байта данных и приема бита подтверждения передача данных может быть сразу же продолжена. Если приемник реагирует на передачу байта данных отрицательным квитированием, то ведущее устройство должно завершить передачу данных, опять освободив шину. Шина после окончания передачи данных, которая может состоять из любого количества байтов, опять освобождается ведущим устройством. Освобождение шины осуществляется с помощью условия завершения – изменение в линии SDA уровня сигнала с низкого на высокий в то время, когда по тактовой шине SCL передается сигнал высокого уровня. После создания условия завершения передачи шина освобождается. Условие завершения передачи также представляет собой однозначное состояние на шине. Все блоки и устройства распознают его и подготавливаются к появлению нового условия начала передачи. В том случае, если ведущее устройство из-за промежуточной занятости шины отзывает свое требование занять шину, то оно может предпринять новую попытку создать условие начала передачи и тем самым получить шину для своих нужд. Полная передача данных через шину I2С, в принципе, состоит из условия начала передачи, одного или нескольких байтов данных (за которыми, соответственно, следует бит квитирования), и условия завершения передачи. |