Микропроцессоры AVR. Реферат Микроконтроллеры avr студента 3го курса Курапова Анатолия Введение

Скачать 0.65 Mb. Скачать 0.65 Mb.

|

|

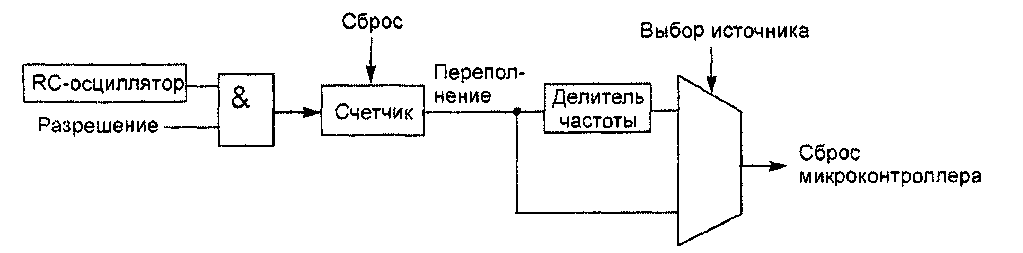

Сторожевой таймер Сторожевой таймер (watchdog timer) – встроенный таймер, тактируемый внутренним RC-осциллятором, который автоматически сбрасывает микроконтроллер при переполнении своего счетного регистра. В частности, он используется для предотвращения перехода микроконтроллера в режим бесконечного цикла, когда на него невозможно повлиять извне. Обобщенная структурная схема сторожевого таймера показана на рис. 5.1. В микроконтроллерах AVR и PIC управление сторожевым таймером несколько отличается. Так, в микроконтроллерах AVR для этого используется регистр управления WDTCR (адрес в области ввода/вывода – 0x21, адрес SRAM – 0x41) (рис. 5.2).  Рис. 5.1. Структурная схема сторожевого таймера

Рис. 5.2. Регистр WDTCR микроконтроллеров AVR Назначение отдельных разрядов регистра WDTCR: WDP0-WDP2 – выбор коэффициента деления частоты следования сигналов сброса (при этом период до наступления сброса зависит от рабочего напряжения процессора – табл. 5.1); WDE – включение/отключение сторожевого таймера (1 – включен); WDTOE – если сторожевой таймер должен быть отключен, следует установить этот разряд в лог. 1. После установки этого разряда он в течение четырех периодов такта системной синхронизации остается в состоянии лог. 1, а затем аппаратно сбрасывается в лог. 0. Программа пользователя имеет возможность отключить сторожевой таймер посредством записи лог. 0 в разряд WDE только во время этих четырех тактов системной синхронизации. Таблица 5.1 Назначение разрядов WDP0 - WDP2 регистра WDTCR

В системе команд AVR сторожевой таймер сбрасывается в исходное состояние по команде wdr. 2. Параллельные порты ввода/вывода Параллельные порты – это особые устройства ввода/вывода, позволяющие передавать во внешний мир или принимать одновременно восемь разрядов данных. Для обозначения портов используются латинские буквы А, В, С и т.д. Количество портов ввода/вывода варьируется в зависимости от модели микроконтроллера. В микроконтроллерах AVR каждому параллельному порту ввода/вывода поставлены в соответствие три регистра (букве х соответствует имя порта А, В и т.д.): DDRx – регистр направления передачи данных – определяет, является тот или иной вывод порта входом или выходом; если некоторый разряд регистра DDRx содержит лог. 0, то соответствующий вывод порта сконфигурирован как вход, в противном случае – как выход; PORTx – регистр порта – если вывод выполняет роль выхода, то в соответствующий разряд записывается значение, предназначенное для вывода; если вывод выполняет роль входа, то лог. 0 в некотором разряде регистра PORTx соответствует высокоомный вход, а лог. 1 – вход, нагруженный подтягивающим сопротивлением; PINx – регистр выводов порта – в отличие от регистров DDRx и PORTx доступен только для чтения и позволяет считать входные данные порта на внутреннюю шину микроконтроллера. Выводы портов зачастую выполняют различные альтернативные функции при работе с внутренними и периферийными модулями микроконтроллеров AVR. Так, к примеру, в некоторых моделях в качестве внешних тактовых входов таймеров/счетчиков Т/С0 и Т/С1 используются разряды 0 и 1 порта В или 4 и 5 порта D. Точное назначение выводов портов следует сверять по спецификации микроконтроллера. Последовательный ввод/вывод В отличие от параллельного обмена данными, в случае последовательного ввода/вывода используется только одна информационная линия. При этом передача данных бывает асинхронной и синхронной. При синхронном последовательном вводе/выводе синхронизируется передача отдельных битов данных с помощью одновременно передаваемого тактового сигнала. Синхронная последовательная передача данных применяется, на уровне печатных плат, в том числе – для обмена данными между различными интегрированными блоками в составе схемы микроконтроллера и различными периферийными схемами (например, для обработки видеосигнала). В противоположность этому, при асинхронной передаче данных передается не тактовый сигнал, а старт-бит и стоп-бит, определяющие начало и завершение передачи слова данных (рис. 7.1).  Рис. 7.1. Типичный формат асинхронной передачи данных (в данном примере – байта 10000010) Главной областью применения асинхронной передачи данных, является не обмен данными в составе схемы, а коммуникация между блоками, разделенными пространственно и обладающими признаками собственного интеллекта. В качестве примера можно назвать связь между персональным компьютером и принтером, модемом, программирующим устройством или регистратором данных. В микроконтроллерах AVR асинхронная передача данных осуществляется с помощью приемопередатчика UART, а в микроконтроллерах PIC – приемопередатчика USART или по шине CAN. Для синхронного ввода/вывода используется особый режим приемопередатчика USART, а также интерфейсы SPI и I2С (в микроконтроллерах PIC – с помощью порта MSSP). Приемопередатчик UART микроконтроллеров AVR Для работы UART выделены в общей сложности четыре регистра: регистр управления UCR (адрес в области ввода/вывода – 0х0А, адрес SRAM – 0х2А) – предназначен для управления функциями приемопередатчика и для разрешения/запрета прерываний от UART (рис. 7.2); регистр состояния USR (адрес в области ввода/вывода – 0x0В, адрес SRAM –0x2В) (рис. 7.3); регистр данных UDR (адрес в области ввода/вывода – 0х0С, адрес SRAM – 0x2С) – физически состоит из двух регистров, обращение к которым осуществляется по одному и тому же адресу; один из них используется для передачи, а другой – для приема данных; регистр UBRR (адрес в области ввода/вывода – 0x09, адрес SRAM – 0x29) – применяется для настройки требуемой скорости передачи данных с помощью встроенного контроллера, позволяющего устанавливать наиболее распространенные скорости передачи по стандарту RS232C.

Рис. 7.2. Регистр управления UCR микроконтроллеров AVR Если разряд RXCIE и разряд общего разрешения прерываний I в регистре состояния SREG установлены в лог. 1, то разрешается прерывание по завершению приема через UART. Если разряд TXCIE и разряд общего разрешения прерываний I в регистре состояния SREG установлены в лог. 1, то разрешается прерывание по завершению передачи через UART. Если разряд UDRIE и разряд общего разрешения прерываний I в регистре состояния SREG установлены в лог. 1, то разрешается прерывание по опустошению регистра данных UART. Если разряд RXEN установлен в лог. 1, то происходит разблокирование приемника, и вывод 0 порта D становится входом UART. Если разряд RXEN содержит лог. 0, то принимающий элемент приемопередатчика UART блокируется, и вывод 0 порта D может использоваться в качестве обычного входа/выхода. Если разряд RXEN содержит лог. 0, то флаги OR и FE регистра состояния USR не могут быть установлены. Если эти флаги все же установлены, то они с помощью RXEN не сбрасываются. Если разряд TXEN установлен в лог. 1, то происходит разблокирование передатчика, а вывод 1 порта D становится выходом UART. Если разряд TXEN содержит лог. 0, то передающий элемент UART блокируется, и вывод 1 порта D может использоваться в качестве обычного входа/выхода. Если разряд TXEN во время процесса передачи устанавливается в лог. 0, то передатчик не блокируется до тех пор, пока текущий символ в сдвиговом регистре, а также символ, возможно, ожидающий на передачу в регистре UDR не будут полностью переданы. Если разряд CHR9 установлен в лог. 1, то слова данных, подлежащие передаче/считыванию имеют длину 11 бит (9 разрядов данных плюс стартовый и стоп-бит). Девятый бит из разряда ТХВ8 при передаче попадает в UCR, а при приеме – в разряд RXB8 регистра UCR. Девятый бит может быть использован для размещения дополнительных информационных данных, например, в качестве бита четности или второго стоп-бита. Если разряд CHR9 установлен в лог. 0, то слова данных, подлежащие передаче/считыванию имеют длину 10 бит (8 разрядов данных плюс стартовый и стоп-бит).

Рис. 7.3. Регистр состояния USR микроконтроллеров AVR Регистр состояния USR информирует программу пользователя о состоянии приемопередатчика UART. Флаг RXC устанавливается в лог. 1, если принятое слово данных было перенесено из сдвигового регистра в регистр UDR (без учета возможных ошибок кадрирования, которые могли возникнуть во время передачи данных). После чтения регистра UDR флаг RXC автоматически сбрасывается в лог. 0. Флаг ТХС будет установлен в лог. 1, если символ в сдвиговом регистре был передан полностью (то есть, включая стоп-бит), и из регистра UDR не ожидается новый байт данных. Флаг очень полезен в полудуплексном режиме работы, когда непосредственно после передачи необходимо переключиться в режим приема. При входе в подпрограмму обработки прерывания флаг завершения передачи ТХС аппаратно сбрасывается в лог. 0. Флаг UDRE устанавливается в лог. 1, если содержимое регистра UDR было перенесено в сдвиговой регистр. С его помощью пользователь получает уведомление о том, что приемопередатчик готов к передаче нового байта. Соответствующая подпрограмма обработки прерывания выполняется до тех пор, пока установлен флаг UDRE. Флаг UDRE сбрасывается при записи байта данных в регистр UDR. В случае сброса при включении питания флаг UDRE устанавливается в лог. 1, чтобы показать, что приемопередатчик готов к передаче нового байта данных. Флаг FE устанавливается в лог. 1 при обнаружении ошибки кадрирования. Это происходит, если при трех сканированиях стоп-бита был более одного раза обнаружен лог. 0, и тем самым стоп-бит был распознан как сигнал низкого уровня. Флаг FE сбрасывается, когда стоп-биту соответствует сигнал высокого уровня. Пользовательская программа должна постоянно проверять флаг FE перед чтением регистра UDR, чтобы можно было распознать потенциально некорректный символ в регистре приема. Флаг OR устанавливается в лог. 1, если один из символов, переданных в регистр UDR из сдвигового регистра, не был прочитан перед следующим поступившим символом. Этот флаг обновляется после считывания действительного символа из регистра UDR, поэтому пользовательская программа должна всегда проверять флаг OR после чтения регистра UDR, чтобы распознать потерю одного поступившего символа. Флаг OR сбрасывается при переносе считанного символа в регистр UDR. Настройка скорости передачи данных через UART В приемопередатчик UART встроен специальный контроллер скорости передачи данных, представляющий собой делитель частоты для определения скорости передачи данных на основании такта системной синхронизации. Скорость передачи может быть вычислена по следующему уравнению: где fBaud – скорость передачи в бодах, Ф – такт системной синхронизации; UBRR – содержимое 8-разрядного регистра UBRR (0...255). Значения, записываемые в регистр UBRR для наиболее распространенных скоростей передачи данных, представлены в табл. 7.1. Таблица 7.1. Значения регистра UBRR для наиболее распространенных скоростей передачи данных и частоты работы кварцевого осциллятора

Значения, выделенные курсивом, превышают 255, и потому не могут быть установлены в регистре UBRR, имеющем длину всего 8 разрядов. Если потребуется соответствующая скорость передачи данных, то необходимо переходить на более низкие частоты колебаний кварцевого осциллятора. |