Микропроцессоры AVR. Реферат Микроконтроллеры avr студента 3го курса Курапова Анатолия Введение

Скачать 0.65 Mb. Скачать 0.65 Mb.

|

|

Регистр GIFR Состояние внешнего прерывания определяется по регистру GIFR (рис. 3.2), который расположен в области ввода/вывода по адресу 0х003А (адрес SRAM – 0х005А).+

Рис. 3.2. Структура регистра GIFR микроконтроллеров AVR Флаг INTF1/INTF0 устанавливается в лог. 1, если возникает внешнее прерывание по сигналу на выводе INT1/INT0. При входе в подпрограмму обработки прерывания этот разряд переводится аппаратно в исходное состояние лог. 0. Регистры TIMSK и TIFR Регистр TIMSK (рис. 3.3), расположенный в области ввода/вывода по адресу 0x0039 (адрес в SRAM – 0x0059), используется для разрешения прерываний от таймеров/счетчиков.

Рис. 3.3. Структура регистра TIMSK микроконтроллеров AVR Состояние прерываний, имеющих отношение к таймерам/счетчикам микроконтроллеров AVR, определяется по регистру TIFR (рис. 3.4), который расположен в области ввода/вывода по адресу 0x0038 (адрес SRAM – 0x0058).

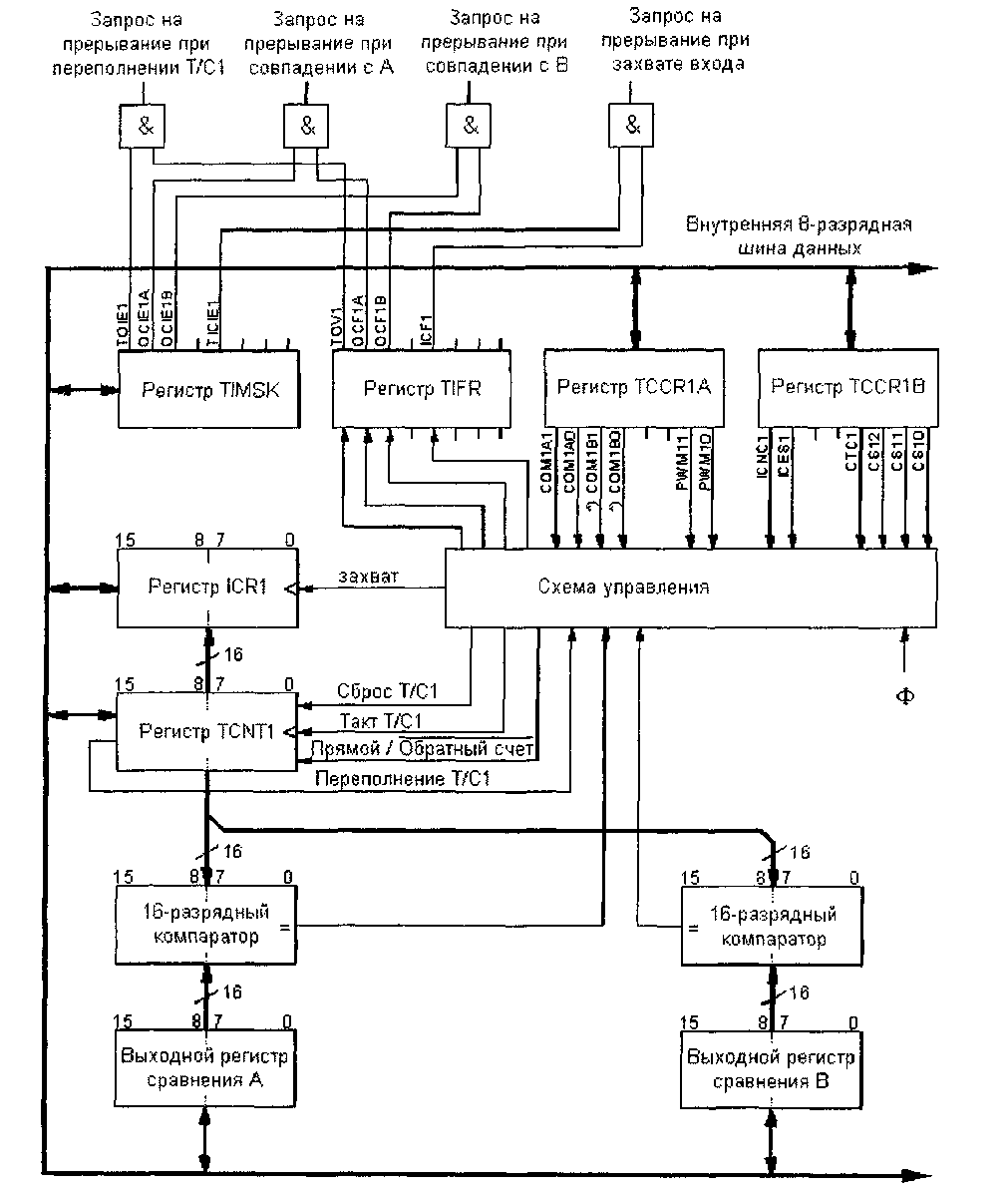

Рис. 3.4. Структура регистра TIFR микроконтроллеров AVR Когда разряд TOIE1 и разряд I в регистре состояния SREG установлены в лог. 1, то разрешено прерывание при переполнении Т/С1. В случае переполнения в регистре TIFR устанавливается флаг TOV1. Если разряд OCIE1A и разряд I в регистре состояния SREG установлены в лог. 1, то разрешено прерывание при совпадении содержимого регистра сравнения А с текущим состоянием Т/С1. В случае совпадения, в регистре TIFR устанавливается флаг OCF1 А. Если разряд OCIE1B и разряд I в регистре состояния SREG установлены в лог. 1, то разрешается прерывание при совпадении содержимого регистра сравнения В с текущим состоянием Т/С1. В случае совпадения, в регистре TIFR устанавливается флаг OCF1B. Если разряд TICIE1 и разряд I в регистре состояния SREG установлены в лог. 1, то разрешается прерывание при выполнении условия захвата. Когда возникает срабатывание по захвату, в регистре TIFR устанавливается флаг ICF1. Если разряд TOIE0 и разряд I в регистре состояния SREG установлены в лог. 1, то разрешается прерывание при переполнении таймера/счетчика Т/СО. В таком случае, в регистре TIFR устанавливается флаг TOV0. Установка в лог. 1 одного из флагов в регистре TIFR приводит к переходу по соответствующему вектору прерывания. При входе в подпрограмму обработки прерывания, флаг в регистре TIFR аппаратно сбрасывается в лог. 0. Сброс Сброс – это, по сути, одна из форм прерываний, вызывающая перезапуск микроконтроллера (аппаратная инициализация всех регистров управления и периферийных устройств и выполнение программы, начиная с адреса 0x0000). Вектор сброса всегда расположен самым первым. Возможны следующие варианты сброса: сброс при включении питания; внешний сброс – сигнал сброса подается на соответствующий вывод микроконтроллера; сброс от сторожевого таймера – микроконтроллер сбрасывается по истечению времени, заданного сторожевым таймером, если этот таймер был разрешен. "Спящие" режимы процессора Микроконтроллеры AVR допускают переход в "спящий" режим, когда происходит временное отключение генератора тактовых импульсов. В таком режиме потребление энергии сведено к минимуму, а выход из него осуществляется при получении запроса на прерывание. Переход в "спящий" режим реализуется по ассемблерной команде sleep. В случае микроконтроллеров AVR, при этом должен быть предварительно установлен в лог. 1 разряд SE (разряд 5) регистра управления MCUCR. Когда во время режима пониженного энергопотребления происходит прерывание, центральный процессор выходит из "спящего" режима, выполняет подпрограмму обработки прерывания и продолжает выполнение программы с команды, следующей после команды sleep. Если во время режима пониженного энергопотребления поступает сигнал сброса, то центральный процессор выходит из "спящего" режима и продолжает выполнение программы с команды, расположенной по адресу $000 в области команд. Для микроконтроллеров AVR может быть выбран один из двух "спящих" режимов: В ждущем режиме (Idle Mode) работа процессора приостанавливается, но таймер/счетчик, сторожевой таймер, система прерываний и тактирования остаются активными. Благодаря этому, центральный процессор может быть возвращен в обычный режим работы с помощью сторожевого таймера, таймера/счетчика или внешнего прерывания. В режиме пониженного энергопотребления (Power Down Mode) системный осциллятор (а значит и весь микроконтроллер) находится в отключенном состоянии. В таком режиме с помощью внутреннего RC-генератора колебаний может включаться лишь сторожевой таймер со своим собственным обеспечением тактовой частотой. Активный сторожевой таймер по истечении времени задержки опять переводит микроконтроллер в нормальное состояние. Если сторожевой таймер также отключен, то в нормальное состояние его может перевести только внешний сигнал сброса или внешнее прерывание. Выбор одного из "спящих" режимов в микроконтроллерах AVR осуществляется с помощью разряда SM (разряд 4) регистра управления MCUCR. Если разряд SM установлен в лог. 1, то микроконтроллер переводится в режим пониженного энергопотребления последующей командой sleep, если же разряд SM сброшен в лог. 0, то последующей микроконтроллер переводится в ждущий режим в том случае, если ранее в регистре MCUCR был установлен разряд SE. Таймеры/счетчики Таймеры/счетчики – это, наиболее часто используемые модули микроконтроллеров. С их помощью можно измерять промежутки времени и частоту, определять ширину импульсов, вычислять скорость и т.д. Хотя они и используются для измерения времени, на самом деле речь идет об обычных двоичных счетчиках. В микроконтроллерах AVR используются как 8-ми, так и 16-ти разрядные таймеры/счетчики. Разрядность определяет момент переполнения счетчика (возврат в нулевое состояние). Так, для 8-разрядного счетчика переполнение наступает, когда счет достигает 255, а для 16-разрядного – 65535. Количество таймеров/счетчиков и их разрядность в микроконтроллерах отличается в зависимости от модели, и потому в данном разделе будут рассмотрены только общие вопросы, имеющие отношение к использованию таймеров/счетчиков. Если таймер/счетчик функционирует в качестве счетчика, то он подсчитывает число импульсов, поступающих на определенный вход микроконтроллера. В этом случае соответствующий вывод должен быть сконфигурирован в инициализационной части программы как вход. В случае использования в качестве таймера, частота тактирования таймера/счетчика является производной величиной от такта системной синхронизации внутреннего кварцевого осциллятора. При этом таймеры/счетчики используют в качестве тактового сигнала разделенный такт системной синхронизации. Коэффициент деления предварительного делителя частоты может настраиваться индивидуально для каждого из таймеров с помощью мультиплексора, управляемого разрядами из регистра управления таймера/счетчика. Таймеры/счетчики микроконтроллеров AVR В микроконтроллерах AVR могут использоваться следующие таймеры/счетчики: 8-ти или 16-ти разрядный Т/С0; 16-разрядный Т/С1; 8-ми или 16-ти разрядный Т/С2. Регистры управления в этом случае называются TCCR0, TCCR1 и TCCR2 (расположены в области ввода/вывода), а режим работы и коэффициент деления частоты осциллятора определяется с помощью разрядов CSx2, CSxl и CSx0 этих регистров. К примеру, для таймеров/счетчиков Т/С0 и Т/С1 выбор режима и входного такта можно определить с помощью комбинаций разрядов, представленных в табл. 4.1. Таблица 4.1. Выбор режима и входного такта для Т/С0 и Т/С1

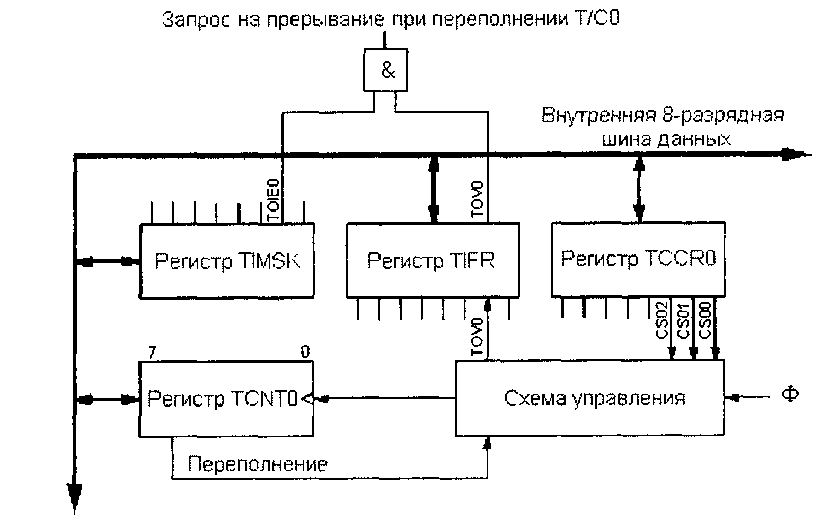

Для Т/С2 комбинации разрядов CS22, CS21 и CS20 могут иметь разное значение для различных моделей микроконтроллеров. Т/С0 Схема работы таймера/счетчика Т/С0, представлена на рис. 4.1. Как только с помощью разрядов CS00, CS01 и CS02 регистра TCCR0 (адрес 0x33 в области ввода/вывода, адрес 0x53 в SRAM) для делителя частоты будет установлена комбинация, отличная от 000, таймер/счетчик Т/С0 по каждому импульсу, поступающему на тактовый вход, начинает увеличивать на единицу содержимое регистра TCNT0 (адрес 0x32 в области ввода/вывода, адрес 0x52 в SRAM). Когда состояние счетчика в регистре TCNT0 изменяется с 0xFF на 0x00, в регистре TIFR (адрес 0x38 в области ввода/вывода) устанавливается флаг переполнения TOV0.  Рис. 4.1. Схема таймера/счетчика Т/С0 Кроме разрядов CS00, CS01 и CS02 регистра TCCR0 (разряды 0-2), никакие другие разряды этого регистра не используются. Таймер/счетчик Т/С0 хорошо подходит для оценки временных интервалов. Для этого в ходе выполнения программы в регистр TCNT0 записывается исходное значение. Затем может быть запущен Т/С0 с требуемым входным тактом. Программа ожидает появления в регистре TIFR флага переполнения TOV0, указывающего на то, что требуемое время истекло. Предположим частота системной синхронизации составляет 4 МГц, а некоторое действие должно выполняться программой каждые 0,5 с. В этом случае можно воспользоваться делением частоты на 8, что соответствует частоте тактирования 500 кГц или 2 мкс. Таким образом, на подсчет 256 тактовых импульсов счетчику потребуется 512 мкс. Это значение должно быть кратно 500 мкс, чтобы с помощью множителя 1000 в программе можно было реализовать требуемое действие в точности с периодом 500 мс. Для этого в счетчик перед началом каждого счета должно быть загружено значение 6, чтобы до переполнения выполнялся подсчет не 256, а только 250 тактовых импульсов. Т/С1 16-разрядный таймер/счетчик Т/С1 гораздо сложнее Т/С0 (рис. 4.2).  Рис. 4.2. Схема таймера/счетчика T/C1 В дополнение к счетному регистру и регистру управления, он содержит регистр захвата по входу (ICR1) и два 16-ти разрядных регистра сравнения на выходе (в некоторых моделях микроконтроллеров регистр сравнения В отсутствует). Рассмотрим назначение отдельных регистров: TCNT1 – счетный регистр (содержимое счетчика); TCCR1А – регистр управления для определения реакции выводов ОС1А/ОС1В в случае совпадения состояния счетчика в регистре TCNT1 с регистрами сравнения OCR1A/OCR1B, а также для выбора режима широтно-импульсной модуляции; TCCR1B – регистр управления для настройки делителя частоты, для разрешения подачи сигнала сброса для регистра TCNT1 и для управления захватом; ICR1 – регистр захвата по входу (при появлении на выводе ICP фронта входного сигнала, определенного как активный, текущее состояние счетчика будет перенесено в этот регистр); OCR1A, OCR1B – регистры сравнения; их содержимое постоянно сравнивается с состоянием счетчика. В случае совпадения выполняются действия, определенные регистром TCCR1A. Регистр управления TCCR1A (рис. 4.3) находится в области ввода/вывода по адресу 0x2F (адрес 0x4F в SRAM).

Рис. 4.3. Регистр TCCR1A таймера/счетчика T/C1 Разряды СОМ1А1/СОМ1А0 и СОМ1В1/СОМ1В0 определяют состояние вывода ОС1 А/ОС 1В при совпадении содержимого регистра сравнения А/В с содержимым счетчика. Возможные настройки для режима сравнения показаны в табл. 4.2. Таблица 4.2. Возможные варианты для работы в режиме сравнения

В случае активизации режима ШИМ, разряды 4…7 в регистре TCCR1А имеют значения, отличные от указанных в табл. 1.6. Когда регистр управления TCCR1A определяет работу в конфигурации широтно-импульсного модулятора, то Т/С1 работает как суммирующий и вычитающий счетчик, осуществляя циклические переходы от 0x0000 к максимальному значению ТОР, и затем снова возвращаясь к 0x0000. При запрограммированной разрешающей способности ШИМ в N разрядов значение ТОР рассчитывается как: Частота fШИМ, с которой повторяются циклы ШИМ, вычисляется по формуле: причем частота таймера/счетчика fT/ci выбирается с помощью разрядов CSIO–CS 12 регистра TCCR1B, а разрешающая способность N – с помощью разрядов PWM10 и PWM11 регистра TCCR1A. Соответствующие взаимосвязи показаны в табл. 4.3. Таблица 4.3. Выбор режима ШИМ (PWM11 и PWM10)

Когда состояние счетчика в регистре TCNT1 совпадает со значением 10 младших разрядов регистра OCR1A/OCR1B, то, в зависимости от состояния разрядов СОМ1А1/СОМ1А0 или СОМ1В1/СОМ1В0 регистра TCCR1A, вывод ОС1А/ОС1В последующим тактовым импульсом устанавливается или сбрасывается. Соответствующие взаимосвязи показаны в табл. 4.4. Таблица 4.4. Возможности выбора для режима сравнения

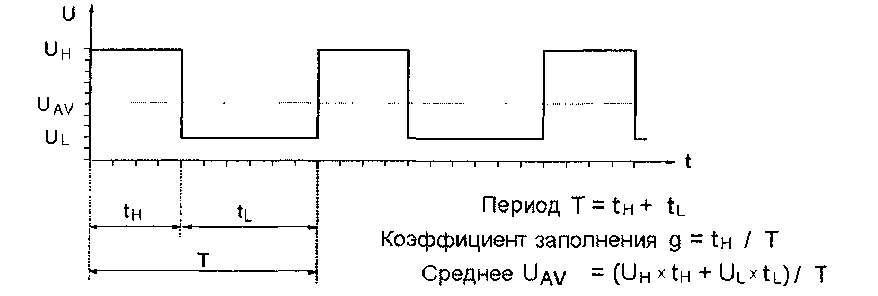

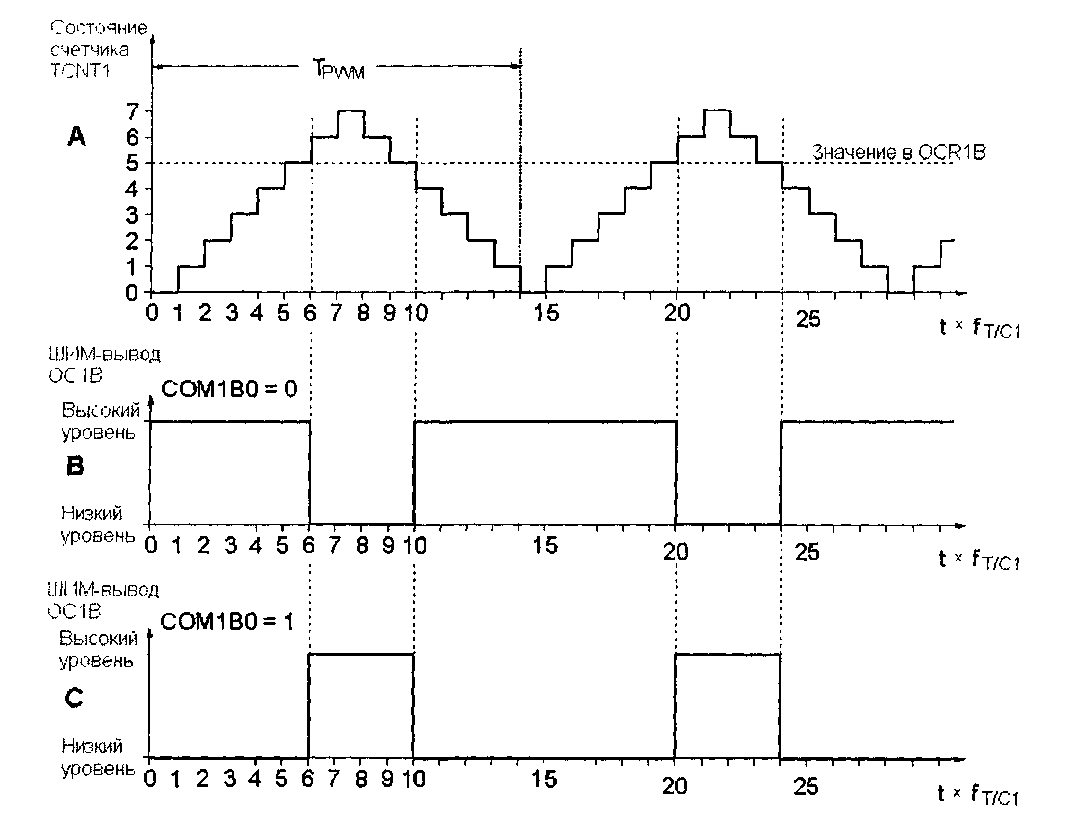

В случае неинвертирующего широтно-импульсного модулятора, коэффициент заполнения g прямоугольного сигнала на выводе с ШИМ соответствует значению n / (2N - 1), где n – значение в соответствующем регистре OCR, a N – разрешающая способность ШИМ в разрядах (рис. 4.4).  Рис. 4.4. Определение периода Т, коэффициента заполнения g и среднего арифметического UAV прямоугольных импульсов напряжения U Если регистр сравнения OCR1A/OCR1B содержит значение ТОР или 0, то на соответствующем выводе, в соответствии с правилами, представленными в табл. 4.5, постоянно поддерживаются уровень лог. 0 или лог. 1. На рис. 4.5. на примере фиктивной трехразрядной ШИМ показано формирование неинвертированного и инвертированного выходного ШИМ – сигнала на выходе ОС1В. На диаграмме А показан примерный вид ступенчатого сигнала, соответствующий состоянию счетчика TCNT1, на диаграмме В – неинвертированный, а на диаграмме С – инвертированный выходной сигнал. Продолжительность периода TPWM в этом случае вычисляется в соответствии с рассмотренным выше уравнением TPWM = TT/C1 * (2N+1 - 2). Таким образом, при N=3 период ШИМ-сигнала состоит из 14 периодов тактового сигнала fT/C1 на входе TCNT1. Таблица 4.5. Вывод ШИМ для особых случаев

Рис. 4.5. Способ формирования неинвертированных и инвертированных выходных ШИМ-сигналов В данном примере регистр сравнения OCR1B содержит значение 5. В регистре TCNT1, учитывая тот факт, что его исходное значение равно 0, значение 5 появляется после пяти тактовых импульсов. На следующем тактовом импульсе, после распознания совпадения на выводе ОС 1В устанавливается уровень лог. 0 (рис. 1.12, В). Регистр TCNT1 инкрементируется далее до тех пор, пока не будет достигнуто значение ТОР, которое при трехразрядной ШИМ составляет 7. Как только достигнуто значение ТОР, направление счета меняется на обратное, и регистр выполняет вычитание. После девятого тактового импульса, начиная от стартового значения 0, содержимое регистра TCNT1 опять совпадает с содержимым регистра OCR1B. На следующем тактовом импульсе на выходе ОС1В устанавливается уровень лог. 1. Регистр TCNT1 декрементируется далее до тех пор, пока опять не будет достигнуто значение 0. Это происходит после в общей сложности четырнадцати тактовых импульсов, считая от начального значения 0. Таким образом завершается период ШИМ-сигнала, направление счета вновь меняется на обратное и регистр TCNT1 опять выполняет сложение. Как видно на рис. 1.12 (В), "высокая" составляющая выходного сигнала составляет 6 тактовых периодов, а "низкая" – 4. Таким образом, коэффициент заполнения g = 6/10 или g = 3/5. Аналогично, диаграмма С на рис. 1.12 показывает соотношения для инвертированного выходного ШИМ-сигнала. В режиме ШИМ устанавливается флаг переполнения TOV1, если счетчик при достижении состояния 0 меняет направление счета на обратное. Это прерывание по Т/С1 при переполнении, как и при нормальной работе в режиме счетчика, вызывается в том случае, если установлен флаг общего разрешения прерываний I в регистре состояния SREG, а также флаг TOIE1 в регистре TIMSK. В соответствии с этим, прерывания при совпадении регистров TCNT1 и OCR1A/OCR1B вызываются тогда, когда в регистре TIMSK установлен флаг общего разрешения прерываний и флаг OCIE1A/OCIE1B. В отношении таймера/счетчика Т/С1 осталось рассмотреть еще регистр управления TCCR1B (адресу 0х2Е в области ввода/вывода, адрес 0х4Е в SRAM). Структура регистра TCCR1B показана на рис. 4.6.

Рис. 4.6. Регистр TCCR1В таймера/счетчика Т/С1 Разряды 0 – 2 используются для выбора частоты тактирования Т/С1 (табл. 1.5). Если разряд СТС1 установлен в лог. 1, то Т/С1 возвращается в состояние 0x0000 по импульсу такта системной синхронизации, следующего после совпадения содержимого счетчика и регистра сравнения А. При работе в режиме ШИМ этот разряд на процесс работы никак не влияет. Разряд ICES1 определяет, каким образом должна осуществляться передача состояния счетчика в регистр захвата ICR1: по нарастающему (ICES 1 = 1) или по ниспадающему фронту (ICES 1=0). Разряд ICNC1 определяет, должно ли быть активизировано подавление помех (если ICNC1 = 0, то подавление помех отключено), Для подавления кратковременных импульсов помех, которые могут привести к ошибочному запуску, входной сигнал зондируется на протяжении четырех периодов такта системной синхронизации. Только после того как будут распознаны четыре последовательных низких или высоких уровня входного сигнала, что определяется разрядом ICES1, при активном подавлении помех будет выполнена запись текущего состояния счетчика в регистр ICR1. Т/С2 Таймер/счетчик Т/С2 обычно имеет разрядность 8 бит и реализует функции сравнения на выходе и ШИМ, аналогичные Т/С1. Основная особенность Т/С2 заключается в том, что в качестве источника тактовых импульсов он может использовать генератор, независимый от системного. Для управления Т/С2 используются два регистра: ASSR (рис. 4.7) и TCCR2 (рис. 4.8).

Рис. 4.7. Регистр ASSR таймера/счетчика Т/С2 Если установить в лог. 1 разряд AS2, то в качестве источника тактовых импульсов можно использовать внешний осциллятор. Оставшиеся три разряда (0-2) используются в программах для проверки того, что данные не записываются в регистры Т/С2 в тот момент, когда они обновляются аппаратно. Такая проверка необходима по той причине, что осциллятор Т/С2 работает асинхронно по отношению к системному осциллятору.

Рис. 4.8. Регистр TCCR2 таймера/счетчика Т/С2 Установка в лог. 1 разряда PWM2 переводит Т/С2 в режим ШИМ. Назначение разрядов COM21 и СОМ20 идентично назначению разрядов COM lxl и СОМ 1x0 таймера/счетчика Т/С1 – выбор режима сравнения на выходе. Разряд СТС2 определяет, должен ли счетчик сбрасываться в нуль при совпадении его содержимого с регистром сравнения. Разряды 0 – 2 определяют частоту тактового сигнала, полученного с помощью предварительного делителя частоты такта системной синхронизации. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||