курсач ЦУ Улан. В любой области науки, техники, производства посредством деятельности и методов вычислительной техники, направленных на поощрение производительности труда человека

Скачать 1.35 Mb. Скачать 1.35 Mb.

|

|

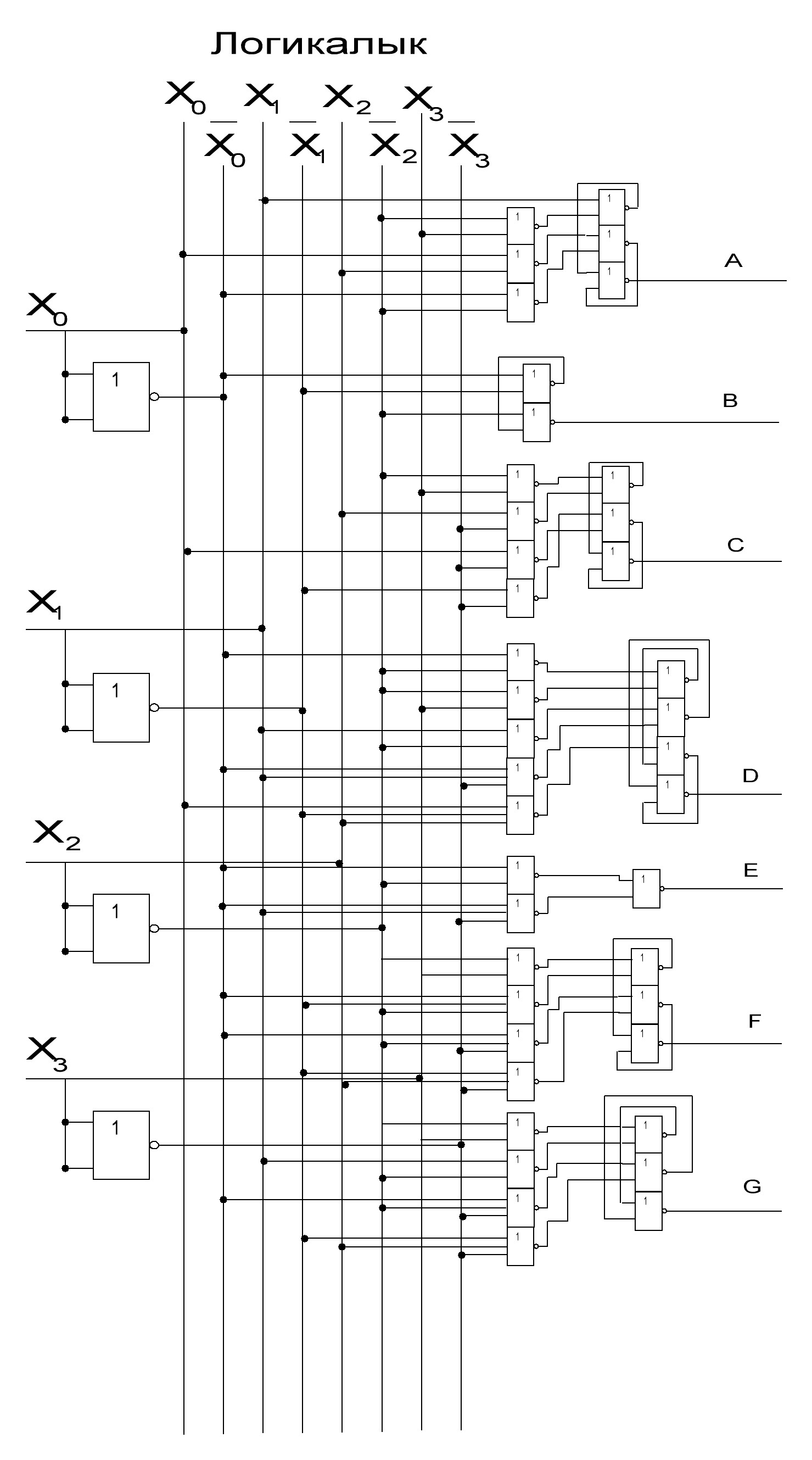

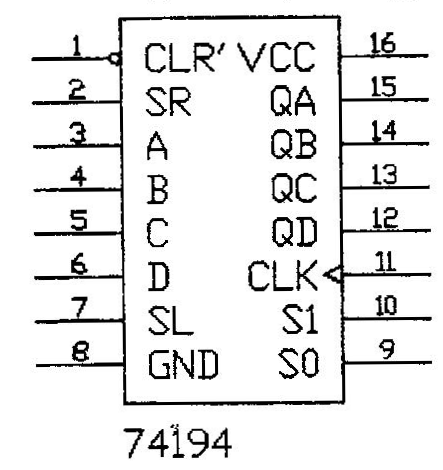

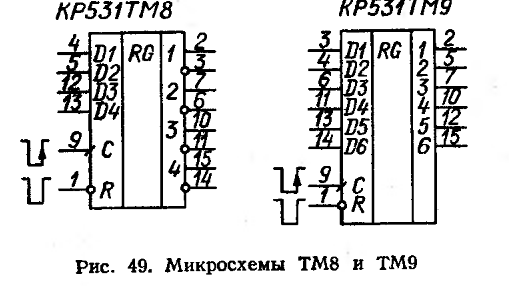

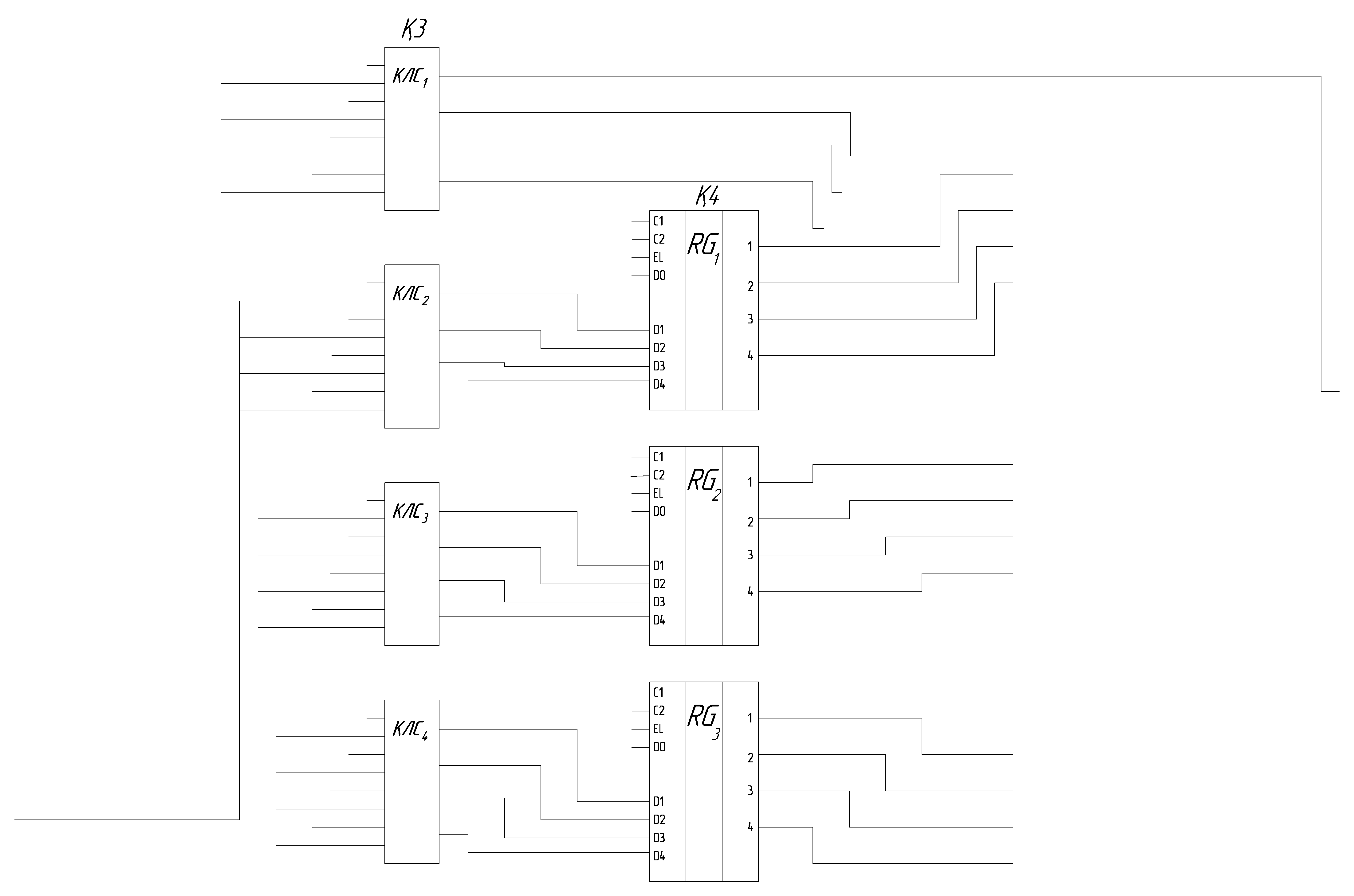

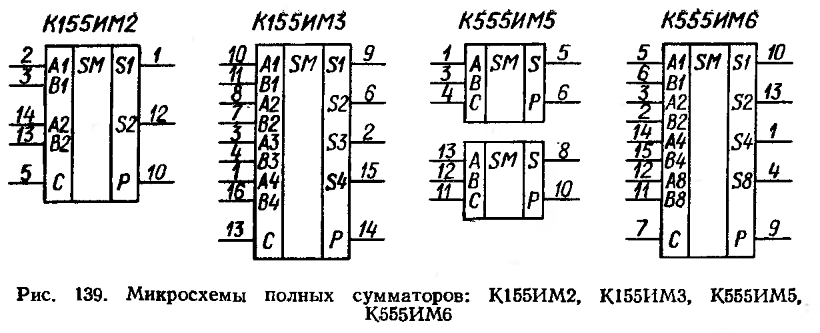

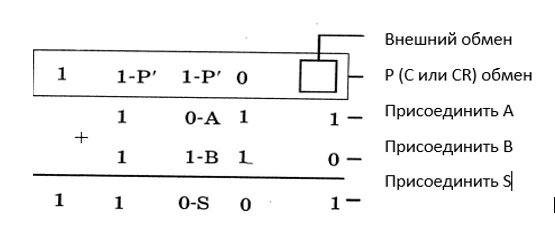

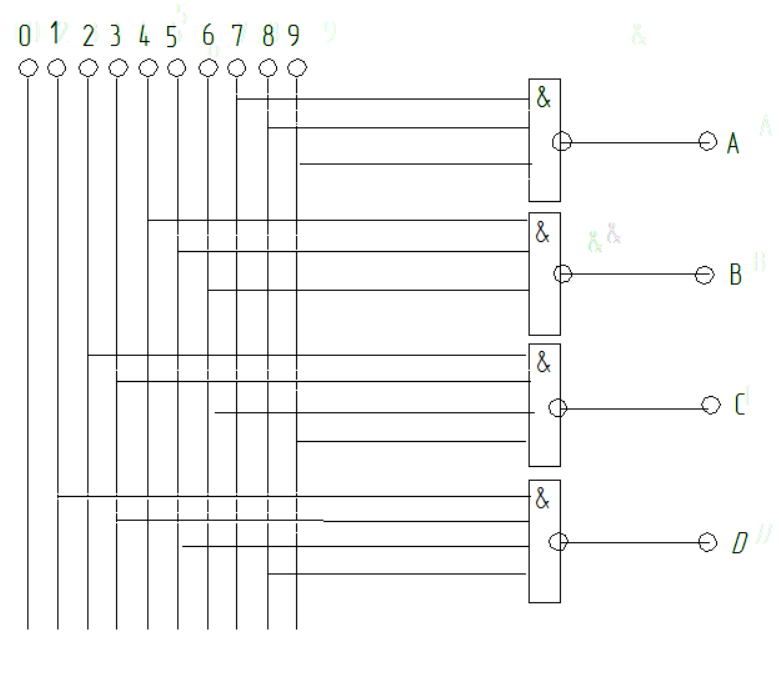

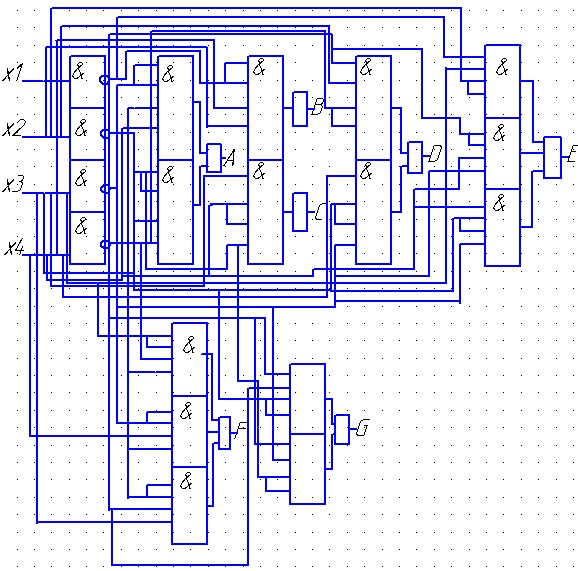

1↓ X3) Принцип работы любого преобразователя кода очень прост: например, если на вход преобразователя подается код 01111 (это число 4 в коде «8421»), то на выходе формируется код 1100110 (это тоже число 4, но сегмент в виде семидразрядного кода с управлением индикатором). При передаче такого же кода на вход индикатора (а при установке пассивного сигнала на входы ВІ, RBI и LT) загорается сегмент, показывающий число 4. Примечание: если устройство имеет несколько выходов, то помимо учета возможности повторения операции, необходимо учитывать и другие. В этом случае операция Х3Х0 (пунктирная прямая) повторяется дважды: для значений У0 и У2. Поэтому при распределении операции Х3Х0 не учитывается 2 или элемент рядом со значением У2, так как этот элемент предварительно расположен на фрагменте Схемы Для У0. Аналогичная ситуация существует и для операции Х3Х0 (подчеркивается двумя линиями), т. е. повторяется дважды при значениях У1 и У3. 5. Выбираем микросхему: К155ле1-6 шт., К155ЛЕ4-4 шт. 6. На базисе или-не нарисуем схему преобразователя кода Примечание: микросхема D2 полностью подчеркнута, т. е. это не позволяет проводам пересекаться при чтении данной схемы. Если микросхема D3, стоящая в каждом месте, подчеркивается, то она препятствует пересечению проводов и считыванию схемы.  Рисунок 9 - Логическая схема преобразователя кодов 2.5 выбор ИМС для управляющего устройства При освоении электрической схемы полной структуры множителя положительных чисел учитывалось соединение первого множителя с помощью синтезированной схемы шифратора, вводящего число А, состоящее из четырех разрядов, и условного обозначения счетчика, передающего число в из четырех разрядов. Шифровальщик реализован в курсовом работе микросхемами dd1 - dd8. Микросхемы выводятся на выходе преобразованными в двоичный код 8421(6(10) = 11110(2), код шифратора-8421). С выхода счетчика, реализованного на микросхеме к155ле, преобразует десятичное число в код 8421(5(10) = 11111(2)). Далее умножение схем производится операцией клс1, клс2, клс3, клс4, клс5, выполненной на микросхеме к155ла3. Шифратор иногда называют кодером (на английском языке coder), и он используется для преобразования десятичных чисел, набранных с клавиатуры кнопочного пульта управления, в двоичные числа. При нажатии любой кнопки клавиши на соответствующий вход шифратора выводится логический один (лог.1) подается сигнал, который на выходе преобразуется в двоично-десятичный код. Кроме того, лог. Сигнал 1 подается только на один вход в каждый момент времени. Это называется активированным входом. Такие шифраторы с одним входом активированы называются двоичными шифраторами. Каждое частичное произведение, начиная со второй строки, сдвигается влево на один разряд –эту операцию осуществляем с помощью трех параллельных регистров марки к555ир11. Полученные полупродукции постепенно суммируют с помощью трех четырехразрядных сумматоров на микросхеме к155им3, получая значение полного произведения, и полученные результаты сразу передаются в параллельно – последовательный, смещающий вправо регистр на последней микросхеме кр1533ие6. 3 выбор имс для операционнОго устройства 3.1 Выбор ИМС параллельного регистра Регистр-устройство для хранения многоразрядных двоичных чисел. Они строятся на основе триггеров (например, D-триггеров). Конечно, число триггеров в регистре определяется числом триггеров в регистре. В зависимости от порядка ввода числа в регистр, они имеют так называемый последовательный или параллельный регистр. В последовательном регистре выход каждого триггера подключен к входу следующего триггера. Разрядные значения слова в виде нескольких последовательных двоичных чисел вводятся один за другим в первый триггер при соответствующем отклонении тактового сигнала, при этом прежние введенные значения разрядов в триггерах сдвигаются с одного триггера на следующий. Конечно, для ввода всего слова потребуется столько тактового сигнала, сколько у него разрядов. На информационные входы триггеров параллельного регистра последовательно подаются значения разрядов слова, которые вводятся в регистр по одному тактовому сигналу. - Существуют также универсальные регистры, включающие два разных способа ввода. В качестве примера такого универсального регистра приведено схематическое обозначение четырехтразрядного регистра 74194 наименований   Рисунок 10 - Микросхема КР531ТМ8 и ШГБ Функция его выводов (т. е. сигналов, подаваемых на них): - VCC, GND - соединительные выходы источника питания и земли; - А, В, С, D, Е-выходы параллельного ввода информации; - QA, QB, QC , QD, QЕ-расходы регистра; - SR-ввод информации при смещении влево; - SL-выход ввода информации при движении вправо; - S1, S0-выходы сигналов, определяющих режимы работы регистра: S1 = 0, S0 = 0 - режим хранения; S1 = 0, S0 = 1 - режим сдвига влево; S1 = 1, S0 = 0-режим сдвига вправо; S1= 1, S0= 1 - режим параллельного ввода; - CLK-вывод тактового сигнала; - CLR' - выход сигнала очистки. Микросхема КР531ТМ8 – регистр, используемый для хранения информации, составленной из шестисинхронных D-триггеров.При подаче лог 0 на вход R осуществляется очистка триггеров, а при уменьшении отрицательного полярного импульса на входе С - Процесс записи.Информация на входе D1-D6, может изменяться при поступлении на вход с лог 0 или лог 1, на входе С имеет значение только при непосредственном изменении сигнала от лог 0 до лог 1. Микросхема КР531ТМ8 имеет прямой выход 1,2,3,4. В последовательном регистре выход каждого триггера подключен к входу следующего триггера. Значения разрядов слова в виде нескольких разрядных двоичных чисел вводятся один за другим в первый триггер при соответствующем отклонении тактового сигнала, при этом прежние введенные значения разрядов в триггерах сдвигаются с одного триггера на следующий. Конечно, для ввода всего слова потребуется столько тактового сигнала, сколько у него разрядов. На информационные входы триггеров параллельного регистра последовательно подаются значения разрядов слова, которые вводятся в регистр по одному тактовому сигналу. При передаче информации (информации) в виде П-разрядных комбинаций нулей и единиц установка для их приема, хранения передачиназывается.  Рисунок 11 - Электрическая схема регистра На информационные входы триггеров параллельного регистра последовательно подаются значения разрядов слова, которые вводятся в регистр по одному тактовому сигналу. 3.2 Выбор ИМС сумматора Двоичная сумма (Binary adder) - числовая единица, выполняющая арифметическую сумму двух двоичных кодов. Позже мы назовем это суммой (сумматором). Они представляют собой состав микросхемы микропроцессора и извлечения(см. тему 3.21) и являются своего рода значениями. Арифметическая сумма двоичного кода использует следующие несложные отношения: 0 + 0 = 0; 0 + 1 = 1; 1 + 0 = 1; 1 + 1=10(2часа в виде двоичного кода). Три предыдущих случая подходят для любой арифметики, а последний случай является уникальным. Два логических сигнала логическая сумма 1 равна 1 + 1 = 1, а арифметическая сумма 1 + 1 = 10(два в двоичном коде). Поэтому логическую сумму не следует путать с арифметической суммой (которая использует элемент-ИЛИ-НЕ) (которая использует сумму-сумматор).Арифметическая сумма двух многоразрядных двоичных кодов дает еще один вариант: 1 + 1+ 1=11 (число З в виде двоичного кода). Если в арифметической задаче решение двух чисел представляет собой разряд, состоящий из двух чисел, то в ответ используется меньшее число, а большее число записывается на следующую сумму разрядов. Последний называется переходным или обменным (perenos) от заданного разряда к следующему и обозначается как P, SNI или CR(от английского «carry»). В арифметической задаче 10 (1 + 1) будет 0сигнальный ответ (пишем«ноль»), а 1сигнальный перейдет в следующий разряд («один в уме»). Арифметическая сумма одного отдельно взятого разряда дает числовое значение, называемое одноразрядной суммой (сумматором)  Рисунок 12 - Сумматор на одноразрядной микросхеме К155ИМ3 Микросхема К555ИМ3 состоит из двух полных, одноразрядных суматоров, каждый из которых имеет три входа ( для передачи чисел а и века, для передачи тасмала от предыдущего разряда С) и два выхода (S - суммарный, Р - переносной). В указанном (любом) разряде выполняется арифметическая сумма трех чисел:А - число первого разрядника,В - число второго разрядника,Р - число,перешедшее из предыдущего разряда, одно разрядная сумма (сумматор) должна иметь три соответствующих входа.В решении формируются два числа: S-число суммы, Р' - число, переходящее в следующий разряд.  Рисунок 13 - Правила подключения Поэтому одноразрядная сумма (сумматор) имеет два соответствующих выхода. Рассмотрим структуру одноразрядной суммы (сумматора). На входе курсового работа числа множителей А и В преобразуются шифратором в код «на 3 больше» в двоичной системе счисления. Заданное по заданию число а т. е. первый множитель преобразуется шифратором в интегральный счетчик . А число В, т. е. второй множитель, передается в регистр. Интегральный счетчик компилируется с помощью JK-триггера в коде "более 3". Параллельный регистр скомпилирован с помощью D-триггера и по определению выберем микросхему. Все установки должны работать только на коде "более 3" в процессе работирования. Далее цифры А-6, В-5 передаются интегральному сумматору. В процессе умножения перенос выполняется последовательно от нижнего разряда к высшему. В результате включения дополнительного (GRP)устройства ИСАС (К5) для ускорения работы сумматора перенос производится параллельно, т. е. сразу же получается результат при умножении двоичных чисел. 3.3 Техническая характеристика работы устройства В первой тактовой сигнализации y0 устанавливается логический уровень «0» (исходное положение) состояния всех компонентов разработанного устройства. Команда У1 записывает в регистр R1 А = 111102 (множитель) и за этот тактический период записывает в регистр R2 число Б = 101002. У3-записывает в счетчике число 17 (в двоичном коде 1000), т. е. исходное положение счетчика. В последующие тактовые промежутки времени производится перенос состава R2 в регистр R3’. В третий промежуток времени сигналы х1 и х2 выполняют операцию умножения. За допуск операции или алгоритм последовательности операций отвечают команды x1 и x2. 1 см. таблицу. Последняя цифра умножителя и меньшего разряда определяет, что произойдет в следующий момент, то есть определяет, что и как будет выполняться устройством. Если счетчику выпадает значение «1», но X1: ST = 0 неверно, и операция продолжается по алгоритму. Логический уровень «1 " приходится на 4-й блок, где выпавшее выражение х2: R2 [0] = 1 верно и подсчет ведется по дальнейшему алгоритму. В следующем такте производит запись результата на выходе Y5-сумматора в регистр R3. Y6-смещает число на выходе сумматора в один разряд и записывает его в регистр R2. Y7-перевод числа из регистра R2 в регистр R3 с сохранением результата суммирования и смещение вправо выполняется включительно. Y8-смещение числа, полученного из регистра R3, вправо. Y9-число на складе счетчика вычитается на одну единицу, пока оно не освободится. Команды от Y0 до Y9 формируются на выходе управляющего устройства. 4 ВЫЧИСЛИТЕЛЬНЫЙ РАЗДЕЛ Таблица 6 - Перечень элементов в составе устройства

Расход шифратора  (4.1) (4.1)Время задержки сигнала  (4.2) (4.2)Расход счетчика  (4.3) (4.3)Время задержки сигнала  (4.4) (4.4)Расход преобразователя кода  (4.5) (4.5)Время задержки сигнала  (4.6) (4.6)T3 - Время задержки сигнала. ЗАКЛЮЧЕНИЕ В ходе данной курсовой работы мы работировали и ознакомились с принципом работы установки, выполняющей сложение положительных двоичных чисел, т. е. числовых сумм. В первую очередь в коде 8421 или базисе-не даны числа А (6) и В (7). С помощью шифратора (К1) я преобразовал число А и В в десятичной системе счисления в код 8421 в двоичной системе счисления. Для запоминания заданных чисел А и В потребовались счетчик (К2) и регистр (К3). Сложив числа А и В, я получил результат полной суммы. Выход должен быть не более восьми разрядов (S8), так как к555ир10 восьмиразрядный. Самый простой счетчик-это триггер, который может находиться в обоих состояниях.Затем синтезируем счетчика. Для синтеза любого счетчика важное значение имеет таблица истинности. В данном случае-это составляем таблицу в коде 8421. Я выбрал JK-триггер для сборки счетчика. Причина, по которой я выбрал JK - триггер, заключается в том, что мы можем построить t-триггер, последовательно соединяя входы J и K через этот триггер. Далее с помощью карты Вейча вычисляются функции для формирования счетчика. Для удобства пополнения карты Вейча существует свой порядок заполнения. Пользовался маркой К155ИЕ6. Микросхема К155ИЕ6 представляет собой асинхронный двоичный счетчик. Он состоит из Т-триггеров и имеет два R-входа, приведенных в 0. Далее для вывода полного результата суммы на экран я использовал регистр к155ир10 с параллельной последовательностью. В курсовом работе я собрал все микросхемы, составленные для соединения чисел А и В, и составил электрическую схему курсового работа. Устройства, необходимые для составления этой схемы: Шифратор, счетчик и регистр, я планировал зафиксировать и запомнить полученный результат и передать один разряд сумматору. Соединили параллельно-последовательный регистр сдвига вправо, постепенно выводя полное значение суммы. СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ 1 Бирюков С. А. Применение интегральных микросхем серии ТТЛ. - М.: Патриот, 1992. - 120 С. 2 Г. А. Айгараева» цифровые устройства и микропроцессорные системы " Астана -2010 3 Ж. З. Журинтаев "Схемотехника" Алматы -2011 4 Ермаганбетов К. Т.» цифровая электроника " Караганда Кар МУ - 2001 5 Шанаев О. Т. "цифровые устройства и микропроцессоры" Алматинский РЭС - 2009 6 м. Нурманов "основы Микросхемотехники" Фолиант Астана -2008 7 Калабеков Б. А. " Цифровые устройства и микропроцессорные системы» 8 Белов А. В "Самоучитель по микропроцессорной технике" 9 Безуглов Д. А., Калиенко И. В. Цифровые устройства и микропроцессоры. Учебник для ВУЗов-Ростов-на-Дону: Енкс, 2006. - 480 с 10 Жилхайдаров Е. К.» цифровые устройства и микропроцессорные системы " МПК -2012 учебное пособие. 11 Алексенко А.Г. Основы микросхемотехники. Элементы морфологии микроэлектронной аппаратуры twirpx.com/file/493881/12 Алексенко А.Г. Основы микросхемотехники.13 Элементы морфологии микроэлектронной аппаратуры https://www.studmed.ru/aleksenko-a-g-osnovy-mikroshemotehniki-elementy-morfologii-mikroelektronnoy-apparatury_191d666c26c.html14 Белов А. В "Схемотехника" 15 Г. А. Айгараева Основы микросхемотехники ПРИЛОЖЕНИЕ А  ПРИЛОЖЕНИЕ В  |