ДИИДС лаб.раб №3 Послед. схемы. Лабораторная работа 3 Часть Триггеры Цель изучение типов триггеров и их функций. Продолжительность лабораторной работы 4 часа

Скачать 1.8 Mb. Скачать 1.8 Mb.

|

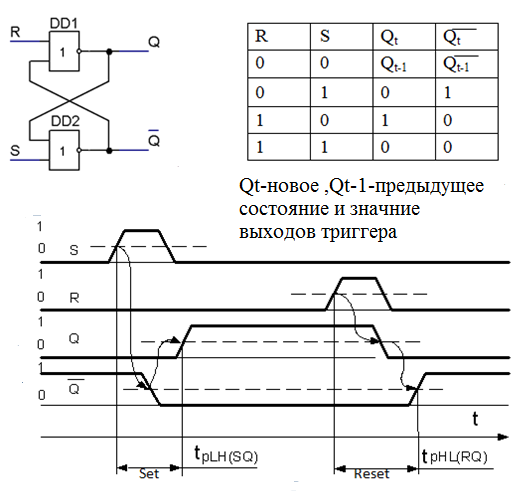

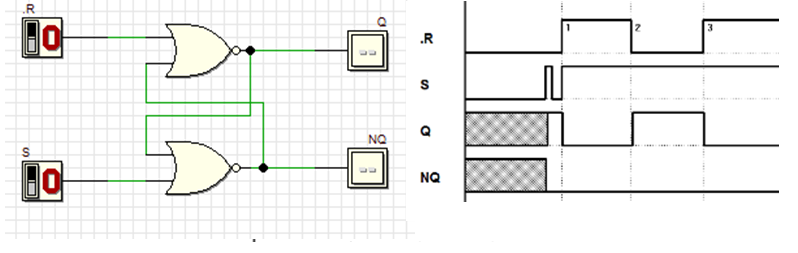

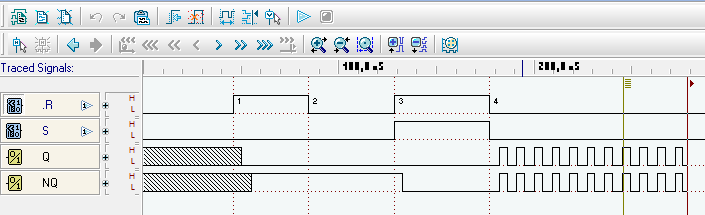

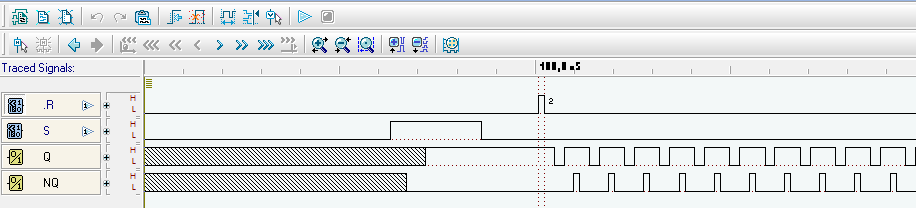

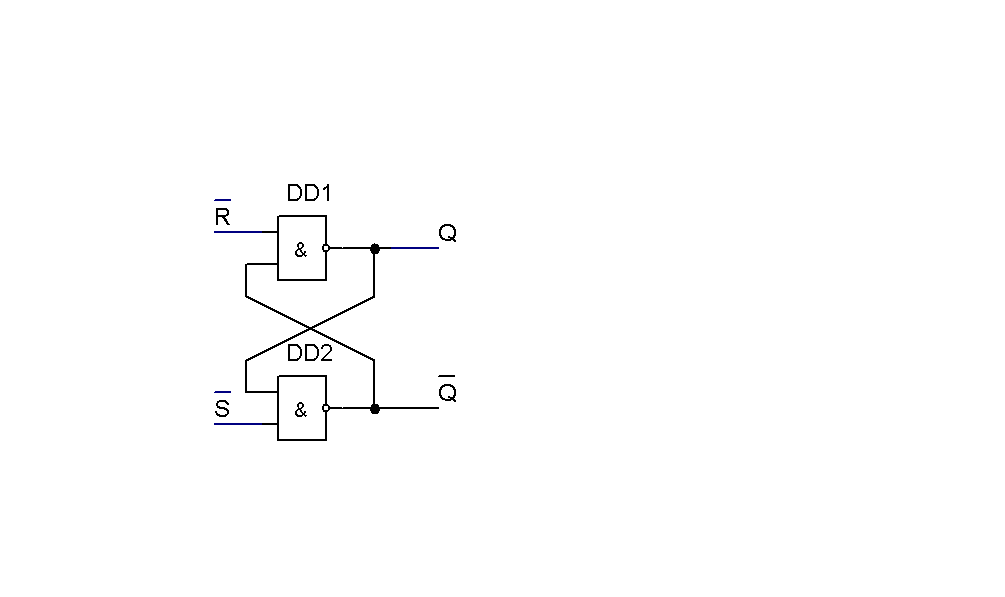

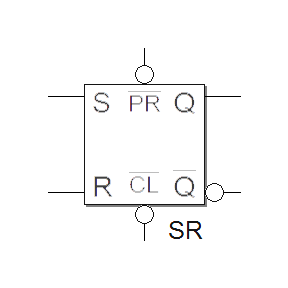

Лабораторная работа №3 Часть 1 . Триггеры Цель - изучение типов триггеров и их функций. Продолжительность лабораторной работы - 4 часа. . Изучение RS триггера. Триггер RS (RSFlipFlop, RSff) - это схема, имеющая два состояния 0 и 1 и способная их сохранять. Сигналы установки -S и сброса-R поступают на входы триггера, сигналы Q и NQ - образуются на его выходах. В простейшем случае это схема, собранная на двух логических элементах(логических вентилях,logic gates) И-НЕ (NAND) или ИЛИ-НЕ(NOR). Ниже на рис. 5.1 приведена таблица истинности RS триггера на элементах ИЛИ-НЕ ( RSNOR) и временная диаграмма его работы . Различают старое состояние триггера Qt-1 и новое Qt , где t обозначает время.  Рис. 5.1. Схема RS NOR триггера, таблица истинности и теоретическая временная диаграмма его работы На теоретической временной диаграмме рис.5.1 стрелками показаны причинно- следственные соотношения сигналов в RS триггере при установке его состояния в 1 (Set-установка ) и в состояние 0(Reset-сброс). Показаны так же задержки сигналов в схеме : TpLH - задержка перехода из состояния 0( Low) в 1( Higth), TpHL - задержка перехода из состояния 1 в 0. На рис.5.2 представлены: a) ДИИДС модель RSNOR триггера, содержащая его схему , блоки ввода и индикации сигналов и временная диаграмма моделирования, b) диаграмма в режиме подачи"запрещенной" комбинации входных сигналов, вызывающих явление "генерации" в модели, c) диаграмма в режиме подачи слишком коротких входных сигналов, вызывающих явление "метастабильности" в модели.  а) DEEDS Модель RS NOR триггера и временная диаграмма а) DEEDS Модель RS NOR триггера и временная диаграмма b) Генерация в DEEDS модели RS NOR триггера при возникновении запрещенной комбинации входных сигналов.  c) Короткие импульсы на входах ДИИДС модели RS триггера приводят к метастабильности. Рис. 5.2. RS NOR flip-flop DEEDS модели и временные диаграммы моделирования в различных режимах Задание 1.Подтвердите приведенные выше утверждения 1.1. С помощью системы моделирования DEEDS создайте проект RS NOR триггера. Обратите внимание, что начальное значение выходных сигналов триггера - X (неопределенно - см. диаграммы на рис. 1.2). 1.2. Подайте сигнал «1» на вход S, а сигнал «0» - на вход R. Тогда выходной сигнал Q=0, а на выходе NQ сигнал =1.. Это установка триггера в 1. 1.3. Подайте сигнал «1» на вход R и сигнал «0» - на вход S . На выходе Q появляется сигнал «0», на выходе NQ - сигнал «1». Это сброс триггера в 0. 1.4. Убедитесь, что когда оба входа S и R равны «0», триггер запоминает старое значение. Это режим хранения в триггере. 1.5. Если сигналы R = 1 и S = 1 одновременно подаются на входы триггера RS, то выходные сигналы будут Q = NQ = 0. Эта комбинация входных сигналов R = 1 и S = 1 называется запрещенной для RS NOR триггера . Запрет означает только то, что если после входной комбинации R = 1 и S = 1 подается комбинация R = 0 и S = 0, то появляются так называемые гонки сигналов . Состояние, в которое переходит триггер, определяется соотношением задержек в его логических элементах. Некоторые триггеры в реальной схеме перейдут в состояние «1», другие «0». Логический элемент(логический вентиль) имеет задержку распространения сигнала (Tpd). Для реальных элементов это случайная величина в диапазоне от Tpdmin до Tpdmax, определяемая нестабильностью технологического процесса их изготовления. Время установки триггера RS в новое состояние в среднем составляет Tpd_rs = 2 * Tpd_gate ( рис.1.1). Поскольку в системе моделирования DEEDS задержки экземпляров логических элементов, в том числе и вентилей ИЛИ-НЕ принимаются равными, возникает несоответствие между моделью схемы и поведением реальной схемы. Если комбинация входных сигналов R = 0 и S = 1 поступает после комбинации входных сигналов R = 0 и S = 0, состояние модели триггера RS NOR не будет устанавливаться, а периодически (период 2 * Tpd_gate) будет изменяться, несмотря на неизменность входных сигналов (так называемая генерация в модели схемы, см. рис. 1.2b). 1.6. Изучите поведение модели триггера RS NOR при одновременной подаче после запрещенных комбинаций сигналов комбинации хранения. Одновременность понимается в пределах погрешности ,меньшей чем задержка вентиля ИЛИ-НЕ , равная в ДИИДС примерно 4 нс . 1.7. Сигналы, поступающие на входы реального триггера RS, должны иметь достаточную длительность. Если длительность входных сигналов меньше минимального значения tp (min), указанного в технических данных RS-триггеров (это время обычно близко к времени задержки вентиля ), переходный процесс в реальной схеме может не достигнуть конца и функциональность схемы будет неправильной (см. рис. 5.2с - эффект метастабильности в модели). Изучите поведение DEEDS модели RS NOR триггера с короткими (1 нс) входными сигналами . 1.8. Как уже отмечалось, явление генерации в модели триггера RS объясняется равенством задержек моделей вентилей ИЛИ-НЕ. Вставьте буферный элемент (повторитель) в одну из петель обратной связи в схеме триггера RS NOR и проверьте, сохраняется ли явление генерации, и в какое состояние переходит триггер при входных комбинациях приводивших к генерации . 1.9. Сравните сгенерированное DEEDS структурное VHDL описание - RS NOR триггера с приведенным ниже поведенческим. library IEEE; use IEEE.STD_LOGIC_1164.all; entity RS_Latch is port (S,R : in STD_LOGIC; Q, Qbar : inout STD_LOGIC); end ; architecture SXEMA of RS_Latch is begin Q<= not (S or Qbar); Qbar<= not (R or Q); end; --Ниже код компоненты NOR2_gate , -- сгенерированный ДИИДС -- component NOR2_gate library ieee; use ieee.std_logic_1164.all; ENTITY NOR2_gate IS PORT( I0,I1: IN std_logic; O: OUT std_logic ); END NOR2_gate; ARCHITECTURE behavioral OF NOR2_gate IS BEGIN O <= (not (I0 or I1)); END behavioral; --Ниже код описания триггера RS _NOR _FF LIBRARY ieee; USE ieee.std_logic_1164.ALL;USE ieee.numeric_std.all; ENTITY RS_NOR_FF IS PORT( -------------------------------------->входы Inputs: i_R: IN std_logic; iiS: IN std_logic; --------------------------------------> выходы Outputs: oQ: OUT std_logic; oNQ: OUT std_logic ------------------------------------------------------ ); END ; ARCHITECTURE structural OF RS_NOR_FF IS ----------------------------------------> Components: COMPONENT NOR2_gate IS PORT( I0,I1: IN std_logic; O: OUT std_logic ); END COMPONENT; ----------------------------------------> Signals: SIGNAL S001: std_logic; SIGNAL S002: std_logic; SIGNAL S003: std_logic; SIGNAL S004: std_logic; BEGIN -- structural ----------------------------------------> Input: S001 <= i_R; S002 <= iiS; ----------------------------------------> Output: oQ <= S003; oNQ <= S004; ----------------------------------------> Component Mapping: C021: NOR2_gate PORT MAP ( S001, S004, S003 ); C023: NOR2_gate PORT MAP ( S003, S002, S004 ); END structural; Задание 2. Изучение работы RS триггера на элементах И-НE 2.1.Выполните все пункты задания 1 при моделировании работы RS триггера на элементах И-НЕ(RSNAND), схема и таблица функционирования которого представлены на рис.5.3.

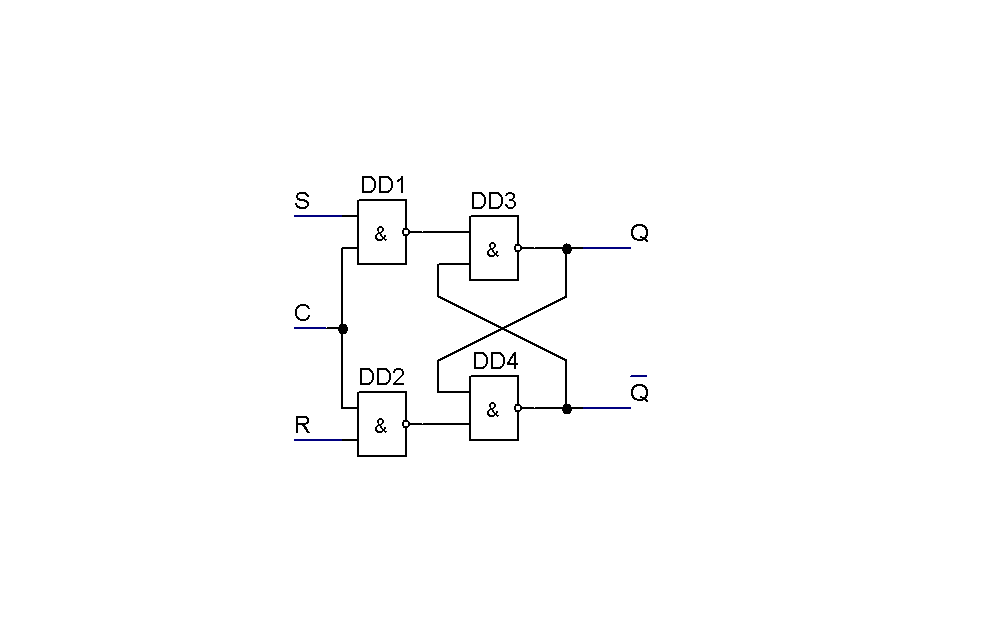

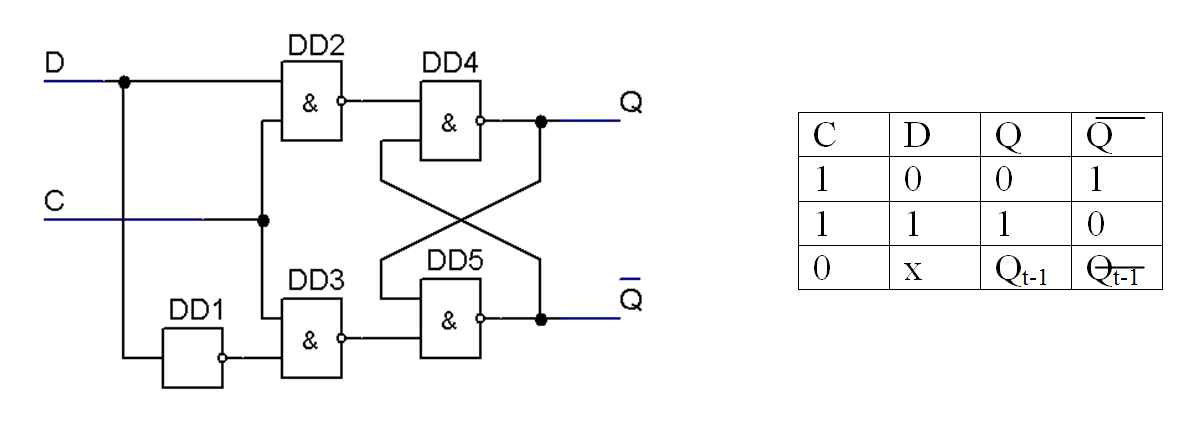

Рис. 5.3. Триггер RS NAND -схема и таблица истинности Активные уровни сигнала R и S триггера RS NAND низкие (0). Запрещенная комбинация входных сигналов: R = 0 и S = 0. 2.2. Сравните структурное VHDL описание RS_NAND, созданное DEEDS, с приведенным ниже поведенческим. library IEEE; use IEEE.STD_LOGIC_1164.all; entity RS_NAND_Latch is port (S,R : in STD_LOGIC; Q, Qbar : inout STD_LOGIC); end ; architecture SXEMA of RS_NAND_Latch is begin Q<= not (S and Qbar); Qbar<= not (R and Q); end; Задание 3. Изучить блок ДИИДС- модель RS триггера (RSLatch). . В библиотеке встроенных блоков DEEDS имеется RS триггер RS Latch (рис.5.4) с дополнительными инверсными установочными входами (PR) ̅ (preset) и сброса (CL) (clear).  Рис. 5.4. Символ блока DEEDS RS-триггер (RS Latch) 3.1.Проведите имитационный эксперимент с моделью блока DEEDS RS триггер- RS Latch. Определите, какая комбинация входных сигналов запрещена в этой модели DEEDS. Сравните приведенное ниже поведенческое VHDL описание этого триггера с генерируемым ДИИДС VHDL описанием. library IEEE; use IEEE.STD_LOGIC_1164.all; entity RS_FF is port( S,R,PR_n,CL_n: in STD_LOGIC; Q , Qbar : out STD_LOGIC); end ; architecture BEH of RS_ FF is begin process(S,R,PR_n,CL_n) if((PR_n and not CL_n ) or( not S and R))=’1’ then Q <= '0'; Qbar <= '1'; elsif ((not PR_n and CL_n ) or( S and not R))=’1’then Q <= '1'; Qbar <= '0'; end if; end process; end ; Задание 4. Изучение синхронного RS-триггера(RS-Latch , синхронный RS триггер-защелка). Для синхронизации времени переключения этого триггера( рис.5.5) предусмотрен сигнал синхронизации (тактовый ) C, активный уровень=1 которого позволяет переключать триггер в соответствии с комбинациями входных сигналов R и S (рис. 5.5).Эта схема при C = 1 ведет себя как обычный триггер RS NAND. Если C = 0, то триггер запоминает предыдущее состояние.

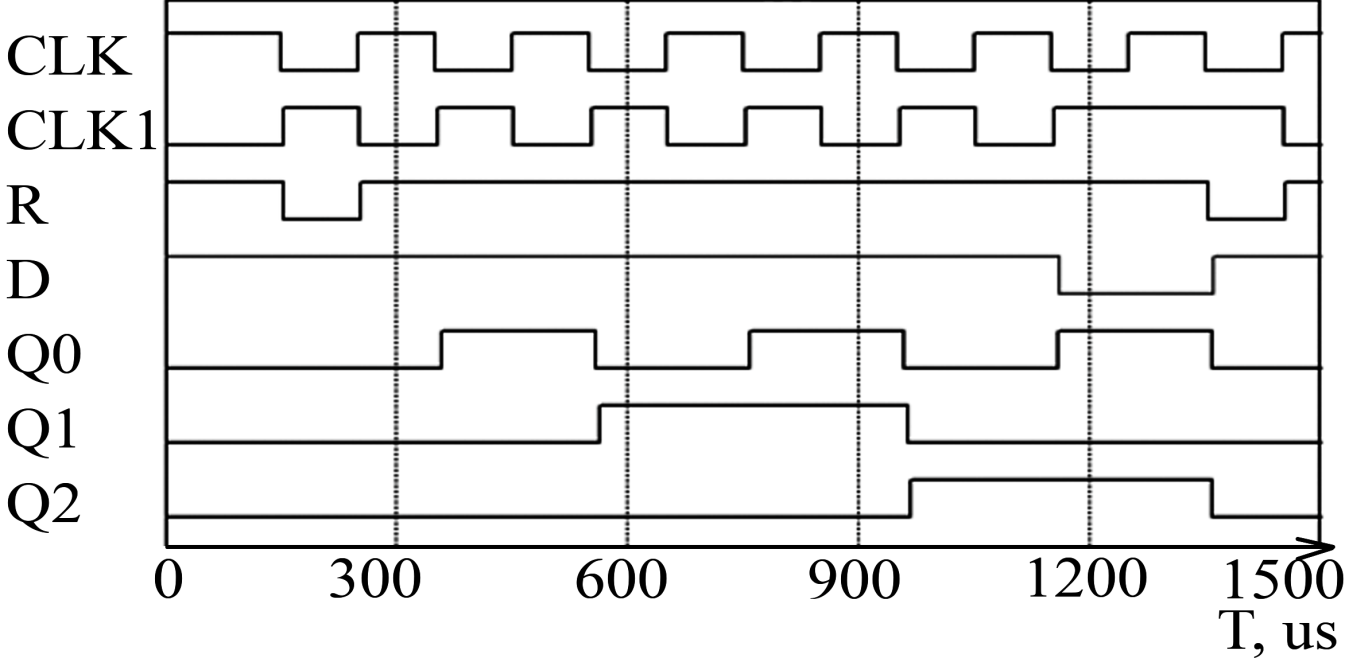

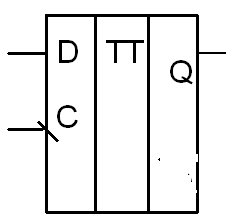

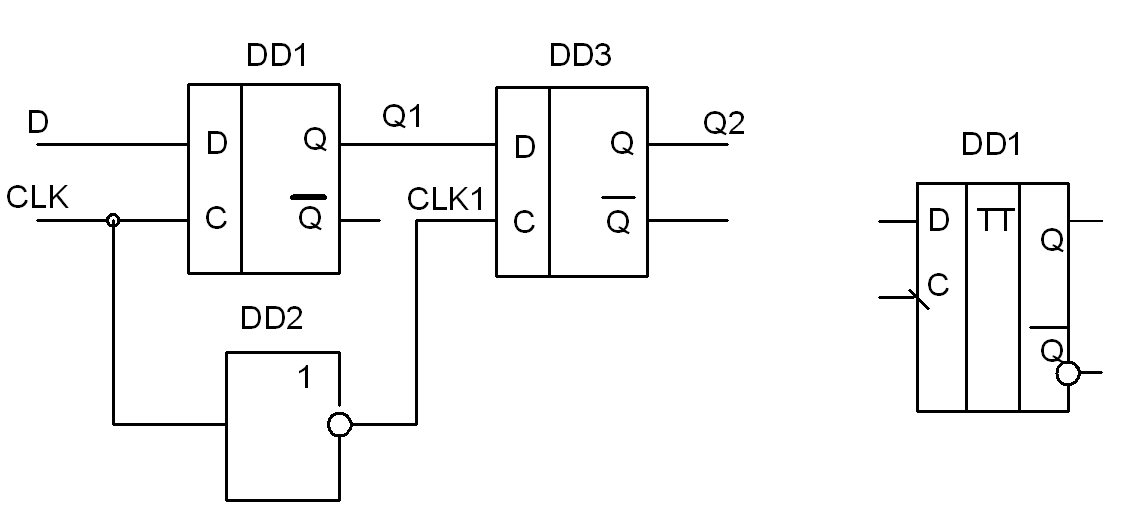

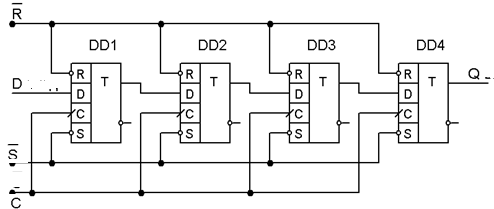

X means “any value” Рис. 5.5. Синхронный RS-триггер -защелка (RS-Latch и его таблица истинности Все время, пока синхросигнал C = 1, состояние триггера может меняться. Фактически, только в момент перехода тактового сигнала C из 1 в 0 состояние синхронного RS триггера зафиксируется . 4.1. Изучите поведение схемы синхронного RS триггера. 4.2. Изучите поведение блока DEEDS RS (Flip-Flop RS-Latch).Синхросигнал обозначен там как E ( от слова Enable-разрешающий )и добавлены установочные входы PR и CL. 4.3. Сравните временные диаграммы двух схем. 4.4. Изучите приведенный ниже код поведенческой VHDL модели синхронного RS-триггера-защелки и сравните его с кодом структурного VHDL описания , которое создает DEEDS. . library IEEE; use IEEE.STD_LOGIC_1164.all; entity RSC_ FF _Latch is port( SC,R, : in STD_LOGIC; Q , Qbar : out STD_LOGIC); end; architecture BEHAVIORAL of RSC_ FF _latch is begin process(C,S,R) begin if(C = '1') and (R = '1') and (S = '0') then Q <= '0'; Qbar <= '1'; elsif (C = '1') and (R = '0') and (S = '1') then Q <= '1'; Qbar <= '0'; end if; end process; end; Задание 5. D -Триггер защелка (статический D -Триггер ,D-Latch). Схема D- Триггера защелки и его таблица истинности показаны на рис. 1.6. Когда тактовый сигнал C = 1, триггер D является «прозрачным», и выходной сигнал Q повторяет входной сигнал D. Если поступает сигнал C=0, триггер-защелка D запоминает последнее значение входного сигнала D (рис. 5.6).  Рис.5.6. Схема D-триггера-защелки(D-Latch Flip-Flop) и таблица истинности Поведение D-триггера-защелки( D-Latch Flip-Flop) вблизи спада сигнала C имеет особенности. В это время входной сигнал D не должен изменяться. Этот интервал времени начинается от времени предустановки tsetup до момента , пока синхросигнал C не станет =0, и заканчивается с истечением времени удержания(thold) после того, как сигнал C стал =0. Если сигнал D изменяется в течение этого интервала, состояние D-триггера-защелки(D-Latch Flip-Flop) непредсказуемо. 5.1. Изучите поведение схемы рис.1.6. 5.2. Изучите поведение блока DEEDS D -триггера -защелки (Flip-Flop D-Latch). 5.3. Сравните полученные временные диаграммы двух схем. 5.4. Рассмотрите поведение модели DEEDS, если условия времени предустановки и удержания нарушены(примем их равными 1 нс.). 5.5. Сравните приведенное ниже поведенческое описание VHDL D-триггера защелки и его структурное описание, создаваемое DEEDS. library IEEE; use IEEE.STD_LOGIC_1164.all; entity D_Latch is port ( C,D : in STD_LOGIC;Q ,Qbar : out STD_LOGIC ); end ; architecture BEH of D_Latch is begin process(C,D) begin if (C = '1') then Q <= D; Qbar <= not D; end if; end process; end; Задание 6. Изучение Динамического D-триггера Динамическими называются триггера, срабатывающие от фронтов синхросигналов. На рис 5.7 представлено условное графическое изображение динамического триггера и его теоретическая временная диаграмма .   Рис. 5.7. Динамический D-триггер и его теоретическая временная диаграмма На диаграмме указаны времена задержки триггера Tplh и Tphl ,а так же необходимые для его правильной работы времена предустановки Tsetup и удержания Thold входного сигнала D относительно синхросигнала С ( рис. 5.7). 6.1.Исследуйте блок ДИИДС- динамический D- триггер. срабатывающий от положительного фронта синхросигнала С( Dpetflip-flop) и сравните временную диаграмму его работы с теоретической. 6.2. Изучите поведение модели DEEDS Dpetflip-flopпри нарушении условий времени установки и удержания (например,равных 1 пикосекунды) (модель отражает или не отражает поведение реального динамического D- триггера в таких условиях?). 6.3. Определите задержку блока DEEDSDpetflip-flop. 6.4. Сравнить поведенческое VHDL описание D- триггера, приведенное ниже и сгенерированное ДИИДС описаниеDpetflip-flop. library IEEE; use IEEE.std_logic_1164.all; entity DFFrs is -- DFFRS_1 interfase description port (D, C, R, S : in std_logic; -- input signal definition Q, Qbar : out std_logic); -- output signal definition end ; architecture BEH of DFFrs is begin process (C, R, S) begin if (S = '0') then -- priority asynchronous set Q <= '1' ; Qbar <= '0' ; elsif (R = '0') then -- priority asynchronous reset Q <= '0' ; Qbar <= '1' ; elsif (C'event and C = '1') then -- positive-edge allocation Q <= D ; -- assigning to the output signal Q the input D value Qbar <= not (D) ; end if; end process; end; Ниже на рис. 5.8 представлена схема двухкаскадного динамического D- триггера, состоящая из двух последовательно соединенных статических D- триггеров-защелок( первый из которых DD1 ведущий(master ) ,а второй-DD3 ведомый (slave ).  Рис. 5.8. Схема двухкаскадного динамического D- триггера Первая D-триггер -защелка DD1-это ведущий. Он меняет свое состояние в соответствии с входным сигналом D, когда синхросигнал CLK равен “1". В это время инвертор DD2 подает на вход синхронизации второй защелки DD3 сигнал CLK1= “0". Таким образом, триггер DD3 закрыт. На падающем фронте сигнала CLK триггер DD1 фиксирует значение сигнала Q1. С задержкой, равной времени задержки инвертора DD2, ведомый триггер DD3 открывается и сигнал Q1 передается на выход Q2. 6.6. Спроектируйте двухступенчатый D -триггер с использованием двух статических D-триггеров ДИИДС (Flip-Flop D-Latch). Получите временные диаграммы его работы. 6.7. Проанализируйте задержки и характеристики модели при коротких входных сигналах и задержке инвертора DD2 меньшей, чем задержка в ведущем триггере. Задание 7. Динамический JK-триггер (JK FF). Динамический JK триггер и его таблица переходов (триггер срабатывает на положительном фронте тактового сигнала Ck) показаны на рис. 5.8.

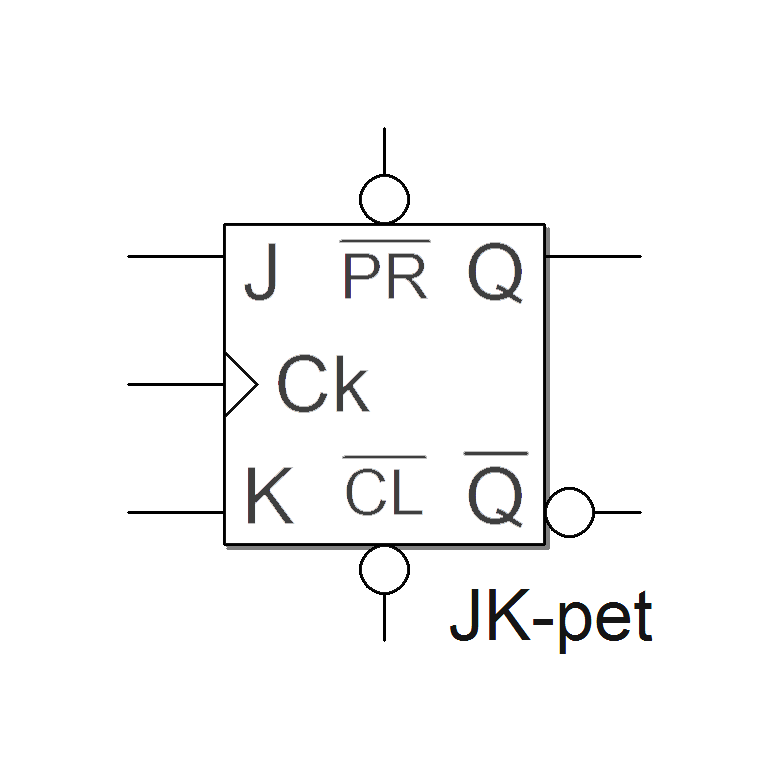

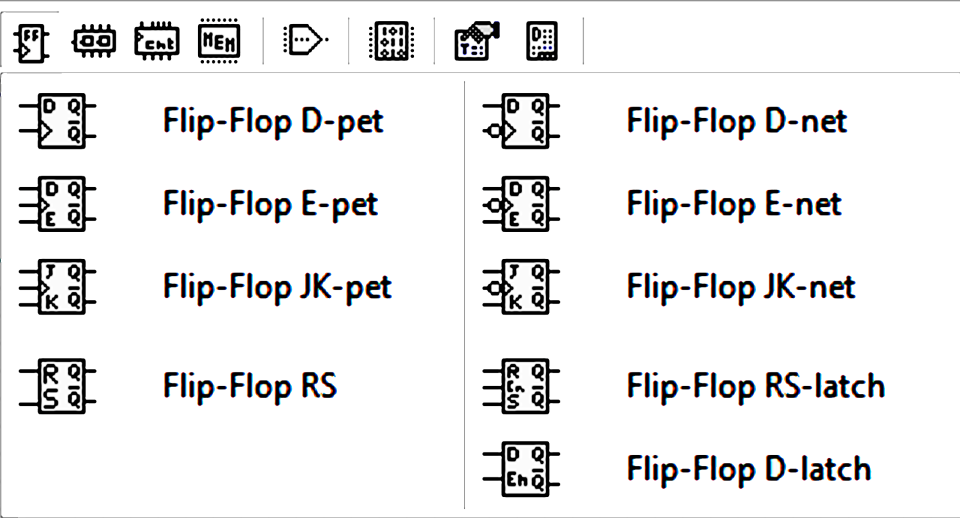

Рис. 5.8. Символ JK-триггера- блока ДИИДС JK-pet и его таблица переходов(в таблице асинхронные входы сброса Cl и установки Pr не отражены) В блоке ДИИДС JK-pet( динамический JK триггер, срабатывающий по фронту синхросигнала)имеются асинхронные инверсные входы установки в 1 (PR-preset) и сброса в 0 (CL-clear). Когда PR = 1 и CL = 1, JK триггер- блок ДИИДС JK-pet работает согласно таблице переходов по положительному (positiveedge- posedge- pet)фронту синхросигнала СК . . 7.1. Исследуйте поведение блока ДИИДС JK-pet. 7.2. Сравните полученные временные диаграммы сигналов с приведенной выше таблицей истинности. 7.3. Определите задержки ( считая с момента активного фронта тактового сигнала). 7.4. Сравните поведенческое (без входов S и R) VHDL описание JK триггера ,приведенное ниже, с сгенерированным ДИИДС описанием . library ieee;use ieee. std_logic_1164.all; entity JK_FF is PORT( J,K,C: in std_logic; Q, QB: out std_logic); end JK_FF; Architecture behavioral of JK_FF is begin PROCESS(C) variable TMP: std_logic; begin if(C='1' and C'EVENT) then if(J='0' and K='0')then TMP:=TMP; elsif(J='1' and K='1')then TMP:= not TMP; elsif(J='0' and K='1')then TMP:='0'; else TMP:='1'; end if; end if; Q<=TMP;Q <=not TMP; end PROCESS; end behavioral; Задание 8. Постройте и исследуйте схему триггера- номер варианта соответствует вашему номеру в студенческой группе. № Задание 1. Статический D триггер - защелка с дополнительным входом сброса в 0( схема из вентилей) 2. Статический D триггер - защелка с дополнительным входом установки в 1 ( схема из вентилей) 3. Динамический D триггер с дополнительным входом сброса в 0( двухступенчатая схема D-триггера с использованием двух статических D триггеров-защелок -блоков ДИИДС) 4. Т- триггер на базе D -триггера ДИИДС и логических элементов 5. Синхронный RS -триггер- защелка с установкой в 0 при появлении запрещенной комбинации входов ( схема из вентилей) 6. RS -триггер- защелка ( на базе D -триггера защелки ДИИДС с дополнительными элементами) 7. Схема RS-защелки, в которой при запрещенной комбинации входных сигналов S = 1 и R = 1 он устанавливается в 0( схема из вентилей) 8. Схема SR-защелки, в которой при запрещенной комбинации входных сигналов S = 0, R = 0 он устанавливается в 1( схема из вентилей) 9. Динамический D- триггер на базе JK-триггера ДИИДС 10. Динамический D триггер с дополнительным входом установки в 1( двухступенчатая схема D-триггера с использованием двух статических D триггеров-защелок -блоков ДИИДС) 11. Статический D триггер - защелка с дополнительными входами сброса в 0 и установки в 1 ( схема из вентилей) 12. Статический D триггер - защелка с дополнительным входом установки в 1 ( схема из вентилей) 13. Динамический D триггер с дополнительными входами установки в 0 и в 1( двухступенчатая схема D-триггера с использованием двух статических D триггеров-защелок -блоков ДИИДС) 14. Т- триггер на базе D -триггера ДИИДС и логических элементов 15. Синхронный RS -триггер- защелка с установкой в 0 при появлении запрещенной комбинации входов ( схема из вентилей) 16. RS -триггер- защелка ( на базе D -триггера защелки ДИИДС с дополнительными элементами) 17. Схема RS-защелки, в которой при запрещенной комбинации входных сигналов S = 1 и R = 1 он устанавливается в 0( схема из вентилей) 18. Схема SR-защелки, в которой при запрещенной комбинации входных сигналов S = 0, R = 0 он устанавливается в 1( схема из вентилей) 19. Динамический D- триггер на базе JK-триггера ДИИДС 20 . Динамический D триггер с дополнительным входом установки в 1( двухступенчатая схема D-триггера с использованием двух статических D триггеров-защелок -блоков ДИИДС) 21. Статический D триггер - защелка с дополнительным входом сброса в 0( схема из вентилей) 22. Статический D триггер - защелка с дополнительным входом установки в 1 ( схема из вентилей) 23. Динамический D триггер с дополнительным входом сброса в 0( двухступенчатая схема D-триггера с использованием двух статических D триггеров-защелок -блоков ДИИДС) 24. Т- триггер на базе D -триггера ДИИДС и логических элементов 25. Синхронный RS -триггер- защелка с установкой в 0 при появлении запрещенной комбинации входов ( схема из вентилей). Задание 9 . Контрольные и диагностические тесты. Задание предполагает построение контролирующего и диагностического тестов и определение места и вида неисправности в модели триггера В библиотеке SXEM_LAB_DEEDS в каталоге FAULTS/Flip_Flops имеются пронумерованные модели триггеров , некоторые с неисправностями. Необходимо для модели, соответствующей вашему номеру разработать контролирующий тест и определить исправен или нет узел . За тем надо попытаться дополнить тест новыми наборами входных сигналов , чтобы сделать тест диагностическим -попытаться неисправность локализовать и определить ее тип .. Контрольные Вопросы 1. Что такое триггер? 2. Зависит ли новое состояние триггера от предыдущего или нет? 3. В чем разница между RS и D-триггером? 4. В чем разница между синхронным и асинхронным триггером? 5. В чем разница между статическими и динамическими триггерами? 6. Какое сочетание входных сигналов RS - триггера на элементы и-не(nand) считается запрещенным? 7. Какое сочетание входных сигналов RS - триггера на элементы или-не(nor) считается запрещенным? 8. Чему равно время задержки сигнала в RS - триггере на элементах И-НЕ ? 9. При каких значениях входов J и K JK - триггер работает как T-триггер? 10. Как реализовать Т-триггер на Д-триггере? 11. Каковы ограничения по времени поступления входных сигналов на динамический триггер? 12. Каково соотношение частот входного и выходного сигналов в Т-триггере? 13. В чем разница между временами предустановки и удержания? 14. В чем заключается эффект метастабильности в триггере ? ПРИЛОЖЕНИЕ 5.1. Типы триггеров и их обозначения в DEEDS Триггеры классифицируются по типам их информационных входов и по динамическим характеристикам. Обозначения входов: R ( Сl)- вход сброса (Q = 0 при R = 1); S( Pr) - вход установки (Q = 1 при S = 1); K - вход сброса у JK-триггера (Q = 0 при K = 1, J = 0); J - установочный вход JK-триггера (Q = 1 при J = 1, K = 0); Т - счетный вход (Qt = Qt-1 при J = 1, K = 1) D - информационный вход (Data); (Q = D) C - синхронизирующий вход (Clock); E - разрешающий вход (разрешает действия других входов); Согласно типам информационных входов, триггеры называются: - RS триггер; - T триггер; - D триггер; - JK триггер; Динамические характеристики триггеров По времени реакции на входные сигналы триггеры делятся на: - асинхронные триггеры меняют свое состояние немедленно при изменении сигналов на их информационных входах( в ДИИДС они обозначаются как защелки- Latch); - синхронные триггеры меняют свое состояние только в определенный момент времени, определяемый значением синхросигнала C(в ДИИДС они обозначаются как триггера-Flip Flop); . Синхронные триггеры делятся на: - управляемые уровнем синхронизирующего сигнала (статические триггеры,защелки); - управляемые фронтом тактового сигнала ( динамические триггеры); Обозначения триггеров и их входов в ДИИДС - FlipFlop (динамический триггер); - Latch ( статический триггер-Защелка ) - PR (Preset) - вход установки (установка в 1); - CR (Clear) - вход сброса в 0. Входы установки и сброса у DEEDS моделей триггеров асинхронные. Суффикс pet ( Positive Edge Triggered) в названии динамического триггера в DEEDS означает,что он срабатывает от положительного (восходящего) фронта тактового сигнала, суффикс net - триггер управляется отрицательным (падающим) фронтом тактового сигнала. Список символов и наименований блоков DEEDS -моделей триггеров представлен на рис. 5.9.  Рис. 5.9. Символы и имена триггеров -блоков DEEDS Приложение 5.2. Шаблоны архитектур поведенческих описаний D-триггеров на VHDL D- триггер с асинхронным (левый столбец) и синхронным (правый столбец) сбросом

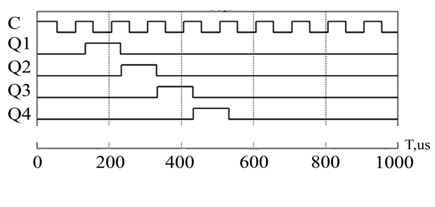

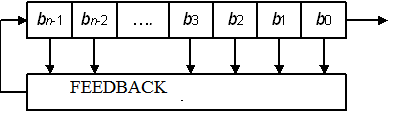

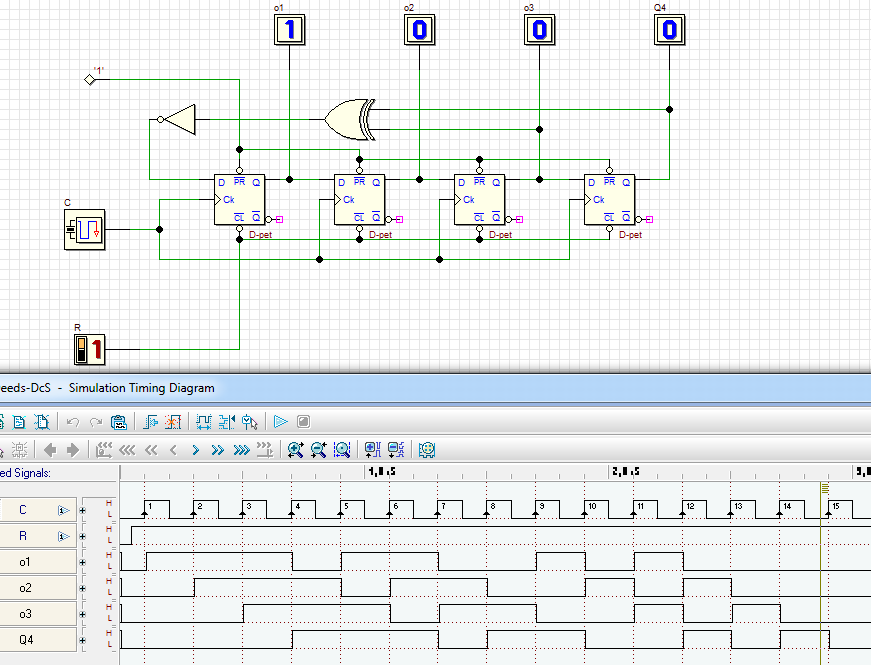

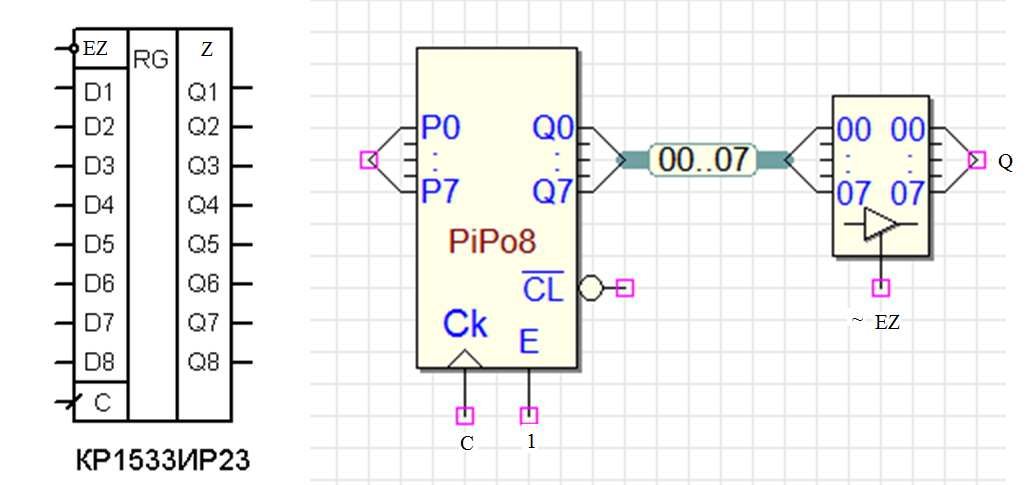

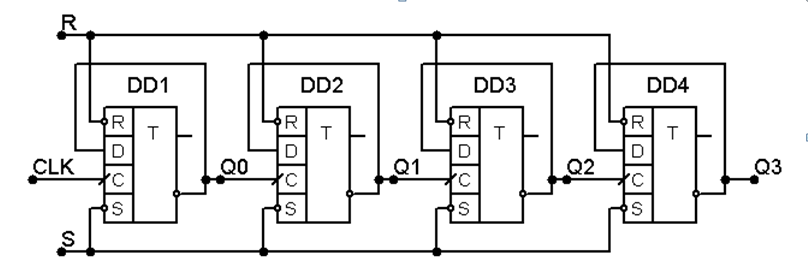

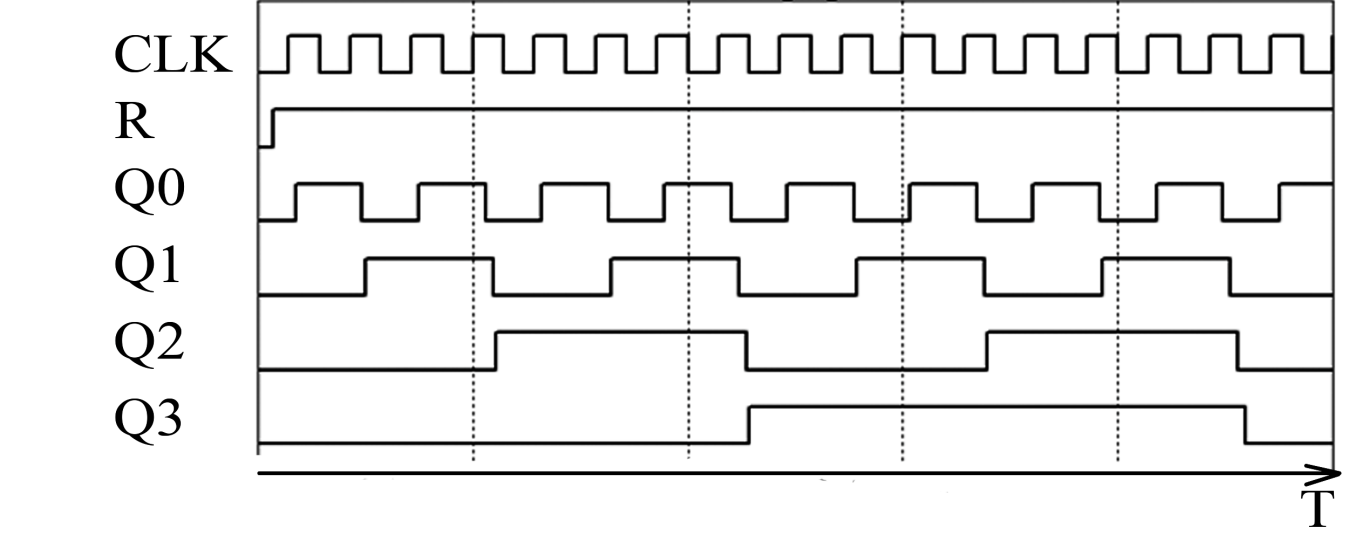

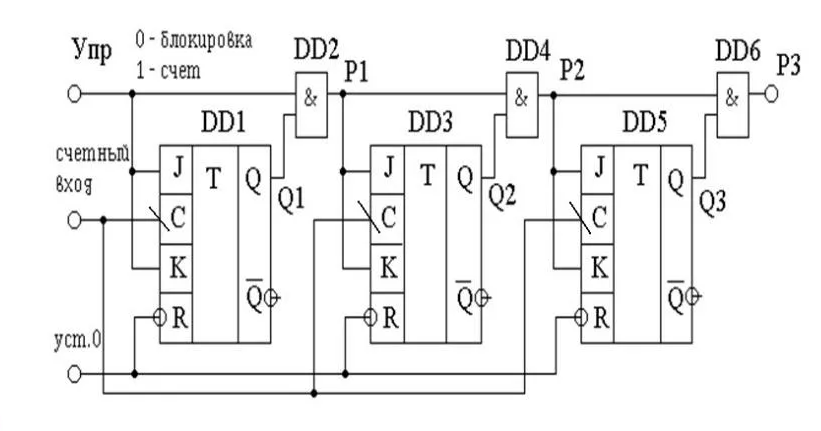

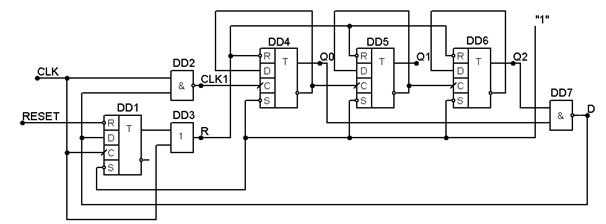

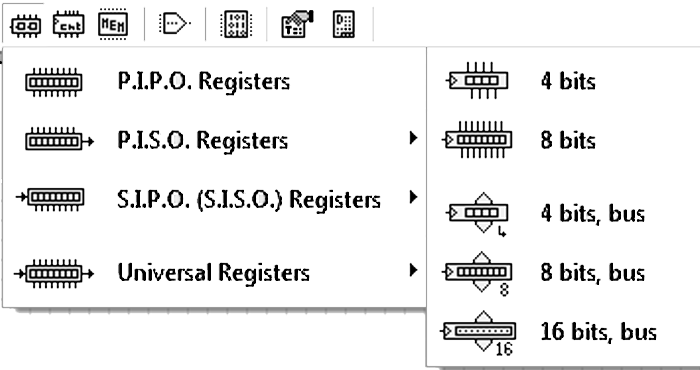

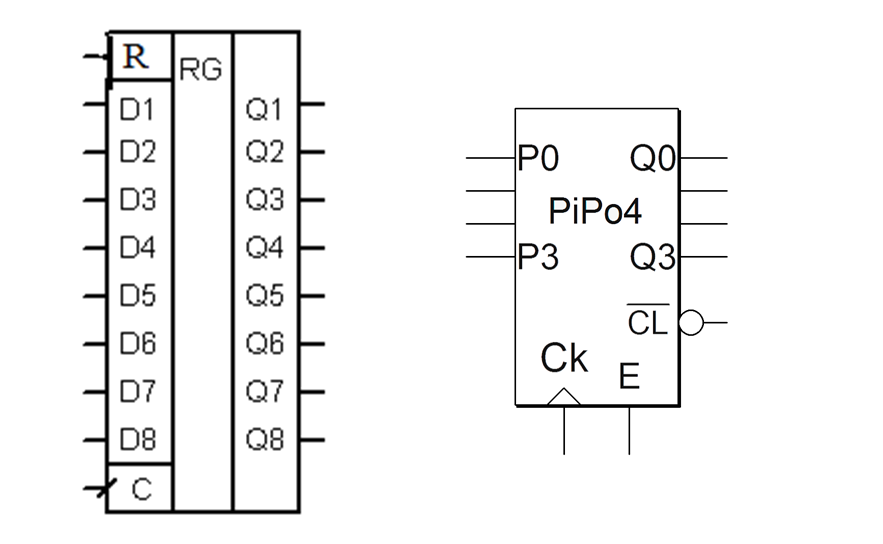

Лабораторная работа № 3 Часть 2 . Регистры и счетчики Цель-изучение регистров и счетчиков . Продолжительность лабораторной работы-4 часа. Регистр-это функциональный узел, используемый для хранения, обработки и вывода многоразрядных данных. Регистры делятся на: - параллельные регистры. Запись и чтение информации осуществляются в параллельном коде (PiPo-параллельный вход, параллельный выход). Они могут быть реализованы на триггерах защелках или динамических триггерах. - последовательные регистры (SiSo). Запись и чтение информации происходит в последовательном коде. Например сдвиговый регистр сдвигает информацию либо вправо, либо влево. Двунаправленный или реверсивный регистр сдвига может использоваться для сдвига данных в обоих направлениях. - универсальные регистры. Запись и чтение информации происходит как в последовательном, так и в параллельном коде. В DEEDS используются следующие обозначения блоков-регистров the - см.ниже): – PIPO – (Parallel Input,Parallel Output); – PISO – (Parallel Input,Serial Output); – SIPO – (Serial Input, Parallel Output); – Universal.  Задание 1. Изучение параллельных регистров. Условное графическое изображение ( УГО) 8-разрядного параллельного регистра D-триггеров и 4- разрядного регистра- блока ДИИДС PIPO4 показано на рис. 6.1. Обозначение входов и выходов: - входы данных Di (Pi), тактовый вход C(Ck), -разрешающий вход E, - сброс вход R(CL), выход Qi.  Рис. 6.1. Условные графические изображения параллельных регистров: 8-разрядного по ГОСТ и четырехразрядного PiPo4 ДИИДС) 1.1. Создайте проект с блоком ДИИДС-регистром pipo4 1.2. Запишите в регистр код , соответствующий вашему номеру в группе ( остаток от деления номера на 16). 1.3. Изучите задержки схемы. 1.4. Создайте схему 7-ми разрядного регистра ,используя два параллельных блока pipo4 с 8-разрядным входным источником сигналов - входной шиной и 8 разрядным выходным индикатором (использовать ДИИДСовские соединители ВusTap и bussplitter ). Запишите в него код в соответствии с вашим номером в группе. 1.5. Сравните сгенерированное ДИИДС VHDL описание регистра PiPo4 и поведенческое, приведенное ниже . library IEEE; use IEEE.std_logic_1164.all; entity Reg_N is generic( N: positive :=4); port ( R,E,C : in std_logic; D : in std_logic_vector(N-1 downto 0); Y : out std_logic_vector(N-1 downto 0) ); end entity; architecture BEH of Reg_N is begin process (C,R) begin if R=’1’ then Y <= (others => '0'); elsif (C'event and C = '1') then if E = '1' then Y <= D; end if; end if; end process; end; Задание 2. Сдвиговый регистр.Сдвиговые регистры содержат несколько триггеров, соединенных цепями сдвига. Схема 4-разрядного регистра сдвига вправо на динамических D-триггерах , срабатывающих по ПОЛОЖТЕЛЬНОМУ фронту синхросигнала , инверсными сигналами сброса R и установки S показана на рис. 6.2. Временная диаграмма на рис.6.3. Рис.6.2. Схема 4-x разрядного регистрасдвига вправо |