правила кирхгофа 2. Электрические цепи постоянного тока Задание 1

Скачать 0.5 Mb. Скачать 0.5 Mb.

|

|

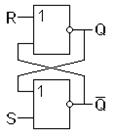

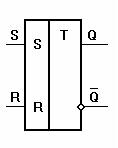

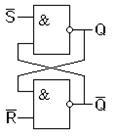

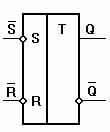

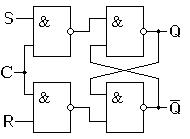

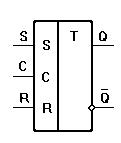

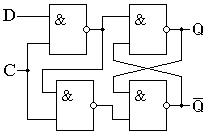

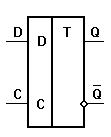

Триггеры Триггеры представляют собой устройства, обладающие двумя (или несколькими) состояниями устойчивого равновесия и способные скачком чередовать их под воздействием внешних сигналов. Это свойство триггера используется для записи и хранения двоичной информации в устройствах цифровой электроники. Триггеры выпускаются в виде интегральных микросхем. В простейшем исполнении триггер представляет собой симметричную структуру из двух логических элементов либо ИЛИ-НЕ либо И-НЕ, охваченных перекрестной положительной обратной связью. На рис. 9.1 представлены схема триггера на основе элементов ИЛИ-НЕ (а) и ее условное обозначение (б).   а) б) Рис. 9.1 Схема RS триггера на элементах ИЛИ-НЕ (а) и ее условное обозначение (б) Схема имеет два информационных входа R и S. Сигналы информационных входов определяют состояние выходов триггера и . Вход S (Set – установить англ.) позволяет устанавливать выход триггера Q в единичное состояние. Вход R (Reset – сбросить англ.) позволяет сбрасывать выход триггера Q (Quit – выход англ.) в нулевое состояние. Второй выход – инверсный. Если на выходе Q присутствует логическая единица, то на инверсном выходе будет логический ноль. И наоборот, если на выходе Q логический ноль, то на инверсном выходе – логическая единица. Такой триггер получил название RS-триггер (по названию своих входов). Триггер является аналогом реле. Если на обоих входах триггера имеются уровни логического «0» (R=0, S=0), триггер сохраняет предыдущее состояние (Qn+1=Qn). При подаче управляющего сигнала «1» на вход S (R=0), триггер принимает состояние логического «1» (Qn+1=1), а при подаче на вход R «1» (S=0) переходит в состояние «0» (Qn+1=0). Следует отметить также, что если до подачи управляющего сигнала, например, на вход R, триггер находился в состоянии логического «0», его состояние не изменится и после подачи сигнала «1» на вход R. При подаче на входы R и S одновременно уровня «1» триггер будет находиться в неопределенном (или неправильном) состоянии, поэтому такое сочетание сигналов R и S называется запрещенной комбинацией управляющих сигналов. Логическая структура, изображенная на рис.9.2, является RS – триггером на элементах И-НЕ. Схема имеет иной закон функционирования, такт переключается сигналами логического нуля, т.е. устанавливается в состояние «1» при S=0 (R=1) и сбрасывается в состояние «0» при R=0 (S=1). Запрещенная комбинация входных сигналов S=0, R=0. Если на входах триггера R=1, S=1, то сохраняется предыдущее состояние (Qn+1=Qn). Этот вариант триггера называют RS -триггером с инверсными входами ( -триггер).   а) б) Рис. 9.2. Схема RS триггера на элементах И-НЕ (а) и ее условное обозначение (б) Триггеры подразделяются по способу ввода информации на синхронные и асинхронные. Особенностью рассмотренных триггеров является то, что установка их состояния, т.е. запись информации, осуществляется с поступлением сигналов на входы. Такие триггеры называются асинхронными. В синхронных триггерах есть вход для синхронизирующего (тактового) сигнала. Запись производится сигналами на информационных входах, но с поступлением тактового сигнала на вход синхронизации (С=1). Если С=0, то триггер находится в режиме хранения записанной информации. Схема синхронного RS – триггера и ее условное обозначение приведены на рис.9.3.   а) б) Рис. 9.3. Синхронный RS – триггер: схема (а); условное обозначение (б) В RS-триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. Для приема информации по одному входу применяются D–триггеры. Они имеют информационный вход D и вход синхронизации (тактовый) С. Схема и условно-графическое обозначение D-триггера на принципиальных схемах приведено на рисунке 9.4.   а) б) Рис. 9.4. D – триггер: схема (а); условное обозначение(б)  При С=1 состояние триггера определяет сигнал на входе D , при С=0 триггер находится в режиме хранения. Состояние триггера сохраняется до тех пор, пока логический уровень на тактовом входе не изменится с 0 на 1, тогда любой из логических уровней на входе D передается на выход Q. Конкретное значение задержки определяется частотой следования импульсов синхронизации. Временные диаграммы D–триггера, поясняющие его работу, приведены на рис.9.5. При С=1 состояние триггера определяет сигнал на входе D , при С=0 триггер находится в режиме хранения. Состояние триггера сохраняется до тех пор, пока логический уровень на тактовом входе не изменится с 0 на 1, тогда любой из логических уровней на входе D передается на выход Q. Конкретное значение задержки определяется частотой следования импульсов синхронизации. Временные диаграммы D–триггера, поясняющие его работу, приведены на рис.9.5.В D-триггерах широко используют динамическое управление, т.е. в них передача информации с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса. Стрелка на условном обозначении D-триггера (рис. 9.6) указывает, что триггер реагирует на перепад уровня синхронизирующего сигнала от «0» к «1» (по фронту синхронизирующего импульса).  Триггеры являются составной частью счетчиков электрических импульсов. D-триггер с динамическим управлением можно превратить в счетный триггер (Т-триггер), если инверсный выход триггера соединить с информационным входом D, а информационные импульсы подавать на вход синхронизации С. Схема такого соединения приведена на рисунке 9.7, а. Триггеры являются составной частью счетчиков электрических импульсов. D-триггер с динамическим управлением можно превратить в счетный триггер (Т-триггер), если инверсный выход триггера соединить с информационным входом D, а информационные импульсы подавать на вход синхронизации С. Схема такого соединения приведена на рисунке 9.7, а. Счетный триггер, называемый Т-триггером, имеет один информационный вход Т (С) и два выхода: и . Как показано на временной диаграмме (рис. 9.5, б), приход очередного импульса на вход С (Т) изменяет состояние на противоположное: ,. Условное обозначение Т-триггера на рис. 9.7, в. В этом обозначении приведен второй вариант изображения динамического входа, реагирующего на перепад уровня сигнала от «0» к «1» (вместо стрелки изображен штрих). Т-триггер можно построить на основе двухступенчатого (двухтактного) RS-триггера, схема которого приведена на рис. 9.8.  Двухтактный RS-триггер состоит из двух триггеров: главного и вспомогательного. Первый, главный триггер, называют ведущим, а второй, вспомогательный, ведомым. По приходу синхронизирующего (тактового) импульса ведущий триггер за счет обратных связей устанавливается в состояние противоположное состоянию ведомого триггера. По окончании синхронизирующего импульса вспомогательный триггер переписывает информацию с выхода главного триггера, т.е. переходит в состояние, совпадающее с состоянием ведущего. В результате, как показано на диаграмме рисунка 9.7, б, период выходного импульсного сигнала τвых = 2τвх; частота, соответственно, fвых=fвх/2. Двухтактные RS-триггеры, называемые еще MS-триггерами, можно использовать для построения универсальных JK-триггеров. JK–триггер имеет два информационных входа J и K, тактовый вход С и два выхода Q и  . Условное обозначение JK-триггера показано на рисунке 9.9, а. . Условное обозначение JK-триггера показано на рисунке 9.9, а. Таблица состояний JK-триггера практически совпадает с таблицей состояний синхронного RS-триггера, но устранена неопределенность, возникающая в RS-триггере при одновременной подаче «1» на информационные входы. То есть в JK-триггере на рис. 9.9,а, разрешена одновременная подача единичных сигналов на входы J и K (J=1, K=1). В этом случае в момент окончания синхронизирующего импульса состояние триггера поменяется на противоположное ( ). Это свойство используют для получения Т-триггера, соединяя входы J и K и подавая на них «1», как показано на рис.9.9, б. Если на вход JK-триггера поставить инвертор, как показано на рис. 9.9,в, то получится D-триггер. Цифровые счетчики Цифровым счетчиком называют функциональный узел, который осуществляет счет числа поступающих не его вход импульсов, формирует результат счета в заданном коде (обычно двоичном и поэтому такие счетчики именуют двоичными) и при необходимости хранит его. Счетчики можно классифицировать по ряду признаков. В зависимости от направлениясчета различают суммирующие (с прямым счетом), вычитающие (с обратным счетом) и реверсивные (как с прямым, так и обратным счетом)счетчики. По способу организации переноса различают счетчики с последовательным, параллельным и последовательно-параллельным переносом. Конструктивно счетчики выполняются в виде совокупности ИС Т-триггеров, соответствующим образом соединенных между собой, или в виде одной ИС, содержащий многоразрядный счетчик. Двоичные счетчики могут быть построены и на синхронных или двухступенчатых D-триггерах и JK-триггерах, предварительно преобразованных в Т-триггеры. К основным параметрам двоичного счетчика относятся: 1.Модуль счета или емкость счетчика (К) – максимальное числоимпульсов, которое может быть подсчитано счетчиком. 2. Разрешающая способность или минимальное время следования (tсл.) – временной интервал между двумя счетными импульсами, при котором не нарушается надежная работа счетчика. Этот параметр определяет максимально допустимую частоту следования счетных импульсов. 3.Время регистрации (tp) – временной интервал между началом подачи счетного импульса и моментом установления результата счета, т.е. окончания самого длительного переходного процесса в счетчике. Пример 1 Составить схему последовательного суммирующего счетчика с модулем счета Kc =17 на основе триггеров К155ТВ1. Построить временную диаграмму работы схемы. Решение. При модуле счета Kc >10 в схемах параллельных счетчиков увеличивается количество дополнительных элементов и усложняются связи между триггерами, а в кольцевых счетчиках требуется большее число триггеров. При таких модулях более простой оказывается схемная реализация последовательных счетчиков. В последовательных счетчиках счетный импульс подается только на вход первого триггера, который играет роль двоичного счетчика младшего разряда. С выходом первого триггера сигнал поступает на счетный вход второго и т. д. Каждый триггер осуществляет счет импульсов в своем разряде. Количество триггеров в счетчике должно удовлетворять условию Kc 2m. При Kc=17 и m=5 Kc < 25=32. Таблица состояний триггеров имеет следующий вид:

Как видно из таблицы, счетчик из 5 триггеров имеет 32 устойчивых состояния. При Кc=17 должно быть исключено 15 избыточных состояний. После семнадцатого импульса счетчик из состояния 00001 должен перейти не в состояние 10001, а в исходное состояние 00000. Это осуществляется подачей на объединенные установочные выводы сигнала от комбинационной схемы, на выходе которой появляется низкий уровень, когда счетчик достиг состояния 00001. Схема счетчика приведена на рис. 4.1

Рис. 4.1 При переходе Т5 в состояние Q5=1 на один из входов элемента 2И-НЕ подается высокий уровень. При подаче семнадцатого импульса на выходе у него появляется низкий уровень, который подается на входы , и все триггеры переходят в состояние Q=0. Временные диаграммы приведены на рис. 4.2.

Рис. 4.2 Так как каждый триггер работает в счетном режиме, то он переходит в новое состояние по спаду управляющего импульса, которым служит входной сигнал предыдущего триггера. Благодаря элементу 2И-НЕ после семнадцатого импульса счетчик возвращается в исходное положение. Надо отметить, что считывание двоичного числа должно, как всегда, проводиться от старшего разряда к младшему, т. е. от выхода Q5 к выходу Q1. Например, после прохождения 10 импульсов показания счетчика будут 01010, что составит 0•24+1•23+0•22+1•21+0•20 =10. Задание 6 Для заданного типа суммирующего счетчика и заданного типа триггеров (таблица 6.1) выполнить следующее: 1. Выбрать необходимое число триггеров и составить таблицу состояний счетчика для заданного модуля счета. 2. Начертить схему счетчика с обозначением входов и выходов. 3. Начертить временную диаграмму работы счетчика за полный цикл работы.

|