Лекции по схемотехнике ЭВМ. Лекция Базовые понятия цифровой электроники версия для печати и pda в лекции рассказывается о базовых терминах цифровой электроники, о цифровых сигналах, об уровнях представления цифровых устройств, об их электрических и временных параметрах

Скачать 5.63 Mb. Скачать 5.63 Mb.

|

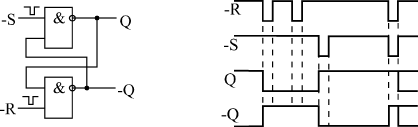

ТриггерыПринцип работы и разновидности триггеровВ основе любого триггера (англ. — "тrigger" или "flip-flop") лежит схема из двух логических элементов, которые охвачены положительными обратными связями (то есть сигналы с выходов подаются на входы). В результате подобного включения схема может находиться в одном из двух устойчивых состояний, причем находиться сколь угодно долго, пока на нее подано напряжение питания.  Рис. 7.1. Схема триггерной ячейки Пример такой схемы (так называемой триггерной ячейки) на двух двухвходовых элементах И-НЕ представлен на рис. 7.1. У схемы есть два инверсных входа: –R — сброс (от английского Reset), и –S — установка (от английского Set), а также два выхода: прямой выход Q и инверсный выход –Q. Для правильной работы схемы отрицательные импульсы должны поступать на ее входы не одновременно. Приход импульса на вход -R переводит выход -Q в состояние единицы, а так как сигнал -S при этом единичный, выход Q становится нулевым. Этот же сигнал Q поступает по цепи обратной связи на вход нижнего элемента. Поэтому даже после окончания импульса на входе -R состояние схемы не изменяется (на Q остается нуль, на -Q остается единица). Точно так же при приходе импульса на вход -S выход Q в единицу, а выход -Q — в нуль. Оба эти устойчивых состояния триггерной ячейки могут сохраняться сколь угодно долго, пока не придет очередной входной импульс, — иными словами, схема обладает памятью. Если оба входных импульса придут строго одновременно, то в момент действия этих импульсов на обоих выходах будут единичные сигналы, а после окончания входных импульсов выходы случайным образом попадут в одно из двух устойчивых состояний. Точно так же случайным образом будет выбрано одно из двух устойчивых состояний триггерной ячейки при включении питания. Временная диаграмма работы триггерной ячейки показана на рисунке.

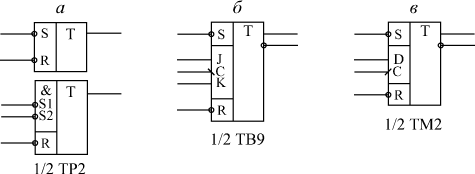

В стандартные серии цифровых микросхем входит несколько типов микросхем триггеров, различающихся методами управления, а также входными и выходными сигналами. На схемах триггеры обозначаются буквой Т. В отечественных сериях микросхем триггеры имеют наименование ТВ, ТМ и ТР в зависимости от типа триггера. Наиболее распространены три типа ( рис. 7.2):

Примером RS-триггера является микросхема ТР2, в одном корпусе которой находятся четыре RS-триггера. Два триггера имеют по одному входу –R и –S, а два других триггера — по одному входу –R и по два входа –S1 и –S2, объединенных по функции И. Все триггеры имеют только по одному прямому выходу. RS-триггер практически ничем не отличается по своим функциям от триггерной ячейки, рассмотренной ранее (см. рис. 7.1). Отрицательный импульс на входе –R перебрасывает выход в нуль, а отрицательный импульс на входе –S (или на любом из входов –S1 и –S2) перебрасывает выход в единицу. Одновременные сигналы на входах –R и –S переводят выход в единицу, а после окончания импульсов триггер попадает случайным образом в одно из своих устойчивых состояний. Таблица истинности триггера ТР2 с двумя входами установки –S1 и –S2 представлена в табл. 7.2.  Рис. 7.2. Триггеры трех основных типов

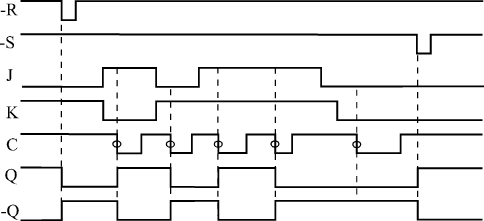

JK-триггер значительно сложнее по своей структуре, чем RS-триггер. Он относится к так называемым тактируемым триггерам, то есть он срабатывает по фронту тактового сигнала. Примером может служить показанная на рис. 7.2 микросхема ТВ9, имеющая в одном корпусе два JK-триггера со входами сброса и установки -R и -S. Входы -R и -S работают точно так же, как и в RS-триггере, то есть отрицательный импульс на входе -R устанавливает прямой выход в нуль, а инверсный — в единицу, а отрицательный импульс на входе -S устанавливает прямой выход в единицу, а инверсный — в нуль. Однако состояние триггера может быть изменено не только этими сигналами, но и сигналами на двух информационных входах J и K и синхросигналом С. Переключение триггера в этом случае происходит по отрицательному фронту сигнала С (по переходу из единицы в нуль) в зависимости от состояний сигналов J и K. При единице на входе J и нуле на входе К по фронту сигнала С прямой выход устанавливается в единицу (обратный — в нуль). При нуле на входе J и единице на входе К по фронту сигнала С прямой выход устанавливается в нуль (обратный — в единицу). При единичных уровнях на обоих входах J и K по фронту сигнала С триггер меняет состояние своих выходов на противоположные (это называется счетным режимом).

Рис. 7.3. Временная диаграмма работы JK-триггера ТВ9 Таблица истинности триггера ТВ9 представлена в табл. 7.3, а временная диаграмма работы — на рис. 7.3. Наконец, самый распространенный D-триггер занимает, можно сказать, промежуточное положение между RS-триггером и JK-триггером. Помимо общих для всех триггеров входов установки и сброса –S и –R, он имеет один информационный вход D (вход данных) и один тактовый вход C. Примером может служить показанная на рис. 7.2 микросхема ТМ2, содержащая в одном корпусе два D-триггера с прямыми и инверсными выходами.

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||