Лекции по схемотехнике ЭВМ. Лекция Базовые понятия цифровой электроники версия для печати и pda в лекции рассказывается о базовых терминах цифровой электроники, о цифровых сигналах, об уровнях представления цифровых устройств, об их электрических и временных параметрах

Скачать 5.63 Mb. Скачать 5.63 Mb.

|

|

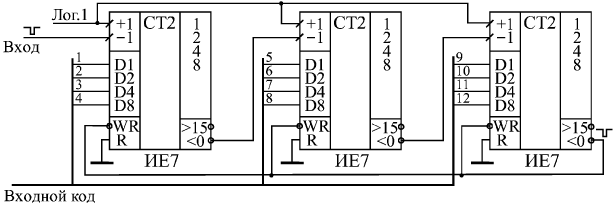

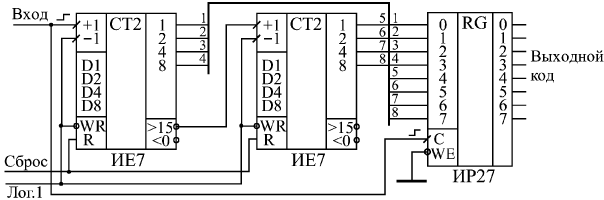

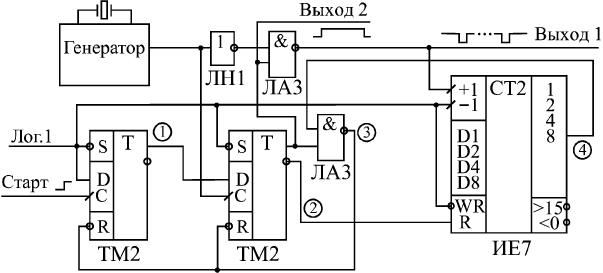

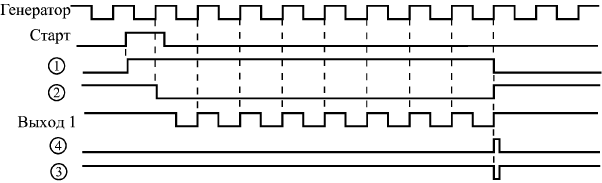

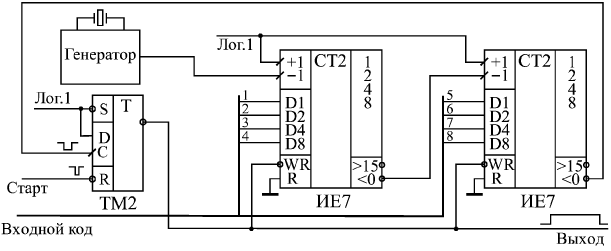

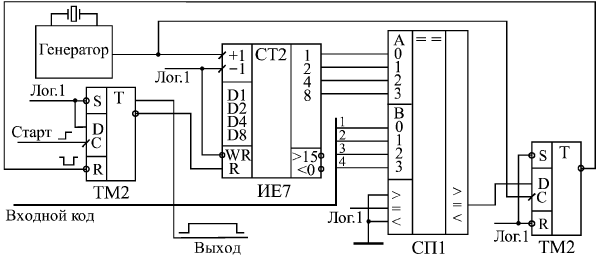

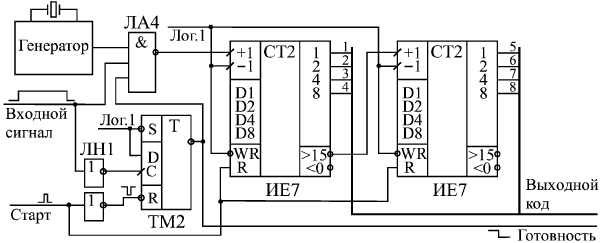

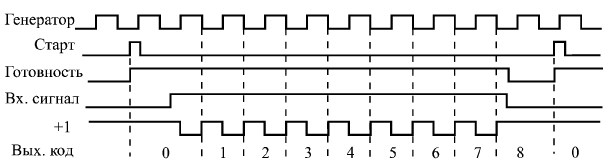

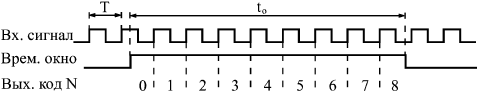

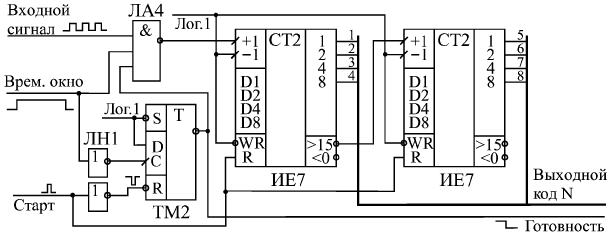

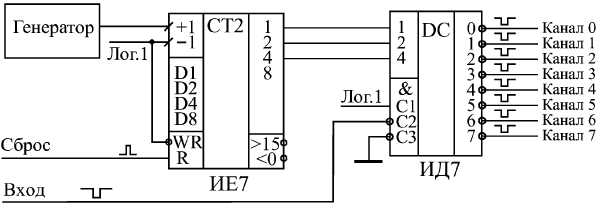

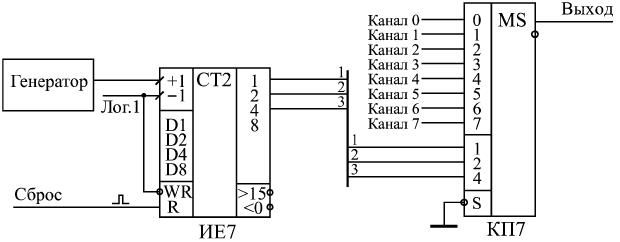

Рис. 9.12. Объединение счетчиков ИЕ7 для увеличения разрядности Объединение счетчиков ИЕ7 и ИЕ6 для увеличения разрядности (каскадирование) очень просто: нужно выходы переноса младших счетчиков (дающих младшие разряды выходного кода) соединить со счетными входами старших счетчиков (дающих старшие разряды выходного кода). На рис. 9.12 показана организация 12-разрядного счетчика на трех микросхемах ИЕ7. Этот счетчик может считать как на увеличение (прямой счет), так и на уменьшение (обратный счет). Возможны также сброс и параллельная запись в счетчики входного кода. Разряды каждого следующего счетчика будут переключаться одновременно, но с задержкой относительно переключения разрядов предыдущего счетчика. Точно так же объединяются и счетчики ИЕ6. Если нужно использовать все выходные разряды многоразрядного счетчика одновременно (как единый код), то необходимо выполнение следующего условия: T>(N – 1)*tзп+tзс, где T - период входного сигнала, N - число объединенных микросхем счетчиков, tзп - время задержки переноса одного счетчика, tзс - время задержки счета (переключения выходного кода) одного счетчика. Применение синхронных счетчиков с асинхронным переносом очень многообразно, например, они могут делить частоту входного сигнала, считать входные импульсы, формировать пачки импульсов, измерять длительность временного интервала, формировать сигналы заданной длительности, измерять частоту входных импульсов, последовательно переключать входные и выходные каналы, формировать сложные последовательности сигналов, перебирать адреса памяти и многое другое. Мы рассмотрим лишь несколько наиболее типичных примеров. В качестве делителя частоты входного сигнала синхронные счетчики с асинхронным переносом очень удобны, так как в них сочетается сравнительно высокая скорость работы с довольно простым управлением. Удобно также и то, что у них имеется режим обратного счета. На этих счетчиках можно строить делители частоты с произвольно изменяемым с помощью входного кода коэффициентом деления. Такие делители находят, например, широкое применение в аналого-цифровых системах, работающих с аналоговыми сигналами разной частоты. Простейший пример 8-разрядного делителя частоты на счетчиках ИЕ7 показан на рис. 9.13.  Рис. 9.13. Делитель частоты с коэффициентом деления, задаваемым входным кодом На вход счетчиков подается 12-разрядный управляющий код, определяющий коэффициент деления входной частоты. Этот код записывается в счетчики по сигналу переноса < 0 старшего счетчика. С этого кода начинается затем счет на уменьшение. Когда счетчики отсчитают количество входных импульсов, равное входному коду, снова выработается сигнал переноса старшего счетчика и снова запишет входной код в счетчики. Коэффициент деления будет равен (N+1) при входном коде N. Отрицательный выходной сигнал будет по форме повторять входной, но с полной задержкой переноса, а его частота будет меньше частоты входного сигнала в (N+1) раз. При 12-разрядном входном коде максимальный коэффициент деления составит 4096, а минимальный - 1. Чтобы сформулировать условия правильной работы данного делителя частоты, надо прежде всего отметить, что запись входного кода в счетчики производится отрицательным уровнем сигнала –WR, то есть передним фронтом входного отрицательного импульса, а счет производится положительным фронтом сигнала -1, то есть задним фронтом входного отрицательного импульса. Отсюда следует, что входной импульс должен быть достаточно коротким. Если он записывает код в счетчики своим передним фронтом, он уже не должен своим задним фронтом переключать счетчики по входу –1. Поэтому длительность входного отрицательного импульса не должна превышать полного времени переключения счетчиков и записи в них входного кода. В нашем случае это три задержки переноса и задержка записи в счетчик. Если частота входного сигнала - большая (к примеру, больше 10 МГц), то нормальная длительность входного сигнала получается сама собой. Но частота входного сигнала не должна быть и слишком большой, иначе в процессе записи счетчик пропустит один из входных импульсов или даже несколько. То есть от переднего фронта входного отрицательного сигнала до заднего фронта следующего входного отрицательного сигнала должны успеть сработать все счетчики и должна произойти запись в счетчики (суммарное время задержки опять же включит в себя сумму задержек переноса всех счетчиков и задержку записи). Ограничения на входную частоту будет тем жестче, чем больше счетчиков мы объединяем для увеличения количества разрядов. В данном случае важно именно количество примененных микросхем, а не количество используемых разрядов, как у асинхронных счетчиков. Для решения часто встречающейся на практике задачи подсчета количества пришедших входных импульсов необходимо всего лишь объединить несколько микросхем счетчиков с целью получения требуемого числа разрядов. Например, если количество входных импульсов не превышает 255, то достаточно двух 4-разрядных счетчиков, если оно не больше 65535, то надо объединить уже четыре 4-разрядных счетчика. Так как в этом случае нас интересуют все выходные разряды одновременно, необходимо обеспечить, чтобы за период входных импульсов переключались все микросхемы счетчиков. Обеспечить одновременность переключения всех выходных разрядов счетчика при счете входных импульсов можно, как и в случае асинхронных счетчиков, за счет включения выходного параллельного регистра, срабатывающего по фронту (рис. 9.14). Данное решение довольно универсально, оно может использоваться в самых разных ситуациях, когда необходим весь выходной код счетчика целиком. Код на выходе регистра будет удерживаться в течение всего периода входных импульсов. Правда, быстродействие счетчика от этого не повышается.  Рис. 9.14. Включение выходного регистра для одновременного пе- реключения разрядов выходного кода Формирование пачки (группы) входных импульсов с заданным количеством импульсов - довольно распространенная задача. Например, такое формирование необходимо при организации обмена информацией в последовательном коде. Если в качестве преобразователя параллельного кода в последовательный используется 8-разрядный регистр сдвига, то ему в качестве синхросигнала необходима пачка из восьми импульсов. Схема формирователя такой пачки импульсов показана на рис. 9.15, а временная диаграмма ее работы - на рис. 9.16.  Рис. 9.15. Формирователь пачки из восьми импульсов По сигналу "Старт" (положительный фронт) перебрасывается первый триггер, использующийся для синхронизации. По первому положительному фронту тактового сигнала с генератора перебрасывается второй триггер, разрешающий прохождение импульсов с генератора на выход через элемент 2И-НЕ, а также разрешающий работу счетчика ИЕ7.  Рис. 9.16. Временная диаграмма работы формирователя пачки им- пульсов После того как на Выход 1 схемы пройдут восемь отрицательных импульсов, на выходе 8 счетчика выработается единица, что приведет к сбросу в исходное нулевое состояние обоих триггеров (коротким отрицательным импульсом на выходе нижнего по рисунку элемента 2И-НЕ) и к запрету прохождения импульсов на выход. Работа формирователя возобновится после следующего сигнала "Старт". На основе счетчиков довольно просто строить формирователи временных интервалов с длительностью, задаваемой внешним кодом. Такие формирователи находят широкое применение, например, в различных измерительных устройствах. Так как формирователь временных интервалов обычно работает с кварцевым тактовым генератором, возможны два подхода к его построению. При первом подходе входной стартовый импульс синхронизируется с тактовым сигналом, в результате чего выходной импульс заданной длительности может начаться не сразу после стартового импульса, а через какое-то время, меньшее периода тактового сигнала. Длительность формируемого временного интервала в этом случае абсолютно точно известна и будет равна целому числу периодов тактового генератора. Именно так было сделано в предыдущей рассмотренной нами схеме (сигнал "Выход 2" на рис. 9.15 как раз и будет формируемым сигналом с заданной длительностью). При втором подходе выходной импульс заданной длительности начинается сразу после входного сигнала, но длительность его может отличаться от заданной на какое-то время, меньшее периода тактового сигнала. Иногда это более приемлемое решение, особенно при больших длительностях выходного сигнала, значительно больших, чем период тактового сигнала. Схема формирователя временного интервала, построенного в соответствии с этим вторым подходом, показана на рис. 9.17. Работа схемы начинается с подачи короткого отрицательного импульса –Старт. Он перебрасывает триггер, который разрешает работу счетчиков снятием сигнала параллельной записи –WR. По отрицательному фронту входного сигнала начинается положительный выходной сигнал заданной длительности. Счетчики начинают считать на уменьшение кода по положительным фронтам тактового сигнала с генератора. Когда они досчитают до нуля, вырабатывается сигнал переноса, перебрасывающий триггер в исходное состояние. Работа схемы возобновится после следующего сигнала –Старт.  Рис. 9.17. Формирователь временного интервала Если входной код равен 1, то длительность выходного сигнала составит от Т до 2Т, где Т - период тактового сигнала. Если входной код равен N (до 255), то длительность выходного сигнала составит от NT до (N+1)T в зависимости от момента прихода входного сигнала по отношению к тактовому сигналу. Абсолютная погрешность выдержки длительности выходного сигнала в любом случае не превышает периода тактового сигнала Т. Эту же самую схему вполне можно использовать в тех случаях, когда необходимо получить убывающий код от заданного числа до нуля. При этом сигнал с выхода триггера будет только внутренним сигналом схемы, а выходными сигналами схемы будут выходные разряды счетчиков. Иногда бывает необходимо сформировать импульс требуемой длительности, но одновременно иметь не убывающий, а возрастающий код (от нуля до заданного значения). В таком случае схема получится несколько сложнее. Пример возможного решения формирователя импульса заданной длительности показан на рис. 9.18.  Рис. 9.18. Формирователь импульса заданной длительности (вариант с нарастающим кодом) По сигналу "Старт" (положительный фронт) перебрасывается левый по рисунку триггер, который начинает формировать выходной сигнал и разрешает работу счетчика (снимая сигнал сброса R). Счетчик считает на увеличение по положительным фронтам тактового сигнала от нуля. Когда выходной код счетчика достигает величины входного кода, перебрасывается правый по рисунку триггер, завершающий процесс формирования выходного сигнала. Счетчик сбрасывается в нуль, правый триггер по следующему фронту попадает в исходное состояние. Новый цикл начнется с приходом следующего сигнала "Старт". Если входной код равен 1, то длительность выходного сигнала составит от Т до 2Т, где Т - период тактового сигнала генератора. Если входной код равен N, то длительность выходного сигнала будет равна от NT до (N + 1)T в зависимости от временного сдвига между сигналом "Старт" и тактовым сигналом. В любом случае абсолютная погрешность времени выдержки выходного сигнала не превысит периода тактового сигнала Т. Счетчики также широко применяются в различных измерителях длительности входных сигналов. Для этого они отсчитывают импульсы тактового кварцевого генератора в течение длительности входного сигнала. После окончания входного сигнала в счетчике остается код, пропорциональный длительности этого сигнала. Пример практической схемы такого измерителя показан на рис. 9.19.  Рис. 9.19. Измеритель длительности входного сигнала  Рис. 9.20. Временная диаграмма работы измерителя длительности входного сигнала Работа схемы начинается по короткому управляющему импульсу "Старт", который сбрасывает счетчик в нуль и переводит всю схему в режим счета, разрешая прохождение сигнала с тактового генератора на вход +1 счетчика при положительном входном сигнале. С началом входного сигнала импульсы с генератора поступают на вход счетчика, и счетчик их считает. После окончания входного сигнала поступление импульсов на вход счетчика прекращается, триггер перебрасывается в исходное состояние и сообщает отрицательным фронтом на своем инверсном выходе о готовности выходного кода (сигнал "Готовность"). Работа схемы возобновится по следующему импульсу "Старт". Временная диаграмма работы измерителя длительности входного сигнала приведена на рис. 9.20. Выходной код N измерителя связан с длительностью входного сигнала t простым соотношением t = NT, где T - период тактового сигнала. Абсолютная погрешность измерения не превышает величины ±Т. Поэтому для уменьшения относительной погрешности измерения необходимо увеличивать частоту тактового генератора и увеличивать разрядность счетчика. Счетчики также применяются и для измерения частоты входного цифрового сигнала. Частоту входного сигнала можно измерить двумя путями: косвенным, то есть измерением периода входного сигнала (по принципу, рассмотренному только что) и вычислением затем частоты (по формуле fвх = 1/Tвх), или же прямым измерением частоты. Первый метод требует вычислений с помощью компьютера или микроконтроллера, второй не требует никаких дополнительных вычислений. Поэтому мы рассмотрим здесь реализацию метода прямого измерения частоты. В соответствии с этим методом необходимо сформировать временное окно с заданной длительностью tо, в течение которого надо сосчитать количество N периодов входного сигнала Т (рис. 9.21). В этом случае будет выполняться соотношение tо = NT или f = N/tо, где f - это частота входного сигнала, равная 1/T. То есть частота входного сигнала пропорциональна коду N, а коэффициент пропорциональности равен 1/tо. Если, например, выбрать tо = 1 c, то код N будет равен частоте входного сигнала в герцах, а при tо = 1 мc код N будет равен частоте входного сигнала в килогерцах.  Рис. 9.21. Измерение частоты входного сигнала прямым методом Если длительность временного окна - строго постоянная величина, то погрешность измерения частоты будет определяться только погрешностью подсчета кода N. Абсолютная погрешность подсчета кода N не превысит единицы, а относительная погрешность не будет более 1/N. Понятно, что для увеличения точности измерения частоты нужно увеличивать N, то есть необходимо увеличивать длительность временного окна tо. Однако при этом автоматически увеличивается время измерения.  Рис. 9.22. Измеритель частоты входного сигнала прямым методом Схема измерителя частоты (рис. 9.22) практически не отличается от схемы измерителя длительности входного сигнала (рис. 9.19). Только в данном случае в качестве измеряемого сигнала будет использоваться сигнал временного окна, а в качестве тактового сигнала - входной сигнал. Для формирования сигнала временного окна можно применить схему рис. 9.15 (сигнал "Выход 2"), которая обеспечивает постоянную длительность выходного сигнала. Еще одно широко распространенное применение счетчиков - последовательное переключение (сканирование) нескольких устройств, узлов, индикаторов, каналов передачи и т.д. То есть имеется, например, группа устройств, которые должны по тем или иным причинам работать не одновременно, а по очереди, так, что в каждый момент активным является только одно устройство, причем очередь эта замкнута в кольцо и после последнего устройства начинает работать первое. Или же имеется несколько каналов связи (входных или выходных линий), которые надо также по очереди подключать к одному выходу (при выходных каналах) или к одному входу (при входных каналах). Во всех подобных случаях опрос, переключение, сканирование может производить счетчик с нужным числом разрядов. Счетчик с числом разрядов n может обслуживать 2n устройств (или каналов). В качестве первого примера рассмотрим схему переключения выходных каналов (рис. 9.23). Она последовательно, по очереди, циклически коммутирует один входной сигнал на восемь выходов, для чего используется счетчик, тактируемый сигналом задающего генератора, и дешифратор, работающий в качестве демультиплексора. Каждый из выходных каналов активен (то есть подключен) в течение одного периода тактового сигнала, а затем пассивен (то есть отключен) в течение семи периодов тактового сигнала. Предусмотрена возможность начального сброса схемы с помощью сигнала "Сброс".  Рис. 9.23. Схема последовательного переключения выходных каналов Используя данную схему, надо учитывать, что в момент переключения каналов может искажаться (обрезаться) выходной сигнал. Поэтому лучше всего обеспечить, чтобы входной сигнал приходил только тогда, когда переключение каналов не производится. Или на время передачи вообще останавливать процесс перебора каналов путем запрета прохождения импульсов с генератора на вход счетчика, а после окончания передачи снова разрешать последовательный перебор каналов.  |