|

|

Лекции по схемотехнике ЭВМ. Лекция Базовые понятия цифровой электроники версия для печати и pda в лекции рассказывается о базовых терминах цифровой электроники, о цифровых сигналах, об уровнях представления цифровых устройств, об их электрических и временных параметрах

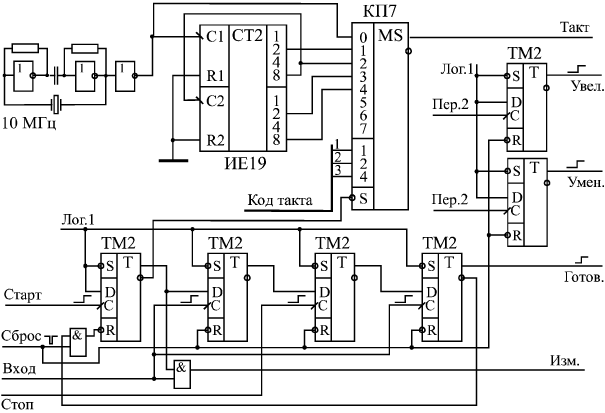

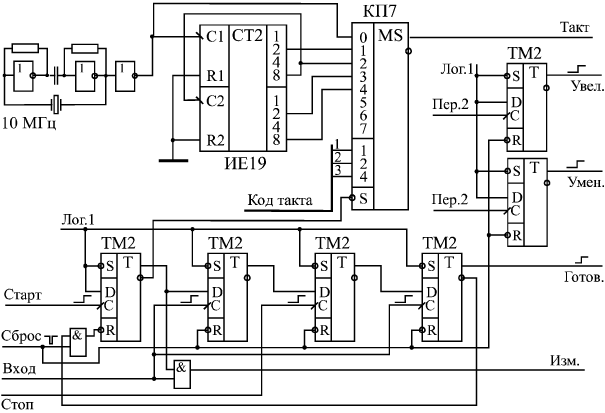

Рис. 9.32. Счетчики измерителя частоты входного сигнала

В основе схемы измерителя частоты по комбинированному методу (рис. 9.32) - два 16-разрядных счетчика на основе микросхем ИЕ7, одновременно работающих в режиме прямого счета. На тактовый вход одного счетчика (верхнего по рисунку) подается измеряемый сигнал "Изм.", на тактовый вход второго (нижнего по рисунку) счетчика - тактовый сигнал образцовой частоты "Такт". Выходные коды обоих счетчиков (соответственно, М и N) используются после окончания измерения для вычисления значения частоты входного сигнала.

Работа счетчиков разрешается отрицательным сигналом "–Разр." по фронту (например, положительному) входного сигнала. После окончания измерения по такому же фронту входного сигнала поступление сигналов "Изм." и "Такт" запрещается. То есть счет производится в течение целого числа периодов входного сигнала.

Выход "Стоп" (положительный фронт) говорит о том, что код N достиг достаточной величины (в нашем случае -8192), и, следовательно, можно останавливать измерение (но только по ближайшему фронту входного сигнала). Иначе говоря, код N в конце измерения будет не менее 8192, и поэтому погрешность измерения частоты входного сигнала не превысит 1/8192 или 0,012%.

Для правильной работы схемы частота входного сигнала должна быть не более тактовой частоты fT = 1/ ТТ и не менее fT /65536. Если она будет слишком малой, то наступит переполнение нижнего счетчика (выработается сигнал переноса "–Пер. 2"). Если же она будет слишком большой, то наступит переполнение верхнего счетчика (выработается сигнал переноса "–Пер. 1"). Например, при тактовой частоте 10 МГц измеряемая частота входного сигнала может находиться в пределах от 152,6 Гц до 10 МГц.

Полное время измерения будет изменяться в пределах от 8192ТТ до (8192ТТ + 2ТВХ). Один период ТВХ может прибавляться к времени измерения из-за того, что после разрешения измерения счет начинается не сразу, а только с приходом фронта входного сигнала. Второй период ТВХ может прибавляться за счет того, что счет заканчивается не сразу после достижения кодом N величины 8192, а только с приходом нужного (положительного) фронта входного сигнала. Максимальное время измерения в любом случае не превышает 65536ТТ для всех измеряемых частот.

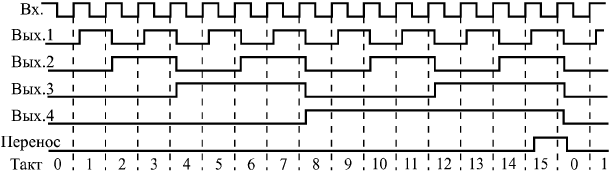

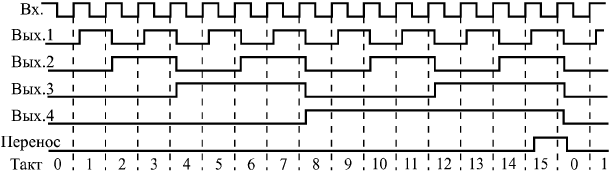

Для увеличения диапазона измеряемых частот можно применить предварительный управляемый делитель частоты (рис. 9.33). Он обеспечивает выбор период тактового сигнала из ряда 100 нс, 400 нс, 1,6 мкс, 6,4 мкс и 25,6 мкс с помощью кода такта. В результате применения этого делителя при минимальной тактовой частоте возможно измерение частоты входного сигнала до 0,6 Гц. Естественно, переход на каждый следующий диапазон измеряемых частот может увеличить время измерения в 4 раза, но точность измерения в любом случае останется прежней.

Рис. 9.33. Делитель частоты и схема управления для измерителя частоты входного сигнала

Схема управления измерителем частоты, также показанная на рис. 9.33, включает в себя цепочку из четырех последовательно срабатывающих триггеров (ТМ2). Перед началом измерения все эти триггеры сбрасываются в нуль сигналом "–Сброс".

Первый триггер перебрасывается в единицу по сигналу начала измерения "Старт" (положительный фронт). При этом разрешается прохождение подсчитываемых импульсов "Изм." и "Такт" на вход счетчиков (рис. 9.32). Одновременно разрешается работа второго триггера.

Второй триггер перебрасывается в единицу по положительному фронту входного сигнала. Тем самым он с помощью сигнала со своего инверсного выхода разрешает работу счетчиков (сигнал "–Разр."). Одновременно разрешается работа третьего триггера.

Третий триггер перебрасывается в единицу по сигналу "Стоп" (то есть при достижении кодом N числа 8192). Он разрешает работу четвертого триггера.

Наконец, четвертый триггер перебрасывается по положительному фронту входного сигнала и сигналом со своего инверсного выхода сбрасывает первый триггер. Поступление сигналов "Изм." и "Такт" прекращается. Выходной сигнал четвертого триггера служит флагом готовности выходных кодов N и M, которые необходимо прочитать для дальнейшего вычисления частоты. Перед новым измерением надо подать сигнал "Сброс".

Кроме четырех управляющих триггеров, в схему управления введены еще два триггера (справа на рисунке), выходные сигналы которых служат флагами переполнения и показывают после окончания измерения, правильно ли сработал измеритель частоты. Перед началом измерения оба эти триггера сбрасываются по сигналу "Сброс". Если частота входного сигнала в нужных пределах, то оба триггера останутся в нуле. Если частота входного сигнала очень большая, то сработает верхний по рисунку триггер по входному сигналу переноса "Пер. 1" (см. рис. 9.32) и выдаст сигнал "Увел.", говорящий о том, что надо поднять частоту тактового сигнала (если это возможно). Если же частота входного сигнала слишком мала, то сработает нижний по рисунку триггер по входному сигналу переноса "Пер. 2" (см. рис. 9.32) и выдаст сигнал "Умен.", говорящий о том, что надо уменьшить частоту тактового сигнала (если возможно).

10. Лекция: Синхронные счетчики: версия для печати и PDA

В этой рассматриваются синхронные счетчики, их алгоритмы работы, параметры, типовые схемы включения, а также способы реализации на их основе некоторых часто встречающихся функций.

|

|

|

|

Синхронные (или параллельные) счетчики представляют собой наиболее быстродействующую разновидность счетчиков. Наращивание их разрядности при соблюдении определенных условий не приводит к увеличению полной задержки срабатывания. То есть можно считать, что именно синхронные счетчики работают как идеальные счетчики, все разряды которых срабатывают одновременно, параллельно. Задержка срабатывания счетчика в этом случае примерно равна задержке срабатывания одного триггера. Достигается такое быстродействие существенным усложнением внутренней структуры микросхемы.

Вместе с тем недостатком синхронных счетчиков является более сложное управление их работой по сравнению с асинхронными счетчиками и с синхронными счетчиками с асинхронным переносом. Поэтому синхронные счетчики целесообразно применять только в тех случаях, когда действительно требуется очень высокое быстродействие, очень высокая скорость переключения разрядов. Иначе усложнение схемы управления может быть не оправдано.

Рис. 10.1. Временная диаграмма работы синхронных двоичных счетчиков

Временная диаграмма работы синхронного счетчика (рис. 10.1) отличается от временной диаграммы синхронного счетчика с асинхронным переносом способом формирования сигнала переноса, используемого при каскадировании счетчиков для увеличения разрядности. Сигнал переноса CR (от английского "Carry") вырабатывается в данном случае тогда, когда все выходы счетчика устанавливаются в единицу (при прямом счете) или в нуль (при обратном, инверсном счете). Входной тактовый сигнал в образовании сигнала переноса при этом не участвует.

При каскадировании (совместном включении для увеличения разрядности), например, двух счетчиков тактовые входы С обоих счетчиков объединяются, а сигнал переноса первого счетчика подается на вход разрешения счета (ECT) второго счетчика. В результате второй счетчик будет считать каждый шестнадцатый входной тактовый импульс (так как он будет срабатывать только при переносе от первого счетчика). Выходные сигналы второго счетчика будут переключаться по фронту общего тактового сигнала одновременно с выходными сигналами первого счетчика. Условием правильной работы будет в данном случае следующее: за период тактового сигнала должен успеть выработаться сигнал переноса первого счетчика.

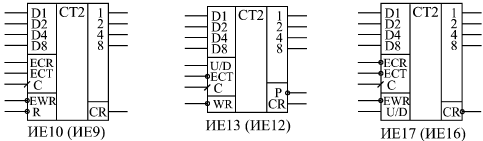

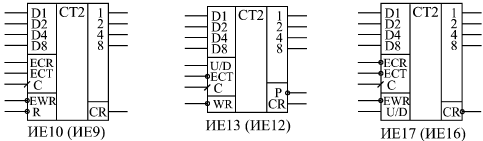

Рис. 10.2. Синхронные счетчики стандартных серий

В стандартные серии микросхем входят несколько разновидностей синхронных (параллельных) счетчиков (рис. 10.2). Различаются они способом счета (двоичные или двоично-десятичные, реверсивные или не реверсивные) и управляющими сигналами (наличием или отсутствием сигнала сброса). Все счетчики считают по положительному фронту тактового сигнала, все имеют выход переноса CR и входы расширения для каскадирования. Все счетчики имеют возможность параллельной записи информации.

Таблица 10.1. Режимы работы счетчиков ИЕ9 и ИЕ10

|

Входы

|

Режим

|

-R

|

-EWR

|

ECR

|

ECT

|

C

|

|

0

|

Х

|

Х

|

Х

|

Х

|

Сброс

|

1

|

0

|

Х

|

Х

|

0 1 1

|

Параллельная запись

|

1

|

1

|

0

|

Х

|

Х

|

Хранение

|

1

|

1

|

Х

|

0

|

Х

|

Хранение

|

1

|

1

|

1

|

1

|

0 1 1

|

Прямой счет

|

Счетчики ИЕ9 и ИЕ10 отличаются друг от друга только тем, что ИЕ9 — двоично-десятичный, а ИЕ10 — двоичный. Микросхемы имеют вход асинхронного сброса –R, по нулевому уровню на котором все выходы счетчика сбрасываются в нуль. Счет (только прямой) производится по положительному фронту на тактовом входе С. Параллельная запись осуществляется синхронно, по положительному фронту на тактовом входе С при установленном в нуль сигнале разрешения записи –EWR. Сигналы ECR ("Enable Carry" — разрешение переноса) и ECT ("Enable Count" — разрешение счета) используются при каскадировании микросхем. Разница между этими сигналами в том, что сигнал ECR не только запрещает счет, как сигнал ECT, но еще и запрещает выработку сигнала переноса CR. Счет идет при единичных сигналах на обоих входах ECT и ECT и при единичном сигнале на входе –EWR. Положительный сигнал переноса CR вырабатывается при максимально возможном коде на выходах счетчика (15 для ИЕ10 и 9 для ИЕ9) и при положительном сигнале на входе ECR. Таблица режимов работы счетчиков ИЕ9 и ИЕ10 представлена в табл. 10.1.

Счетчики ИЕ12 (двоично-десятичный) и ИЕ13 (двоичный) отличаются от ИЕ9 и ИЕ10 тем, что они реверсивные, то есть допускают как прямой, так и обратный счет. Кроме того, у них несколько другое управление. Считают они также по положительному фронту тактового сигнала С при нулевом уровне на входе разрешения счета ECT. Прямой счет осуществляется при нулевом уровне на входе управления U/D, обратный — при единичном уровне на входе U/D. Переключение уровней на входах U/D и ECT допускается только при положительном сигнале на тактовом входе С. Сброс счетчиков ИЕ12 и ИЕ13 в нуль не предусмотрен, зато имеется возможность асинхронной параллельной записи информации по нулевому уровню сигнала параллельной записи –WR.

Положительный сигнал на выходе параллельного переноса CR появляется при достижении максимального кода (15 для ИЕ13 и 9 для ИЕ12) при прямом счете или при достижении нулевого кода при обратном (инверсном) счете. Имеется также выход последовательного переноса Р, отрицательный импульс на котором вырабатывается при положительном сигнале CR и повторяет отрицательный импульс на тактовом входе С (аналогично рассмотренным ранее счетчикам ИЕ6 и ИЕ7).

Режимы работы счетчиков ИЕ12 и ИЕ13 представлена в табл. 10.2.

Таблица 10.2. Режимы работы счетчиков ИЕ12 и ИЕ13

|

Входы

|

Режим

|

-WR

|

U/D

|

-ECR

|

C

|

|

0

|

Х

|

Х

|

Х

|

Параллельная запись

|

1

|

Х

|

1

|

Х

|

Хранение

|

1

|

0

|

0

|

0 1 1

|

Прямой счет

|

1

|

1

|

0

|

0 1 1

|

Обратный счет

|

Микросхемы ИЕ16 (двоично-десятичный счетчик) и ИЕ17 (двоичный счетчик) отличаются от рассмотренных синхронной параллельной записью по фронту тактового сигнала С, возможностью прямого и обратного счета и отсутствием сигнала сброса в нуль.

Срабатывают счетчики ИЕ16 и ИЕ17 по положительному фронту тактового сигнала С. При нулевом уровне на входе разрешения записи -EWR по фронту сигнала С в счетчик записывается информация со входов данных D1, D2, D4, D8. При единичном уровне на входе –EWR по положительному фронту сигнала С происходит счет. Направление счета определяется входом U/D: при единице на этом входе счет прямой, при нуле — обратный. Имеются два входа расширения: вход разрешения счета –ECT и вход разрешения переноса –ECR. Различаются эти два входа тем, что сигнал –ECR не только запрещает счет, как сигнал –ECT, но еще и запрещает выработку сигнала переноса. Переключение уровней на входах U/D, –ECT и –ECR надо производить только при единичном уровне на тактовом входе С.

Отрицательный сигнал переноса –CR (синхронный) вырабатывается при достижении на выходах счетчика максимального кода (15 для ИЕ7 или 9 для ИЕ16) при прямом счете или нулевого кода при обратном счете.

Режимы работы счетчиков ИЕ16 и ИЕ17 приведены в табл. 10.3.

Таблица 10.3. Режимы работы счетчиков ИЕ16 и ИЕ17

|

Входы

|

Режим

|

-EWR

|

U/D

|

-ECT

|

-ECR

|

C

|

|

0

|

Х

|

Х

|

Х

|

0 1 1

|

Параллельная запись

|

1

|

1

|

0

|

0

|

0 1 1

|

Прямой счет

|

1

|

0

|

0

|

0

|

0 1 1

|

Обратный счет

|

1

|

Х

|

1

|

Х

|

Х

|

Хранение

|

1

|

Х

|

Х

|

1

|

Х

|

Хранение

|

Возможности применения синхронных (параллельных) счетчиков очень широки. Достаточно сказать, что они без всяких проблем могут заменить во всех схемах как асинхронные (последовательные) счетчики, так и синхронные счетчики с асинхронным (последовательным) переносом. При необходимости достижения максимального быстродействия они имеют большие преимущества по сравнению со всеми другими счетчиками. Их выходной код устанавливается одновременно при любом количестве разрядов без применения дополнительных выходных регистров (которые требовались в случае асинхронных счетчиков и синхронных счетчиков с асинхронным переносом).

Мы рассмотрим здесь всего несколько схем, иллюстрирующих характерные особенности именно синхронных счетчиков.

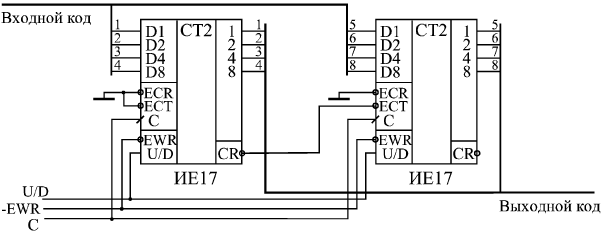

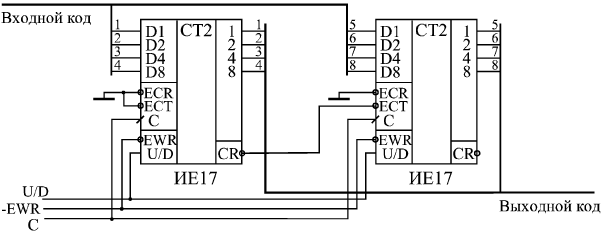

Сначала остановимся на методах каскадирования счетчиков. В отличие от других типов счетчиков, синхронные счетчики можно соединять различными способами, причем способ соединения различен для разного количества микросхем. В качестве примера возьмем микросхемы ИЕ17.

| |

|

|

Скачать 5.63 Mb.

Скачать 5.63 Mb.