|

|

Лекции по схемотехнике ЭВМ. Лекция Базовые понятия цифровой электроники версия для печати и pda в лекции рассказывается о базовых терминах цифровой электроники, о цифровых сигналах, об уровнях представления цифровых устройств, об их электрических и временных параметрах

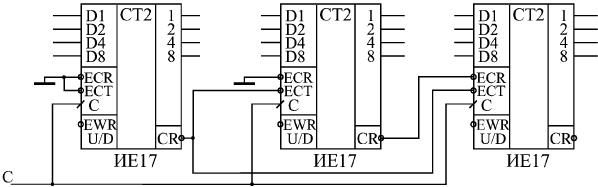

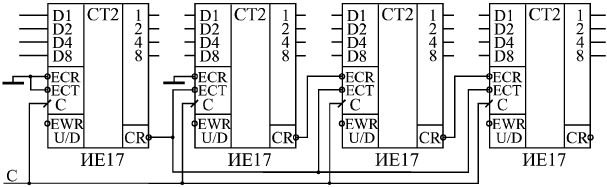

Рис. 10.3. Объединение двух счетчиков ИЕ17

При объединении двух счетчиков (рис. 10.3) никаких проблем не возникает: выход переноса –CR младшего счетчика соединяется со входом разрешения счета старшего счетчика –ECT. На входы –ECR обоих счетчиков подается нулевой уровень. Условие правильной работы будет простым и легко выполнимым: период тактового сигнала С не должен быть меньше, чем задержка выработки сигнала переноса CR.

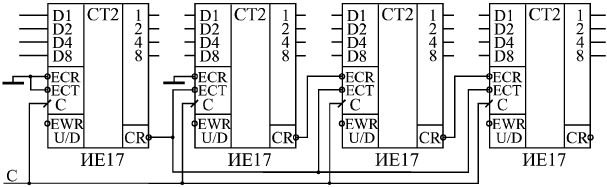

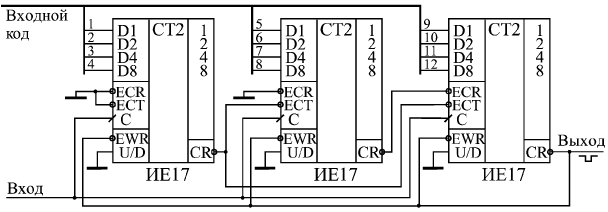

Рис. 10.4. Объединение трех счетчиков ИЕ17

При объединении трех счетчиков ситуация несколько усложняется (рис. 10.4). Сигнал с выхода переноса первого счетчика подается на входы -ECT второго и третьего счетчиков. Сигнал с выхода переноса второго счетчика подается на вход -ECR третьего счетчика. В результате третий счетчик будет считать только тогда, когда имеется перенос как у первого, так и у второго счетчика. На рисунке для простоты не показано подключение входных и выходных сигналов, не участвующих в каскадировании.

Условие правильной работы схемы остается тем же, что и в случае двух счетчиков: период тактового сигнала С не должен быть меньше задержки выработки сигнала переноса CR.

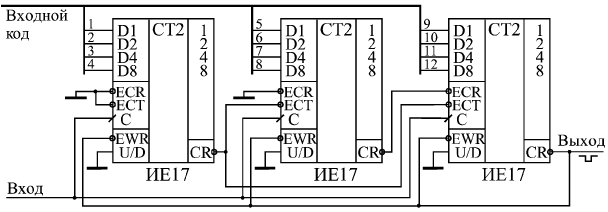

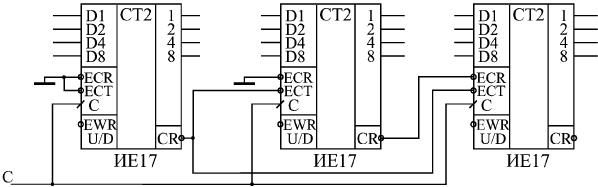

При объединении четырех (и более) счетчиков уже возникает проблема, так как у старших счетчиков не остается свободных управляющих входов для собирания всех сигналов переноса более младших счетчиков. Поэтому в данном случае используется способность входного сигнал –ECR запрещать выходной сигнал переноса -CR (рис. 10.5). На четвертый и последующие счетчики подаются уже сигналы переноса не со всех предыдущих счетчиков, а только с первого и с предыдущего. На рисунке для простоты не показано подключение входов и выходов, не участвующих непосредственно в каскадировании.

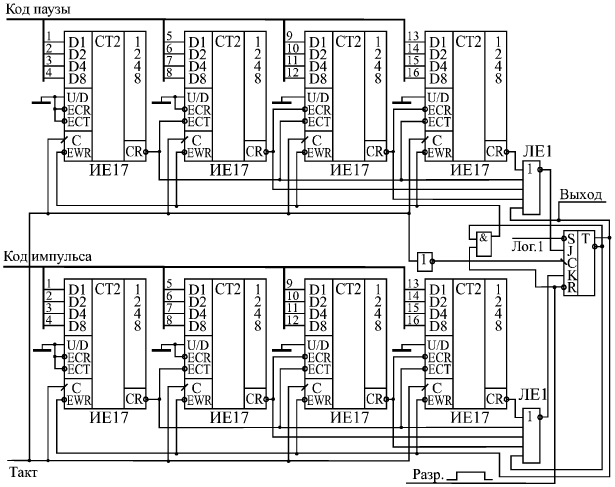

Рис. 10.5. Объединение четырех счетчиков ИЕ17

При таком включении происходит уже накапливание задержки сигналов переноса. Максимальной задержка будет для сигнала переноса второго счетчика. Условие правильной работы всех счетчиков будет следующее: период тактового сигнала С не должен быть меньше, чем максимальная суммарная задержка сигналов переноса до входа последнего счетчика. При объединении четырех счетчиков в эту максимальную задержку входят задержка сигнала переноса –CR микросхемы относительно фронта сигнала С и задержка сигнала переноса –CR относительно сигнала –ECR. При объединении пяти счетчиков добавится еще одна задержка сигнала переноса –CR относительно сигнала –ECR и т.д. Поэтому с увеличением количества объединяемых счетчиков будет снижаться допустимая тактовая частота.

При необходимости объединения большого количества счетчиков (большего четырех) можно избежать накопления суммарной задержки переноса, включив на входах старших счетчиков -ECT логические элементы ИЛИ с нужным числом входов. Эти элементы должны собирать все сигналы переноса с более младших счетчиков, то есть на их выходах должен быть нуль тогда, когда сигналы -CR всех предыдущих счетчиков нулевые. При этом, правда, в суммарную задержку переноса, которая не должна превышать периода тактового сигнала С, войдут задержки этих самых элементов ИЛИ.

В любом случае при выполнении условия правильной работы счетчиков схема будет работать как идеальный счетчик, то есть все разряды многокаскадного счетчика будут переключаться одновременно.

А теперь рассмотрим некоторые схемы на основе синхронных счетчиков.

Управляемый делитель частоты с коэффициентом пересчета, задаваемым входным кодом, реализуется на синхронных счетчиках довольно просто (рис. 10.6). Сигнал переноса -CR старшего счетчика подается на вход разрешения записи –EWR. Счетчики работают в режиме обратного счета (на вход U/D подан сигнал логического нуля).

Рис. 10.6. Управляемый делитель частоты

При достижении всеми счетчиками нулевого кода вырабатывается сигнал переноса -CR, переводящий счетчики в режим параллельной записи входного управляющего кода. Следующим положительным фронтом тактового сигнала С входной код записывается в счетчики. Это приводит к новому циклу счета от входного кода до нуля.

Коэффициент пересчета делителя частоты равен (N+1), где N — входной код, который может принимать значения от 1 до (2n–1), где n — количество разрядов кода. Условие правильной работы делителя частоты следующее: период тактового сигнала не должен быть меньше полной задержки переноса. Длительность выходного сигнала делителя частоты равна периоду тактовой частоты.

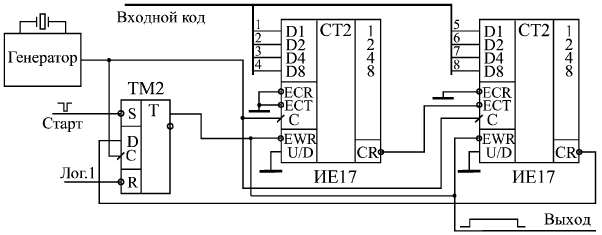

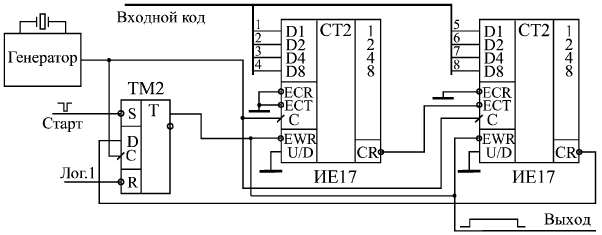

Следующая схема — формирователь временного интервала заданной длительности (рис. 10.7) демонстрирует, как надо использовать выходной сигнал переноса синхронных счетчиков при необходимости организации разового (не периодического) цикла работы.

Рис. 10.7. Формирователь интервала заданной длительности

Работа формирователя начинается по короткому отрицательному импульсу "–Старт", перебрасывающему управляющий триггер в единицу и начинающему выходной сигнал. Положительный сигнал с выхода триггера переводит 8-разрядный синхронный счетчик из режима параллельной записи входного кода в режим счета (по входу –EWR). Счет на уменьшение идет по положительным фронтам тактового сигнала с генератора. Когда счетчик досчитает до нуля, следующим положительным фронтом тактового сигнала нулевой сигнал переноса –CR будет записан в триггер. Тем самым будет завершен выходной сигнал, а счетчик будет переведен в режим параллельной записи. Следующий цикл работы формирователя начнется по сигналу "–Старт".

В данном случае триггер, обрабатывающий сигнал переноса, работает синхронно со счетчиками, так как тактируется тем же (положительным) фронтом единого тактового сигнала. Длительность выходного сигнала будет находиться в интервале от NT до (N+1)T, где Т — период тактового сигнала с генератора, а N — входной код от 0 до 2510.

Посмотрим, как на синхронных счетчиках можно построить генератор прямоугольных импульсов с регулируемыми длительностью импульса и длительностью паузы, который был рассмотрен в предыдущем разделе (см. рис. 9.28 и 9.29). Будем ориентироваться на достижение максимального быстродействия, то есть на максимально возможную тактовую частоту.

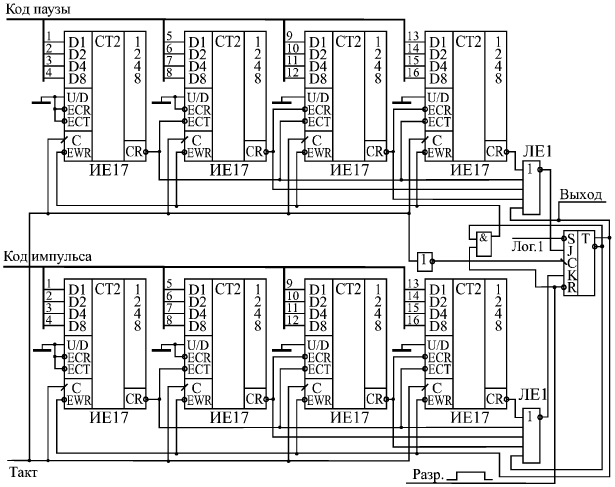

Схема управления будет мало отличаться от схемы рис. 9.29, поэтому мы остановимся только на схеме счетчиков импульса и паузы. Выберем разрядность обоих этих счетчиков равной 16. Тогда схема счетчиков импульса и паузы (рис. 10.8) будет включать в себя восемь микросхем счетчиков ИЕ17 и выходной триггер, а также логические элементы 4ИЛИ-НЕ для уменьшения задержек переноса. В данном случае очень удобно брать JK-триггер, так как он имеет два информационных входа и тактовый вход.

Триггер тактируется отрицательным фронтом сигнала С, а счетчики — положительным фронтом, поэтому для обеспечения синхронной работы всей схемы по одному фронту тактового сигнала сигнал на вход С триггера подается через инвертор.

Рис. 10.8. Синхронные счетчики импульса и паузы для генератора прямоугольных импульсов

Суть работы схемы остается прежней: 16-разрядные счетчики импульса и паузы работают по очереди, что определяется управляющими сигналами с выходов триггера (прямого и инверсного). Счетчики считают на уменьшение (в режиме инверсного счета) от кода, параллельно записанного в них, до нуля.

До начала работы (сигнал "Разр." нулевой) оба счетчика находятся в состоянии параллельной записи и записывают в себя код импульса и паузы. После прихода положительного сигнала разрешения генерации "Разр." начинает счет верхний по рисунку счетчик (счетчик паузы).

Когда счетчик паузы досчитывает до нуля, его сигнал переноса записывается в триггер по входу J и перебрасывает выход триггера в единицу, что переводит счетчик паузы из состояния счета в состояние параллельной записи и запрещает поступления сигнала на вход J. Одновременно переходит в состояние счета нижний по рисунку счетчик (счетчик импульса), который, в свою очередь досчитав до нуля, перебрасывает триггер в нуль по входу К. Этот процесс периодически повторяется, пока разрешена генерация (то есть сигнал "Разр." — положительный).

Сформулируем условия правильной работы схемы.

Во-первых, за период тактового сигнала должен успеть полностью сработать 16-разрядный счетчик, выполненный на четырех микросхемах синхронных счетчиков. То есть сигнал на входы -ECR и -ECT последнего счетчика должны успеть придти до следующего фронта тактового сигнала.

Во-вторых, за период тактового сигнала должна успеть сработать цепочка из инвертора (ЛН1), триггера (ТВ11) и элемента 2И (ЛИ1). Это более мягкое требование, чем предыдущее, если, конечно, взять перечисленные элементы из быстродействующих серий КР531 или КР1531.

Рассмотренный переход на синхронные счетчики позволяет повысить максимальную частоту тактового сигнала генератора прямоугольных импульсов по меньшей мере вдвое (до 20 МГц) по сравнению со схемой на синхронных счетчиках с асинхронным переносом.

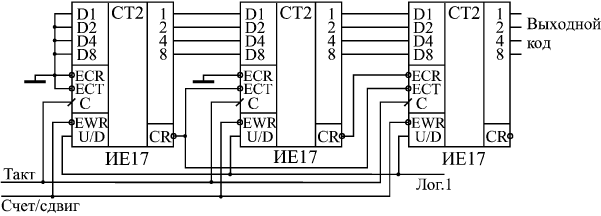

Наконец, последнее применение синхронных счетчиков, которое мы рассмотрим, связано с их возможностью параллельной записи по фронту тактового сигнала. То есть в режиме параллельной записи счетчик представляет собой регистр, срабатывающий по фронту тактового сигнала. Благодаря этой особенности при объединении нескольких счетчиков их выходные коды можно последовательно считывать с выходов последнего в цепочке, старшего счетчика (рис. 10.9). Счетчики в данном случае образуют своеобразный многоразрядный сдвиговый регистр.

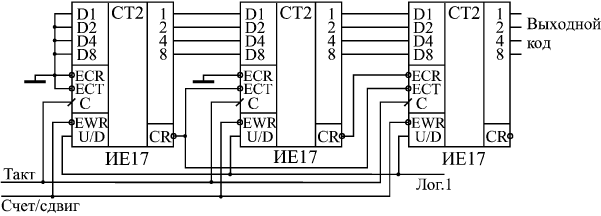

Режим работы схемы определяется управляющим сигналом "Счет/Сдвиг". При высоком уровне этого сигнала счетчики находятся в режиме прямого счета по фронту сигнала "Такт". При низком уровне сигнала счетчики переходят в режим последовательного счета 12-разрядного счетчика через четыре разряда правого по рисунку счетчика. Первым читается состояние старшего счетчика, последним — младшего. Сдвиг выходного кода происходит по положительному фронту тактового сигнала. После трех импульсов тактового сигнала во все три счетчика оказывается записанным нулевой код, то есть схема готова к режиму прямого счета.

Рис. 10.9. Последовательное чтение выходного кода многокаскадного счетчика

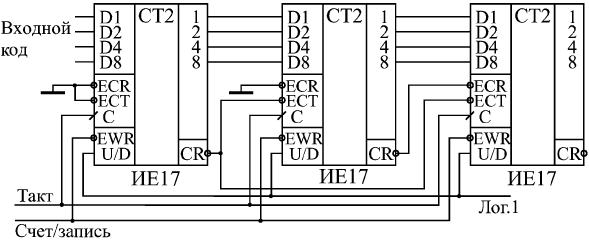

Рис. 10.10. Последовательная запись в счетчики исходного состояния

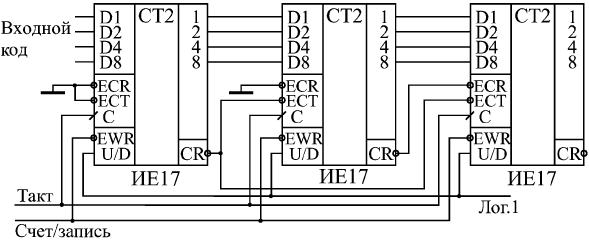

И точно такая же последовательная перезапись информации из счетчика в счетчик позволяет с помощью 4-разрядных входных кодов записать исходное состояние нескольких последовательно соединенных счетчиков (рис. 10.10).

Перед началом работы схема переводится в состояние параллельной записи нулевым уровнем сигнала "Счет/Запись". При этом 4-разрядные коды, которые надо записать во все счетчики, по очереди подаются на вход первого (младшего) счетчика и сдвигаются по направлению к старшему счетчику по положительному фронту тактового сигнала С. Для записи всех трех счетчиков необходимо подать три тактовых импульса подряд. Причем первым надо записывать код, предназначенный для старшего (на рисунке справа) счетчика, а последним — код, предназначенный для младшего (на рисунке слева) счетчика.

|

|

|

|

Скачать 5.63 Mb.

Скачать 5.63 Mb.