Лекции по схемотехнике ЭВМ. Лекция Базовые понятия цифровой электроники версия для печати и pda в лекции рассказывается о базовых терминах цифровой электроники, о цифровых сигналах, об уровнях представления цифровых устройств, об их электрических и временных параметрах

Скачать 5.63 Mb. Скачать 5.63 Mb.

|

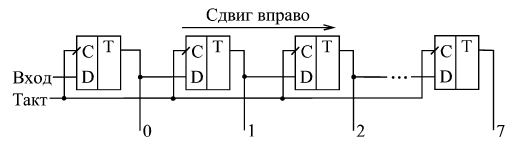

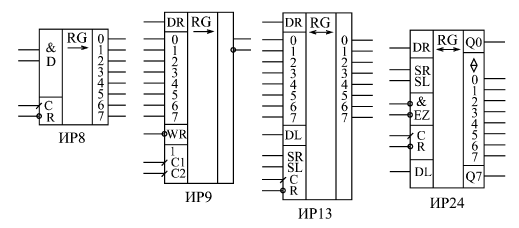

Сдвиговые регистрыРегистры сдвига или сдвиговые регистры (англ. shift register) представляют собой, как уже отмечалось, последовательно соединенную цепочку триггеров. Основной режим их работы - это сдвиг разрядов кода, записанного в эти триггеры, То есть по тактовому сигналу содержимое каждого предыдущего триггера переписывается в следующий по порядку в цепочке триггер. Код, хранящийся в регистре, с каждым тактом сдвигается на один разряд в сторону старших разрядов или в сторону младших разрядов, что и дало название регистрам данного типа. В связи с названием направления сдвига в сдвиговых регистрах часто возникает путаница. Сдвиг бывает двух видов: вправо (основной режим, который есть у всех сдвиговых регистров) и влево (этот режим есть только у некоторых, реверсивных сдвиговых регистров). Названия эти отражают внутреннюю структуру регистров сдвига (рис. 8.14) и перезапись сигналов последовательно по цепочке триггеров. При этом триггеры, вполне естественно, нумеруются слева направо, например, от 0 до 7 (или от 1 до 8) для 8-разрядных регистров. В результате сдвиг информации регистром вправо представляет собой сдвиг в сторону разрядов, имеющих большие номера, а сдвиг информации регистром влево - это сдвиг в сторону разрядов, имеющих меньшие номера. Однако, как известно, в любом двоичном числе слева расположены старшие разряды, а справа - старшие разряды. Поэтому сдвиг двоичного числа вправо будет сдвигом в сторону младших разрядов, а сдвиг влево - сдвигом в сторону старших разрядов. Это противоречие, не чей-то злой умысел, просто так исторически сложилось, и об этом надо помнить разработчику цифровой аппаратуры.  Рис. 8.14. Направление сдвига в сдвиговых регистрах В стандартные серии цифровых микросхем входит несколько типов сдвиговых регистров, отличающихся возможными режимами работы, режимами записи, чтения и сдвига, а также типом выходных каскадов (2С или 3С). Большинство регистров сдвига имеет восемь разрядов. На рис. 8.15 представлены для примера четыре типа микросхем регистров сдвига. Регистр ИР8 - наиболее простой из регистров сдвига. Он представляет собой 8-разрядную линию задержки, то есть имеет только один информационный вход, на который подается последовательная сдвигаемая информация (точнее, два входа, объединенных по функции 2И), и восемь параллельных выходов. Сдвиг в сторону выходов со старшими номерами осуществляется по переднему фронту тактового сигнала С. Имеется также вход сброса –R, по нулевому сигналу на котором все выходы регистра сбрасываются в нуль. Таблица истинности регистра ИР8 приведена в табл. 8.5.  Рис. 8.15. Сдвиговые регистры

Регистр ИР9 выполняет функцию, обратную регистру ИР8. Если ИР8 преобразует входную последовательную информацию в выходную параллельную, то регистр ИР9 преобразует входную параллельную информацию в выходную последовательную. Однако суть сдвига не меняется, просто в ИР9 все внутренние триггеры имеют выведенные параллельные входы, и только один, последний триггер имеет выход (причем как прямой, так и инверсный). Запись входного кода в регистр производится по нулевому сигналу на входе -WR. Сдвиг осуществляется по положительному фронту на одном из двух тактовых входов С1 и С2, объединенных по функции 2ИЛИ. Имеется также вход расширения DR, сигнал с которого в режиме сдвига перезаписывается в младший разряд сдвигового регистра. Таблица истинности регистра ИР9 приведена в табл. 8.6.

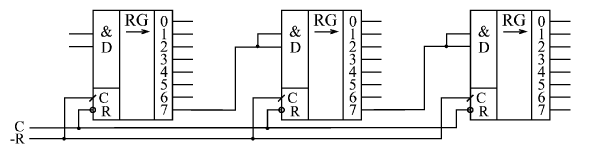

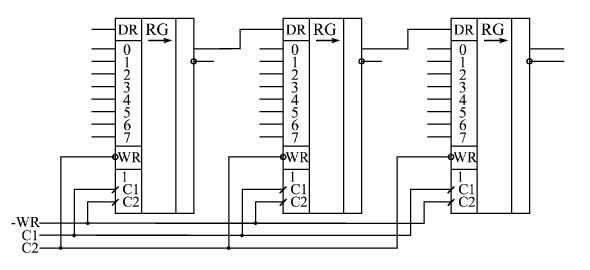

Рис. 8.16. Соединение регистров ИР8 для увеличения разрядности Как и все остальные сдвиговые регистры, ИР8 и ИР9 допускают каскадирование, то есть совместное включение для увеличения разрядности. На рис. 8.16 показано объединение трех ИР8, а на рис 8.17 - совместное включение трех ИР9. В обоих случаях в результате объединения получается 24-разрядный сдвиговый регистр. При этом увеличение разрядности не приводит к увеличению задержки сдвига, так как тактовые входы всех используемых регистров объединяются параллельно. В случае регистров ИР8 входной последовательный код преобразуется в 24-разрядный выходной параллельный код. В случае регистров ИР9 входной 24-разрядный параллельный код преобразуется в выходной последовательный код.  Рис. 8.17. Соединение регистров ИР9 для увеличения разрядности Регистр ИР13 соединяет в себе возможности регистров ИР8 и ИР9. Он имеет как восемь входов для параллельной записи, так и соответствующие им восемь выходов параллельной информации. Сдвиг осуществляется по положительному фронту тактового сигнала С, причем сдвиг возможен как в сторону старших разрядов (вправо), так и в сторону младших разрядов (влево). Для наращивания разрядности у регистра ИР13 имеются последовательные информационные входы DR и DL, сигналы с которых вдвигаются, соответственно, в младший и в старший разряды. Предусмотрен сброс всех выходов регистра в нуль по нулевому сигналу на входе –R.

Режим работы регистра ИР13 определяется двумя управляющими входами SR и SL. При единице на входе SR и нуле на входе SL по фронту сигнала С происходит сдвиг в сторону старших разрядов. При нуле на входе SR и единице на входе SL по фронту сигнала С происходит сдвиг в сторону младших разрядов. При обоих единичных сигналах на входах SR и SL по фронту сигнала С происходит параллельная загрузка информации в регистр. Таблица истинности регистра ИР13 приведена в табл. 8.7. Отметим, что регистр ИР13 применяется заметно реже, чем более простые регистры ИР8 и ИР9, так как задач, в которых были бы нужны все возможности ИР13, не так уж много, а управление работой ИР13 - довольно сложное. Наконец, последний сдвиговый регистр, который мы рассмотрим подробнее, это регистр ИР24. По своим возможностям он близок к ИР13, однако его главной особенностью является двунаправленная параллельная шина данных. То есть одни и те же выводы микросхемы используются как для параллельной записи информации в регистр, так и для параллельного чтения информации из регистра. При этом двунаправленные выводы данных имеют повышенную нагрузочную способность. Это позволяет легко сопрягать ИР24 с многоразрядными микросхемами памяти и с двунаправленными буферами. Поэтому применяется данный регистр чаще, чем ИР13. Регистр ИР24 обеспечивает сдвиг информации в обоих направлениях. Имеются входы расширения DR и DL, а также выходы расширения Q0 и Q7, что позволяет легко наращивать разрядность. Отличие выходов Q0 и Q7 от нулевого и седьмого разрядов данных состоит в том, что Q0 и Q7 - однонаправленные, то есть в любом режиме работы выдают информацию с выходов внутренних триггеров младшего и старшего разрядов. Тактируется регистр положительным фронтом сигнала С. Предусмотрен сброс регистра нулевым сигналом на входе –R. Режим работы микросхемы определяется сигналами на управляющих входах SR и SL. При единичном сигнале на SR и нулевом сигнале на SL по положительному фронту сигнала С происходит сдвиг информации вправо (в сторону разрядов с большими номерами). Запись в разряд 0 производится при этом со входа расширения DR. При единичном сигнале на SL и нулевом сигнале на SR по положительному фронту сигнала С происходит сдвиг информации влево (в сторону разрядов с меньшими номерами). Запись в разряд 7 производится при этом со входа расширения DL. При обоих нулях на входах SR и SL регистр переходит в режим хранения. Во всех этих случаях разряды данных работают как вход или как выход в зависимости от сигналов –EZ.

При обеих единицах на входах SR и SL по положительному фронту С в регистр записывается параллельный код, причем разряды данных переходят в состояние приема независимо от сигналов –EZ. Таблица истинности регистра ИР24 приведена в табл. 8.8.  | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||