Лекции_Вычислительные машины_new. Лекция История развития вычислительной техники

Скачать 5.16 Mb. Скачать 5.16 Mb.

|

Выполнение операции сложения над числами с плавающей запятойРассмотрим специфику операции сложение-вычитание с плавающей запятой. Число Х, представленное в форме с плавающей запятой, имеет вид: где p – порядок числа, М – мантисса, k – основание системы счисления. Если каждому числу Х однозначно соответствует пара p, k, то 1>|M|k-1, а число Х называется нормализованным. Порядок и мантисса числа записываются в своих разрядах в виде чисел с фиксированной запятой; мантисса – в виде дробного числа с запятой перед старшим из основных разрядов, порядок – в виде целого числа с запятой после младшего разряда. Структура представления в ЭВМ числа с плавающей запятой более подробно рассмотрена в гл.I п.1. Разрядная сетка машины с плавающей запятой имеет следующий вид:

В нормализованных числах мантисса содержит максимальное количество значащих цифр, поэтому нормализованные числа представляются с максимальной точностью. Выполнение операции сложения-вычитания чисел с плавающей запятой состоит из следующих этапов: - выравнивание порядков; - суммирование мантисс; - определение порядка результата; - нормализация результата; - округление результата. Выравнивание порядков осуществляется путем сдвига вправо мантиссы числа с меньшим порядком. Так как сдвиг вправо эквивалентен делению мантиссы на k, то при каждом сдвиге порядок должен увеличиваться на 1. Порядок результата принимается равным порядку большего числа. В результате алгебраического сложения мантисс после выравнивания порядка получают мантиссу суммы (разности). Полученная сумма (разность) нормализуется. Для выполнения операции выравнивания порядка используется сумматор порядков, в котором из порядка первого числа вычитают порядок второго числа. По знаку разности определяют больший порядок, а абсолютная величина разности позволяет определить необходимое число сдвигов. При сравнении порядков возможны пять случаев: а) px - py б) px - py < n – второе слагаемое является результатом суммирования; в) px - py = 0 – приступают к суммированию мантисс; г) px - py = k1 (k1 < n) – мантисса второго слагаемого сдвигается на k1 разрядов вправо, затем мантиссы суммируются; д) py - px = k2 (k2 < n) – мантисса первого слагаемого сдвигается на k2 разрядов вправо, затем мантиссы суммируются. Мантиссы, полученные после выравнивания порядков, складываются как двоичные числа с фиксированной запятой. При этом результат может оказаться ненормализованным. Если используются модифицированные коды, то переполнение (левое нарушение нормализации) определяется по комбинациям цифр 01 и 10 в знаковых разрядах суммы мантисс. Нормализация заключается при этом в сдвиге мантиссы результата вправо на 1 разряд. Правое нарушение нормализации определяется по комбинациям цифр 00,0 (11,1) в старшем и знаковом разрядах мантиссы результата. При этом нормализация результата заключается в сдвиге мантиссы результата влево до тех пор, пока не появится “1” (“0”) в старшем разряде сетки мантиссы. При нормализации сдвиг вправо результата и отбрасывание его младшего разряда могут привести к большой положительной ошибке. Для уменьшения погрешности применяют округление, состоящее в использовании дополнительного разряда со стороны младших разрядов. Если в дополнительном разряде будет 1, то ее добавляют в младший основной разряд. Вследствие этого погрешность будет закономерной и не больше 2-n веса младшего разряда. Операции умножения и деления чисел с плавающей запятой Числа X, Y, представленные с плавающей запятой, имеют соответствующие порядки px и py, которые целые и могут лежать в диапазоне - (2+m-1) p +(2+m-1). Величины pmin= -(2+m-1) и pmax= +(2+m-1) представляют собой минимальный и максимальный порядки, которые могут быть размещены в разрядной сетке порядков. Если при микрооперациях с порядками порядок получается меньше чем pmin, то число считается “малым” (отрицательное переполнение разрядной сетки порядков) и его приравнивают к нулю. Если порядок после микрооперации получается больше pmax, то число получается “большим” и не может разместиться в разрядной сетке (положительное переполнение) ЭВМ. Поэтому результат считается неверным, вычисления прекращают, выдавая сигнал переполнения. Операции умножения и деления с плавающей запятой легко сводятся к операциям с фиксированной запятой: Z=XY=2Px + Py (MX · MY), Z=X/Y=2Px - Py (MX / MY). При умножении (делении) порядки складываются (вычитаются) по правилам сложения с фиксированной запятой после младшего разряда, а мантиссы умножаются (делятся) по правилам умножения (деления) чисел с фиксированной запятой перед старшим разрядом. При микрооперациях над порядками проверяются отрицательное и положительное переполнение. После микроопераций над мантиссами проверяется нормализация мантиссы результата. При умножении нормализованных мантисс результат может получится ненормализованным (правое нарушение нормализации). Например, в прямом коде MX=0.10...0, MY=0.10...0, MZ=0.010...0, где |MZ|<1/2. В этом случае необходимо результат MZ сдвинуть влево, от порядка результата pZ вычесть единицу, проверить на отрицательное переполнение порядка. При делении может происходить левое нарушение нормализации, когда после пробного вычитания z0=1. В этом случае мантиссу результата сдвигают вправо, к порядку прибавляют единицу, проверяют на положительное переполнение. Форматы данных Данные, размещаемые в устройствах ЭВМ, могут иметь различные форматы, как показано на рис. 1.2. В этих форматах могут находиться числа, указатели адреса и закодированные символы. Числа часто представляются как целые в разрядной сетке 8, 16, 32, 64 бита, где они размещаются в форме с фиксированной запятой после младшего разряда со знаком (S) или без знака. Если число занимает 16 бит, то это целое слово (ЦС), если 32 бита, то оно имеет формат короткого целого (КЦ) – двойное слово; и если оно занимает формат в 64 бита, то это – длинное целое (ДЦ). В формате двоичных целых чисел без знака все разряды считаются значащими и представление чисел лежит в диапазоне от 0 до 255 (байт), до 65535 (ЦС), 4Г-1 (КЦ) и 264-1 (ДЦ) соответственно десятичной системе счисления. Двоичные числа со знаком представляются в дополнительном коде, и их величина лежит в диапазоне -2m X +(2m -1), где m = 7 (байт), 15 (ЦС), 31 (КЦ), 63 (ДЦ) при представлении в форматах байт, слово, двоичное слово и в разрядной сетке 64 бита. Так, в формате “слово” мантиссу числа можно представлять с абсолютной точностью в интервале -32768 до +32767(10) в дополнительном коде с фиксированной запятой после младшего разряда. Числа с плавающей запятой могут иметь в ОЗУ два формата: вещественное с одинарной точностью (ОТ) или вещественное с двойной точностью (ДТ). В этих форматах знак мантиссы числа непременно размещается в старшем разряде старшего байта, за ним располагается смещенный беззнаковый порядок Е (Exponent) размерностью 8 бит (ОТ) или 11 бит (ДТ). В оставшихся младших разрядах размещается в прямом коде нормализованная мантисса с весами значащих цифр от 2-1 до 2-23 или 2-52 (ДТ). Величина Е (характеристика) определяется по формуле E = p + pmax, где p – истинный порядок, целое число в прямом коде со знаком; |pmax| – величина смещения, для соответствующих форматов равная +127, +1023, +16383(10). Так, если в формате ОТ размещать истинный порядок со знаком, то представление порядка лежит в диапазоне 1.1111111 0.1111111 (-127 +127). При этом минимальный порядок будет равен -127, а максимальный +127(10). Отсюда, с учетом смещения, характеристика числа лежит в диапазоне EminEmax или 0000 0000 1111 1111, где код 0…0 = Emin соответствуют наибольшему отрицательному порядку, а код 1…1 = Emax наибольшему положительному порядку. В МП код 0…0 используется для представления нуля, для которого и все разряды мантиссы (М) также принимаются равными нулю, а код 1…1 используется для представления , у которой мантисса, с учетом левого сдвига, равна 1,0…0, а знак S указывает на +(S = 0) или -(S = 1) бесконечность. Поэтому диапазон представления чисел, отличных от нуля и бесконечности, определяется характеристикой, лежащей в интервале 00000001 11111110 в формате ОТ или 00000000001 11111111110 в формате ДТ. Смещенный порядок намного упрощает выполнение операций сравнения и “больше-меньше” чисел с плаваюшей запятой.  Рис. 4 Мантисса в форматах ОТ и ДТ нормализована и сдвинута на один разряд влево, лежит в диапазоне 1,0…0 до 1,1…1.Так как старшая цифра в разряде 20 в ней всегда равна единице, в форматах ОТ и ДТ она не присутствует (опущена). При передаче в сопроцессор чисел формата ОТ и ДТ они аппаратно преобразуются в расширенный формат (РТ), где цифра мантиссы из разряда 20 восстанавливается путем сдвига мантиссы вправо и занимает место в разряде с весом 2-1 (левый старший разряд мантиссы). РТ используется только в сопроцессоре и в МП для внутренних операций, промежуточных результатов и констант. Поэтому наибольший диапазон представления чисел ЭВМ может быть получен в формате ДТ, где он составляет примерно от 2,23 10-308 до 1,79 10308. Для представления десятичных чисел в двоичной системе счисления (BCD) используется код 8, 4, 2, 1, в котором каждой десятичной цифре отводится тетрада с весами в разрядах 23, 22, 21, 20, т.е. 8, 4, 2, 1. Такое кодирование в прямом коде позволяет представить десятичные цифры Цi 0,1,2, …,9 кодами 0000, 0001, …,1001. Если десятичные цифры кодировать для целых чисел, то младшая тетрада будет соответствовать цифре (Ц0) с весом 100, более старшая (Ц1) с весом 10+1 и т.д. В формате один байт могут быть закодированы только две десятичные цифры без знака - упакованный формат (УПК) или одна цифра Ц0(Ц1=0) - неупакованный формат (НУПК). Арифметические операции с числами BCD можно осуществлять только в целочисленном устройстве. В сопроцессоре формат УПК из 18 десятичных цифр и одного бита знака в старшем байте используется в операциях загрузки, сохранения и передачи последовательности символов для печати. Указатели используются для определения адреса команд или операндов в сегментных (близкий) или межсегментных (далекий) передачах. Близкий указатель содержит величину смещения, которая суммируется с базовым адресом сегмента. Далекий указатель загружает селектор в соответствующий сегментный регистр, и уже к новому адресу сегмента суммируется смещение, которое и является линейным адресом операнда или команды. В цепочки объединяются данные, хранящиеся по соседним адресам. Элементами цепочек могут быть биты, байты, слова или двойные слова. Цепочки используются для пересылки части файлов из одной области памяти в другую, поиска конкретных значений внутри цепочки, сравнений цепочек и других операций преобразования баз данных. Длина цепочки может быть практически любой, размещаемой внутри области памяти ЭВМ. При работе с числами и при ошибках программирования могут возникнуть особые случаи прерывания вычислений ЭВМ по следующим причинам: - в формате присутствует денормализованное вещественное число, при котором Е = Еminи мантисса не равна нулю; - в формате присутствуют не числа, когда Е = Еmax, а мантисса равна любому значению кроме 1,0 … 0 (например, результат, полученный от деления на нуль); - результат операции не размещается в разрядной сетке ЭВМ (переполнение) или результат слишком мал (антипереполнение); - результат не может быть представлен точно в предписанном формате (например, деление на 1/3). 6. Стадии выполнения команды и способы адресации В ЭВМ используются одно-, двух- или трехадресные команды [16]. Самой быстродействующей и наиболее гибкой для программирования является трехадресная команда вида

В структуре этой команды имеется поле кода операции (КОП) и три адреса операндов А1, А2, А3. С помощью этой команды легко программируются многие операции. Например, сложение Z = X + Y можно запрограммировать так: в поле КОП закодировать адрес микропрограммы сложения, находящейся в постоянной памяти УУ, в А1 закодировать адрес операнда Х, в А2 – Y, а в А3 разместить адрес, куда направить результат сложения. Недостатком трехадресных команд (трехадресных ЭВМ) являются значительные затраты оборудования на размещение адресов А1, А2, А3 и наибольшая разрядность шины данных. Для устранения этих недостатков используют двух- или одноадресные команды вида

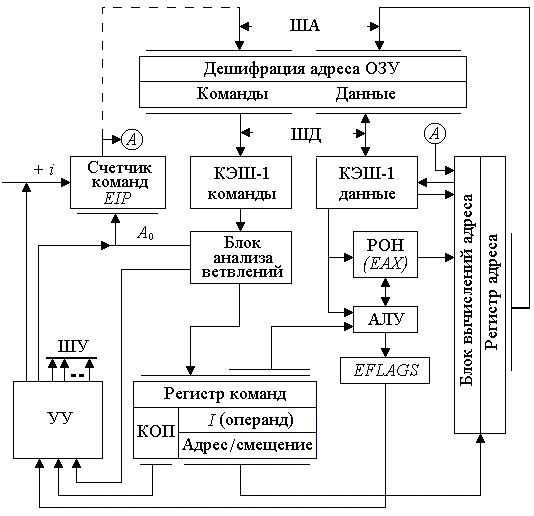

При двухадресных командах один из адресов фиксируют. Например, результат операции передается по адресу (на место) первого операнда. При этом значение первого операнда, естественно, стирается. При одноадресной команде для выполнения операций фиксируют и место нахождения первого операнда, используя, например, специальный регистр – аккумулятор (ЕАХ) – или верхнюю ячейку (вершину) стековой памяти. После выполнения команды, если она не последняя, процессор извлекает следующую, которая обычно располагается по более старшему адресу (естественная адресация). Для определения ее адреса используется счетчик команд (IP или EIP), значение которого увеличивается на i =1, 2, … каждый раз до адреса следующей команды естественного порядка. Если при ветвлениях в алгоритме возникает необходимость перейти к выполнению команды, отличной от естественного порядка, используются одноадресные управляющие команды условного или безусловного перехода. При безусловном переходе содержимому EIP всегда присваивается поле адреса команды А0. При командах условного перехода анализируется состояние соответствующего флага регистра EFLAGS, который обрабатывается устройством управления по коду поля КОП. В зависимости от значения флага EIP может быть присвоено А0 или EIP + i. Укрупненная схема командного управления ЭВМ показана на рис. 1.3. Для считывания операндов и команд в процессор кроме прямой адресации, при которой поле адреса указывает на ячейку памяти (регистр МП), где хранится операнд или команда, может использоваться также непосредственная, косвенная или ассоциативная адресация. При непосредственной адресации операнд I располагается в самой команде вида

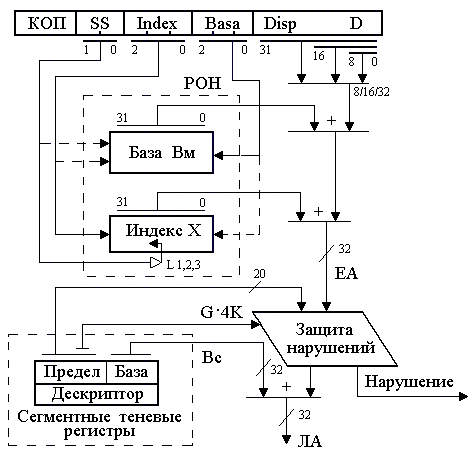

Этот операнд (константа) может быть использован операционным блоком (АЛУ) для вычислений, и не требуется дополнительного обращения к ОЗУ. При косвенной адресации в команде располагается адрес ячейки или регистра МП, где хранится адрес операнда. При ассоциативной адресации в поле адреса размещается ключ (признак, тэг) поиска или ассоциация и для поиска используются микрооперации сравнения информации “по содержанию”, а не дешифрация адреса в ОЗУ. В новых МП система команд постоянно совершенствуется и дополняется, сохраняя программную совместимость с младшими моделями. В настоящее время в i486, Pentium принята структура команды, показанная на рис. 6, и длина команды может достигать 16 байт при 32-битной адресации. Обязательной для каждой команды является наличие поля КОП размерностью в 1 или 2 байта. Все другие поля команды могут отсутствовать или расширяют функции адресации или назначение команды. Так, наличие перед командой одного из префиксов группы изменяет ее функции, определенные по умолчанию, следующим образом: - REP(в группе REPE / REPZ, LOCK, REPNE / REPNZ) – распространяет выполнение операции (КОП) на все элементы цепочки; - AS – изменяет разрядность 16 (32)-битного эффективного адреса, обрабатываемого командой, на 32 (соответственно в скобках на 16)-битный адрес; - OS – изменяет разрядность операнда в 16 (32) бит на разрядность в 32 (16) бит; - SO – указывает новый сегментный регистр для команды из группы возможных.  Рис. 5. Схема командного управления ЭВМ

Префиксы Префиксы

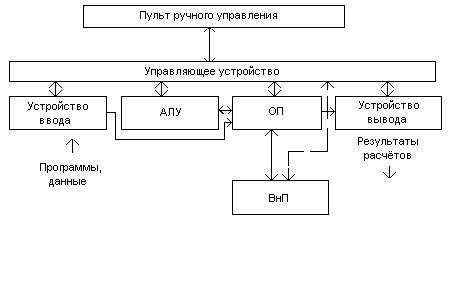

Рис. 6. Обобщенная структура команды Префиксы могут располагаться перед командой в любом порядке, только по одному из группы. В следующих двух байтах команды ModR / M и SIB кодируются дополнительные сведения о коде операции и способе вычисления адресов операндов. Поля этих байтов имеют следующие назначения: - mod и r / m в различных комбинациях определяют 8 регистровых (mod = <11>) и 24 индексных типа адресации; - reg / коп определяет либо номер одного из 8 регистров РОН, либо расширяет на 3 бита поле КОП; - r / m определяет либо номер РОН, в котором находится операнд, либо с полем mod кодирует 32 типа адресации. В случае 32-битной адресации байт ModR / M содержит информацию о необходимости использования дополнительных кодов из байта SIB, состоящего из следующих полей: - SS – масштабный множитель (00 – х1, 01 – х2, 10 – х4, 11 – х8); - index – поле 3-битного кода номера РОН, который является индексным регистром; - base – поле номера РОН, который содержит базовый адрес. За байтом Mod R / M или SIB команды часто следует поле смещения Disp. Это поле указывает на “удаление” операнда от адреса, заданного в базовом регистре команды. В зависимости от кода поля mod (00, 01, 10) величина смещения занимает 1, 2 или 4 байта. В поле I команды иногда размещается непосредственный операнд, который в зависимости от КОП может располагаться в 8 / 16 / 32 битах последнего поля команды. Данные, участвующие в вычислениях, обычно располагаются в ОЗУ. Для задания места нахождения операндов наиболее широко в адресных ЭВМ используются непосредственная, прямая и косвенная адресации. При непосредственной адресации 8 / 16 / 32-битный операнд размещается в поле I команды и после извлечения команды из ОЗУ он сразу участвует в операции. Так, команда сложения addax, 8AD5h в поле I содержит двухбайтный код <1000101011010101>, который МП использует для сложения с содержимым регистра АХ. Недостатком этой адресации является то, что команда работает с жестко закрепленными данными (константой). При прямой адресации к памяти в команде закодирован адрес ячейки ОЗУ, в которой находится операнд. При обращении к ОЗУ поле адреса Аi команды (плюс адрес сегмента) считывается в регистр адреса и затем передается на ША. Код из ША дешифрируется и возбуждает соответствующую ячейку ОЗУ для взаимодействия с ШД. Так, при чтении операнд из ячейки передается на ШД, затем в кэш-1 и АЛУ для участия в выполнении КОП команды. При записи результат операции по ШД передается в ячейку (рис. 4). Недостатком прямой (абсолютной) адресации к памяти является значительная разрядность адресной части команды, которая увеличивается с увеличением числа ячеек ОЗУ и удваивается при двухадресной команде. В качестве примера команды с абсолютной адресацией может быть команда вида moveax, [21051944], которая загружает аккумулятор содержимым ячейки 21051944h. В этой команде адрес 21051944h увеличивает ее длину на 32 бита. Разновидностью прямой являются неявная, регистровая и адресация ввода / вывода. Отличие регистровой адресации от прямой к памяти заключается в том, что в поле Аi кодируется короткий адрес регистра РОН, в котором находится операнд. При этом длина команды уменьшается и МП не обращается к ОЗУ за операндом, тем самым уменьшается время выполнения операции. Однако перед выполнением команды операнд должен находиться уже в соответствующем РОН. Для организации регистровой адресации РОН EAX, ECX, EDX, EBX, ESP, EBP, ESI, EDI присваиваются соответственно трехбитные адреса 000, 001, …, 111 и если в поле reg располагается, например, адрес регистра <010>, то это означает, что команда выполняет операцию с участием операнда регистра EDX. Например, команда с регистровой адресацией mov edx, ecx двухадресная, передает содержимоеECXв РОН EDX. При неявной адресации адресное поле отсутствует. Операнд располагается в устройстве, которое неявно задается полем КОП. После дешифрации этого поля микропрограмма УУ указывает место операнда (например, регистра AL, однобайтной команды ааа). Команды неявной адресации имеют наименьшую длину, но узко специализированы. Для обмена с внешними устройствами любая ЭВМ с МП i86, …, i486, Pentium имеет определенное число буферных регистров - портов, через которые и осуществляется процесс ввода / вывода информации. Каждому порту присваивается свой адрес в диапазоне от 0 до 64К-1. Для обмена с портами предназначены команды ввода in или вывода out, где в качестве приемника или источника зафиксирован EAX/ AX / AL. В этих командах используется прямая адресация ввода / вывода, например, inax, 22 - загрузить AX содержимым регистра из 22h порта или косвенная адресация ввода / вывода с обращением за адресом порта в регистр DX (outdx, ax - вывести AX в регистр порта, адрес которого занесен в DX). Заметим, что команды ввода / вывода кроме поля КОП имеют еще второй байт адреса порта или один байт КОП с использованием для адресации содержимого регистра DX. Причем номера портов выравниваются по границам передаваемых данных. Так при 32-битных операциях они нумеруются 0, 4, 8, …, 252, …, 65532. Существенным недостатком прямой адресации является необходимость закрепления операндов за определенными устройствами и номерами ячеек (статическое распределение памяти). С целью расширения возможности хранения данных во всех областях ОЗУ, организации контроля и защиты от неправильного использования областей и мультизадачности вычислений в ЭВМ введены динамический режим распределения памяти, косвенная и относительная адресации операндов (рис. 6). Для этого вся адресуемая область разбивается на сегменты и страницы. Каждому сегменту присваивается начальный адрес (база) и верхний адрес (база + предел). В дальнейшем адресация в командах осуществляется относительно базы сегмента (эффективный адрес ЕА). Такая адресация называется базовой. В МП 8086 / 88 для хранения базовых адресов используются сегментные регистры CS, DS, SS, ES. В процессорах i486, Pentium базовые адреса и пределы сегментов хранятся в дескрипторах, которые размещаются в теневых сегментных регистрах (CS), (DS), (SS), (ES), (FS), (GS). Базовый адрес массива и при необходимости индекс операнда массива хранятся в РОН МП. Причем индекс массива можно масштабировать путем умножения его на величину 21, 22, 23. Масштабирование эквивалентно микрооперациям сдвига содержимого индексного регистра влево на величину L1, L2, L3. Тогда в общем случае линейный адрес операнда с использованием косвенной адресации вычисляется по формуле ЛА = ВС + (Х 2<SS> + (ВМ +D)). Содержимое полей команды дешифрируется и устанавливается значение масштаба <SS>, номеров регистров РОН, где хранятся базовый адрес массива ВМ и индекс Х массива. Затем базовый адрес суммируется с содержимым смещения Disp поля команды ВМ + D. Одновременно величина в Х сдвигается на 0, 1, 2, 3 разряда влево в соответствии со значением <SS>. Затем величина индексного регистра Х суммируется с ВМ+ D и тем самым вычисляется эффективный адрес операнда, т. е. его удаление от начала сегмента ЕА = Х 2<SS> + (ВМ + D).  Рис. 7. Схема вычисления 32-битного линейного адреса Величина ЕА сравнивается с величиной предела сегмента. Если ЕА не выходит за размеры сегмента, эффективный адрес суммируется с базой сегмента. Тем самым определяется линейный адрес ЛА операнда, который используется для определения физического адреса. ВR- и V-режимах этот линейный адрес совпадает с физическим адресом ФА и передается в регистр адреса. В P-режиме этот адрес может быть больше размерности ОЗУ и линейный адрес с учетом страничного преобразования обычно преобразуется в физический адрес. В зависимости от составляющих BM, X, D, 2<SS>, которые могут присутствовать или отсутствовать в микрооперациях вычисления адреса, различают базовую, индексную и их разновидности со смещением адресации операндов. При базовой адресации в команде отсутствует смещение и не используется индексирование. ЕА задается только базовым РОН кроме ESP. Искомый РОН в мнемонике описания команды заключается в скобки. Например, moveax, [ecx] - передать в EAX двойное слово из ОЗУ с адресом = база сегмента + ECX. При базовой адресации со смещением ЕА определяется суммированием содержимого РОН, закодированном в поле base, с величиной 8 / 16 / 32-разрядного смещения в команде. Смещение в команде является целым числом со знаком. Например, команда moveax, [esi + D] осуществляет передачу в ЕАХ содержимого ячейки ОЗУ с адресом, равным сумме базы сегмента РОН ESI и смещения в поле команды + D. Отличительной особенностью способа индексной адресации со смещением и масштабированием от базовой адресации со смещением является возможность масштабирования индексного адреса Х путем умножения его на 1, 2, 4 или 8. При множителе 1 эти способы адресации не отличаются. При множителях 2, 4 или 8 масштабирование (сдвиг влево на один - L1, два - L2 и три разряда - L3) позволяет осуществлять вычисление адреса с учетом размера элементов массива или задания их порядка обработки командой. Например, команда movecx, [esi 4] + 53 передает двойное слово, которое находится в сегменте данных с эффективным адресом L2 ESI (31, 0) + 53h. Наиболее сложным способом адресации является базовый/индексный с масштабированием и смещением. Для вычисления адреса в этом способе участвуют два РОН. Один из РОН содержит индекс, который масштабируется. Смещение размером в 8, 16 или 32 бита располагается в команде. Например, команда addeax, [ebx][edi 8] + 547671 осуществляет сложение содержимого EAX с элементом массива, имеющим эффективный адрес ЕА = EBX (31, 0) + L3 EDI (31, 0) + 547671h. Использование команд с базовой / индексной адресацией упрощает программирование вычислений, уменьшает разрядность команд и позволяет размещать в операционной системе данные в любых освобождающихся областях ОЗУ, изменяя при этом только базовые адреса. Для уменьшения времени вычисления линейного адреса используется конвейерный параллельный способ дешифрирования команды и вычисления адресов, что позволяет многие команды на последней ступени обработки в МП Pentium выполнять за один такт синхронизации. В рассмотренных способах адресации место операнда кодируется в команде и закреплено за программой. При смене базовых адресов изменяются и физические адреса расположения операндов в памяти. Это усложняет обмен данными между программами и организацию программных прерываний. Для упрощения обмена между программами, прерываний при обращении к подпрограммам и “безадресного” поиска и размещения операндов в ЭВМ используется стековая адресация. Под стек отводится часть ОЗУ (сегмент стека с базовым адресом в регистре SS или (SS)), которая участвует в операциях МП с использованием реверсивного счетчика – указателя ESP / SP. Содержимое указателя ESP / SP (вершина стека) используется командами как поле адреса операнда. При записи в стек командами push величина ESP / SP уменьшается, а при чтении командами pop указатель увеличивается на величину, равную длине операнда в байтах, после выполнения команды. Например, команды push ecx передает в ОЗУ содержимое ECX по ЕА = ESP (31,0). Принципы действия ЭВМ Упрощенная структура ЭВМ представлена на рис. 8 ЭВМ содержит следующие основные устройства: арифметическо-логическое устройство, память, управляющее устройство, устройство ввода данных в машину, устройство вывода из нее результатов расчета и пульт ручного управления. Арифметическо-логическое устройство (АЛУ) производит арифметические и логические преобразования над поступающими в него машиинными словами,т.е. кодами определенной длины, представляющими собой числа или другой вид информации. Количество разрядов в машинном слове обычно совпадает с количеством разрядов в основных регистрах АЛУ. Память хранит информацию, передаваемую из других устройств, в том числе поступающую в машину извне через устройство ввода, и выдает во все другие устройства информацию,необходимую для протекания вычислительного процеса.Память машины в большинстве случаев состоит из двух существенно отличающихся по своим характеристикам частей: быстродействующей основной или оперативной (внутренней) памяти (ОП) и сравнительно медленно действующей , но способной хранить значительно больший объем информации внешней памяти (ВнП). Оперативная память содержит некоторое число ячеек, каждая из которых служит для хранения машинного слова или его части. Ячейки нумеруются, номер ячейки называется адресом.  Рис. 8. Структура электронной цифровой вычислительной машины. Фон-Нейманавская модель ЭВМ В запоминающих устройствах, реализующих в ЭВМ функцию памяти выполняются операции считывания хранимой информации для передачи в другие устройства и записи информации, поступающей из дргих устройств. При считывании слова из ячейки содержимое последней не меняется и при необходимости слово может быть снова взято из той же ячейки. При записи хранившееся в ячейке слово стирается и его место занимает новое. Непосредственно в вычислительном процессе участвует только ОП, и лишь после окончания отдельных этапов вычислений из ВнП в ОП передается информация, необходимая для следующего этапа решения задачи. Управляющее устройство (УУ) автоматически без участия человека управляет вычислительным процессом, посылая, всем другим устройствам сигналы, предписывающие им те или иные действия, в частности включает АЛУ на выполнение нужной операции. Алгоритмом решения задачи численным методом называют последовательность арифметических и логических операций, которые надо произвести над исходными данными и промежуточными результатами для получения решения задачи. Поэтому алгоритм можно задать указанием, какие следует произвести операции, в каком порядке и над какими словами. Описание алгоритма в форме, воспринимаемой ЭВМ, называется программой. Программа состоит из отдельных команд.Каждая команда преписывает определенное действие и указывает, над какими словами (операндами)это действие производится. Программа представляет собой совокупность команд,записанных в определенной последовательности, обеспечивающей решение задачи на ЭВМ. Чтобы устройство управления могло воспринимать команды, они должны быть закодированы в цифровой форме. Автоматическое управление процессом решения задачи достигается на основе принципа программного управления, являющегося основной особенностью ЭВМ. Другим важнейщим принципом является принцип хранимой в памяти программы. Согласно этому принципу команды программы, закодированные в цифровом виде, хранятся в памяти наравне с числами. В команде указывается не сами участвующие в операциях числа, а адреса ячеек ОП, в которых они находятся, и адрес ячейки, куда помещается результат операции. Поскольку программа храниться в памяти, одни и те же команды могут нужное число раз извлекаться из памяти и выполняться. Более того, так как команды представляются в машине в форме чисел, то над командами как над числами машина может производить операции ("модификация команд"). Использование электронных схем, принципов программного управления и хранимой в памяти программы позволило достигнуть высокого быстродествия и сократить во много раз число команд в программах решения задач, содержащих машинные циклы, по сравнению с числом операций, которые производит машина при выполнении этих программ. Команды выполняются в порядке,соответствующем их расположению в последовательных ячейках памяти, кроме команд безусловного и условного переходов, изменяющих этот порядок соответственно безусловно или только при выполнении некоторого условия, обычно задаваемого в виде равенства нулю,положительного или отрицательного результата предыдущей команды или отношения типа >,=,< для указываемых командой чисел. Именно благодаря наличию команд условного перехода ЭВМ может автоматически изменять соответствующим образом ход вычислительного процесса, решать сложные логические задачи. Перед решением задачи на ЭВМ программа и сходные данные должны быть помещены в память. Предварительно эта информация наносится на магнитные носители путем соответствующего намагничевания участков их поверхностей. Затем при помощи устройств ввода программа и исходные данные считываются с магнитных носителей и переносятся в ОП. Информация может также вводится с клавиатуры и других устройств ввода. Устройство вывода служит для выдачи из машины результатов расчета, например , путем распечатывания на принтере или отображения на экране. При помощи пульта управления оператор пускает и останавливает машину, а при необходимости может вмещаться в процесс решения задачи. Представленная на рис. 2 структура (модель) вычислительной машины, получившая название Фон-Неймановской, благодаря ее изящной простоте и большей гибкости при управлении вычислительным процессом с самых первых шагов электронной вычислительной техники и по сей день доминирует при построении различных ЭВМ. Однако в последние годы конструкторы ЭВМ, стремясь достигнуть существенного повышения производительности, в ряде случаев отходят от модели Фон-Неймана. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||