Лекции_Вычислительные машины_new. Лекция История развития вычислительной техники

Скачать 5.16 Mb. Скачать 5.16 Mb.

|

|

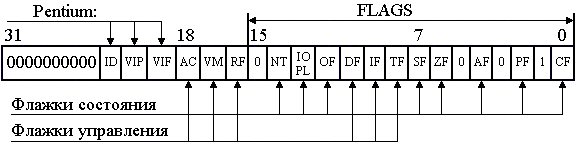

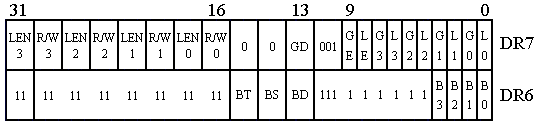

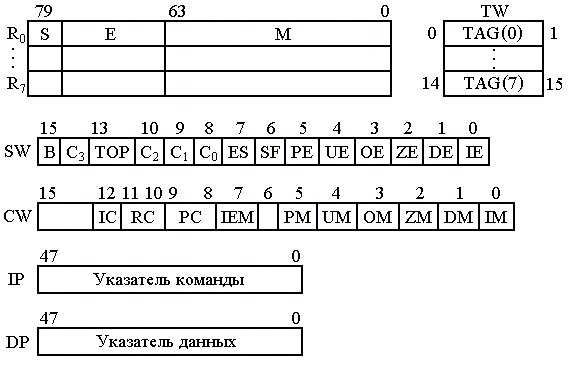

В 1986 г. на базе МП Intel 80286 IBM изготавливает в корпусе XT по новейшей технологии с использованием 16-разрядной шины ISA компьютер AT XT- 286. В процессоре Intel 80286 вводится «защищенный режим». Этот новый режим используют для размещения данных и команд в различные сегменты, а содержимое сегментных регистров – как селекторы или указатели адреса дескриптора. Дескриптор хранит 24-битный базовый адрес, позволяющий адресовать до 16 Mб физической памяти, поддерживает виртуальное управление памятью и различные механизмы защиты. Это проверка границы сегмента, опции сегментов только для чтения и только для записи и четыре уровня привилегий для защиты кода операционной системы от приложений или программ пользователя. Более того, переключение задач и локальная таблица дескрипторов позволяет операционной системе защитить приложения или программы пользователя друг от друга. После модели AT PC-XT 286 фирма IBM прекращает выпуск XT и все её компьютеры с системными шинами MCA, PCI, VL-bus относятся к одной из групп класса AT, семейства PS/2. Производительность компьютера XT-286 примерно в 3 раза выше моделей XT. ОЗУ емкостью 640 Кб доводилось до 16 Мб установкой плат расширения. В нем установлен НЖМД на 20 Мб и один из накопителей НГМД формата на 3.5" или 5.25" емкостью от 720 Кб до 1.44 Мб. Кроме DOS все AT могут работать с операционной системой Windows. В начале 1987 г. на базе МП 386DX фирма IBM выпустила компьютер PS/2 модели 80 с тактовой частотой 20 МГц, который стал настоящей сенсацией из-за высокой производительности вычислений. Помимо высокого быстродействия достоинством МП 386 является возможность работать в реальном, защищенном и виртуальном режимах. Реальный режим, как и для 286-го процессора, это базовый режим совместимости с 8086. Компьютер в этом режиме ("Turbo PC") быстрее осуществляет вычисления с ОЗУ 640 Кб и программами для DOS. В архитектуру процессоров Intel, начиная с 80386, для вычислений и адресации памяти вводятся 32-разрядные регистры (архитектура IA-32) общего назначения (GP), подходящие как для хранения адресов, так и для операндов. Часть каждого 32‑разрядного регистра для обеспечения совместимости имеет значение одного 16-разрядного регистра предыдущих двух поколений процессоров. Был введен новый «виртуальный режим» 8086 для повышения быстродействия выполнения программ на новой 32-разрядной машине, созданный ранее для процессоров 8086 и 8088. 32-разрядная адресация позволяет адресовать к 4 Гб адресного пространства, и также увеличить размер каждого сегмента до 4 Гб. Первоначальные инструкции х86 были расширены новыми инструкциями с 32‑разрядными операндами и формой адресации. В процессоре Intel 386 также вводится метод для управления виртуальной памятью и страничная организация памяти, с фиксированным размером страницы 4 Kб, и возможность определения сегментов размером в 4 Гб. Процессор Intel 386 был первым архитектуры IA-32, в который включили 6 параллельно работающих блоков: - шинный интерфейс (доступ к памяти и устройствам ввода/вывода других блоков); - блок предварительной выборки кода (получает объектный код из шинного интерфейса и помещает его в 16‑байтную очередь); - блок декодирования инструкций (декодирует объектный код из блока предварительной выборки в микрокод); - блок выполнения (выполняет инструкции микрокода); - сегментный блок (переводит логические адреса в линейные адреса и выполняет проверку защиты); - блок страничного преобразования (переводит линейные адреса в физические, выполняет проверку страничной защиты и содержит кэш с информацией о 32 наиболее часто используемых страницах). Защищенный режим МП 386, который аналогичен МП 286, называется "естественным", т.к. оба МП разрабатывались для OS/2 и Windows NT, предназначенных для работы в этом режиме. Дополнительные возможности адресации памяти в защищенном режиме появились благодаря новому менеджеру памяти (MMU), который использует страничную организацию памяти и программные переключения. В новом виртуальном режиме МП 386 имитирует работу МП 8086. При этом создается несколько независимых областей (отсеков) памяти с полным набором функциональных возможностей DOS. Такие отсеки, которые называются "виртуальными машинами", позволяют организовать многозадачные вычисления с использованием OS/2 и Windows. Было разработано несколько типов персональных компьютеров с модификациями МП 386 – SX, SL, DX, работающих с таковыми частотами 16, 20, 25, 33 МГц и сопроцессором 80387, который устанавливался отдельно от МП на системной плате и выполнял операции с плавающей запятой параллельно процессору ЭВМ. Следующим шагом в разработке компьютеров явилось использование в их составе МП 486 следующих разновидностей: - 486 SX без сопроцессора; - 486 DX со встроенным сопроцессором; - 486 DX2 с удвоением внутренней частоты вычислений и сопроцессором; - 486 DX4 с утроенным быстродействием и сопроцессором. Тактовая частота первого МП 486 составляла 25 МГц, которая в более поздних МП увеличилась до 33, 50, 66 МГц. Структура процессора 486 подробно рассматривается ниже. В процессор Intel 486 добавлена возможность одновременного выполнения до пяти инструкций на разных стадиях с помощью расширения блока декодирования инструкций и операционного блока выполнения в пять конвейерных стадий, где каждая стадия работает параллельно с другими. Каждая стадия может выполнить свою работу над одной инструкцией за один такт. Также к процессору Intel 486 был добавлен кэш L1 8 Кб для увеличения числа инструкций, которые могут быть выполнены за один такт. В процессоре Intel 486 впервые в CPU было интегрировано устройство с плавающей запятой (FPU) и добавлены новые инструкции для поддержки кэша L2 и мультипроцессорности. Позже в процессор Intel 486 SL были введены функции поддержки энергосбережения и системного управления для ноутбуков PC, работающих от батарей. В процессор Intel Pentium для достижения суперскалярной производительности была добавлена вторая линия конвейерной обработки (2 линии конвейера, известные как U и V, которые вместе могут выполнять две инструкции за один такт). Также был удвоен кэш L1, 8 Кб для кода и другие 8 Кб для данных. Для увеличения производительности в циклах программы было добавлено прогнозирование ветвлений. Основные регистры остались 32-битные, но добавилась внутренняя шина данных 128 и 256 бит, для увеличения скорости внутренней передачи данных, и внешняя шина данных была увеличена до 64 бит. Был добавлен дополнительный программируемый контроллер прерываний APIC для поддержки систем с несколькими процессорами Pentium. Следующей разработкой Intel был процессор Pentium Pro, который имеет трехходовую суперскалярную архитектуру, это значит, что процессор может выполнять 3 инструкции за каждый такт. В суперскалярной реализации процессора Pentium Pro предусматривается «динамическое выполнение» (анализ потоков микрокодов, нестандартное выполнение, улучшенное прогнозирование ветвлений и прогностическое выполнение). Три устройства декодирования инструкций работают параллельно, декодируя объектный код в более малые операции, называемые “микрокодом”. Они попадают в накопитель инструкций, который при отсутствии взаимосвязи может быть реализован пятью параллельными блоками выполнения (2 АЛУ, 2 FPU и 1 блок для работы с памятью). Блок сброса изымает выполненный микрокод в порядке расположения в программе, учитывая все ветвления. Мощность процессора Pentium Pro дополнительно расширена кэшем L2 до 256 Кб, который находится в корпусе МП и использует выделенную 64-разрядную шину. Кэш L1 в нем двухпортовый, кэш L2 поддерживает до 4 параллельных обращений. Также в процессоре Pentium Pro шина адреса увеличена до 36 бит, что позволяет адресовать до 64 Гб ячейкам физического адресного пространства. В процессоре Pentium II к архитектуре процессора Pentium Pro добавлены команды MMX. Для процессора Pentium II вводится новая спецификация установки в системную плату: слот 1 и слот 2. В этой новой спецификации кэш L2 выносится из кристалла МП. В процессоре Pentium II увеличен кэш данных L1 и кэш инструкций L1 до 16 Кб каждый, а размер кэша L2 может быть 256, 512 Кб и 1 или 2 Мб (только для слота 2). Процессоры слота 1 используют для кэша L2 “половинную тактовую частоту” шины, а процессоры слота 2 работают на частоте процессорной шины. Процессор Pentium III является последним, базирующимся на архитектуре Р6. В 10-стадийный процессор Pentium III введены 70 новых инструкций. Процессор Pentium III внес в архитектуру IA-32 расширения SSE. В результате стали доступны новые 128-разрядные регистры и SIMD операции над упакованными операндами с плавающей запятой с одинарной точностью. Процессор Pentium 4 изготовлен с использованием 20-стадийного конвейера, позволяющего использовать более высокие частоты синхронизации и архитектуру NetBurst. Его ядро создано на основе 32-битной микроархитектуры IA-32, обеспечивающей программную совместимость х86, но в нем реализованы 128-битные регистры для параллельной обработки операций над числами, представленными в формате с плавающей запятой. Функциональная схема ЭВМ на базе процессоров Pentium рассматривается в гл. V. В разработках ЭВМ используются видеоплаты SVGA различных фирм с общим стандартным интерфейсом VESA ассоциации производителей. Достоинством стандарта VESA BIOS является то, что для работы с SVGA различных фирм программист может пользоваться одним единственным драйвером, который обеспечивает почти все существующие на сегодняшний день разрешающие способности и цветовые возможности дисплеев, вплоть до разрешения 1280 1024 точек при 16777216 (24-разрядное представление) цветов. Особенностью изготовления персональных компьютеров на базе МП 486, Pentium является возможность расширения и использования в их составе устройств, изготовленных в различных фирмах и странах. Совместимость обеспечивается соблюдением как стандартов ассоциации производителей, так и "подстройкой" BIOS под эти устройства. Лекция 6. Регистры процессора Как видно из табл. 2.2, важной характеристикой МП и процессоров фирмы Intel является разрядность регистров. Начиная с МП Intel 386 и до настоящего времени фирма Intel придерживается 32-разрядной архитектуры IА-32, обеспечивающей программную совместимость х86 различных модификаций ЭВМ, построенных на базе МП Intel 8086 и выше. Регистры процессора, как сверхбыстродействующая память, предназначены для хранения операндов и команд, сведений о состоянии вычислительного процесса, обмена данными между МП, ОЗУ и портами, организации адресации и взаимодействия между блоками. По выполняемым функциям они подразделяются на пользовательские, системные и регистры сопроцессора [21, 13]. В 16 регистров пользователя (прикладного программиста) включены 8 регистров общего назначения, 6 сегментных регистров, регистр (счетчик) команд и регистр флагов. Определенные буквы в наименованиях регистров несут смысловое значение: - E (Extended) – расширенный, т.е. 32-битный; - H (High) – старший байт регистра, разряды (15, 8); - L (Low) – младший байт, разряды (7, 0). Описание регистров общего назначения: - EAX/AX/AL – аккумулятор, регистр для операций ввода/вывода через порты, вместе с DX выступают в качестве неявных операндов в командах умножения и деления; AL – регистр двоично-десятичных операций; - EBX/BX – регистр для хранения базовых адресов при работе с данными; - ECX/CX/CL – счетчик, используется при организации циклов; - EDX/DX/DL – регистр данных, хранит данные по умолчанию, адрес порта при операциях ввода/вывода, используется в командах умножения и деления; - EBP/BP – указатель базы при работе с данными в стековых структурах; - ESP/SP – указатель (реверсивный счетчик) стека; - ESI/SI – адресный регистр – индекс источника; - EDI/DI – адресный регистр – индекс приемника. Вместе с SI используется в цепочечных инструкциях обработки массивов, хранит смещения (индексы) относительно базы (начала массива). Сегментные регистры CS, SS, DS, ES, FS, GS используются для сегментной адресации. Регистры FS и GS появились в составе МП, начиная с i386. Регистр-указатель команд EIP/IP предназначен для определения адреса следующей команды. Для организации условных переходов в программах и хранения состояний вычислительного процесса предназначен регистр флагов EFLAGS, структура которого приведена на рис. 2.1.  Рис. 2.1. Структура регистра EFLAGS Флаги состояния при выполнении операций принимают следующие значения: - CF – флаг переноса. CF = 1, если при выполнении арифметической операции возник перенос в старший разряд или заем из старшего разряда. В разных форматах операций старшим битом может быть 7, 15 или 31; - PF – флаг паритета (четности). PF = 1, если после выполнения операции в младшем байте имеется четное число единиц, иначе PF = 0; - AF – флаг вспомогательного переноса. AF = 1 при возникновении переноса в младшей тетраде; - ZF – флаг нуля. ZF = 1, если в результате выполнения операции результат равен нулю; - SF – флаг знака. При выполнении арифметических операций в дополнительном коде знак хранится в старшем разряде. В SF копируется старший бит (7, 15 или 31); - OF – флаг переполнения. OF = 1 при сложении чисел с одинаковыми знаками (при вычитании – с разными), когда знак результата операции не совпадает со знаком любого из операндов; - IOPL – привилегии I/O. Значение двух битов устанавливается в соответствии с уровнем привилегий (0, 1, 2, 3) задачи, решаемой МП в Р-режиме; - NT – флажок вложенной задачи. NT = 1 в Р-режиме, при переходе к подпрограмме с помощью команды CALL. Используется командой IRET: если NT = 1, осуществляется переключение задачи; если NT = 0, возврат из аппаратного прерывания. Флаги управления используются для организации вычислительного процесса. Их назначение и наименование: - TF – режим покомандного выполнения (трассировки). При TF = 1 МП осуществляет пошаговое выполнение команд, иначе – обычный режим; - IF – прерывание. При IF = 1 допускаются внешние аппаратные прерывания по входу INTR. При IF = 0 МП игнорирует запросы INTR (прерывания запрещены или замаскированы), состояние IF игнорируется по входу NMI немаскируемых внешних и внутренних прерываний; - DF – направление. При DF = 1 обработка цепочек слева направо и автодекремент (на 1, 2 или 4) регистров (E)SI, (E)DI. При DF = 0 обработка цепочек справа налево и автоинкремент (на 1, 2 или 4) регистров (E)SI, (E)DI; - RF – возобновление. При RF = 1 можно маскировать особые случаи в режиме отладки программы; - VM – V-режим. При VM = 1 устанавливается V-режим (режим эмуляции МП 8086). При VM = 0 МП работает в R- или Р-режиме; - AC – контроль выравнивания. При AC = 1 и AM = 1 в CR0 допускается выравнивание нечетного ФА при обращении к памяти. Используется на уровне привилегий 3; - VIP, VIF – ожидание и прерывание. Флажки устанавливаются командами Pentium в V-режиме; - ID – идентификация. Определяет поддержку команды опроса модели МП CPUID. Системные регистры Системные регистры используются системными программистами для организации работы МП в Р- или V-режиме. Все системные регистры 32-разрядные, кроме LDTR и TR, и в i386, i486 и Pentium делятся на регистры Р-режима, управления, отладки и проверки. К регистрам Р-режима относятся регистры GDTR, IDTR, LDTR и TR, причем LDTR и TR используются как 16-разрядные селекторы. Регистры Р-режима предназначены для организации сегментной адресации и назначение их рассмотрено в гл.III п.6. Регистр задачи TR используется в многозадачном режиме. Он указывает на сегмент состояния задачи (TSS), в который сначала записывается значение всех пользовательских регистров и системных регистров CR3 и LDTR – контекст предыдущей (выходящей) задачи, а затем по новому значению TR из TSS извлекается контекст загружаемой в МП на выполнение задачи. К регистрам управления относятся регистры CR0, CR2, CR3 и в i486 зарезервированный CR1. В регистр CR0 в младшие 2 байта включено слово состояния машины (MSW), впервые появившееся в МП 286, в следующих МП расширенное дополнительными информационными битами. Структура CR0 показана на рис. 2.2. Назначение информационных битов CR0 следующее: - PE – реальная адресация. При PE = 0 МП работает в режиме реальной адресации. Устанавливается командой загрузки CR0; - MP – слежение за сопроцессором, при его отсутствии MP = 0; - EM – эмуляция сопроцессора, при EM = 1 генерируется ситуация 7 (сопроцессор отсутствует); - TS – задача переключена. TS = 1 при каждом переключении задач; - ET – тип сопроцессора. ET = 1 при наличии Intel 387 и ET = 0 при наличии Intel 287; - NE – ошибка сопроцессора. При NE = 1 сообщаются ошибки FPU и возможны прерывания; - WP – защита записи. При WP = 1 не допускается изменение области памяти пользователя супервизором; - AM – маска выравнивания. При AM = 0 контроль выравнивания запрещен; - NW – запрет сквозной записи. При NW = 0 сквозная запись и циклы недействительности разрешены; - CD – разрешение кэш. При CD = 0 внутренний кэш используется, иначе – нет; - PG – включение страничной адресации. При PG = 1 страничный механизм включен, иначе – выключен. При страничной адресации, когда бит CR0 (31) = 1, и наличии свопинга в CR2 заносится линейный адрес страницы, отсутствующей в ОЗУ.  Рис. 2.2. Формат регистров управления Регистр CR3 используется как базовый регистр каталога страниц в i386, i486 и Pentium. В младших разрядах имеет два информационных бита: - PWT – сквозная запись страниц. При PWT = 1 устанавливается способ сквозной записи, а при PWT = 0 – способ обратной записи; - PCD – запрет кэширования страниц. При PCD = 1 запрещена загрузка страниц в кэш. Регистр CR4 используется только в МП Pentium. Имеет следующие информационные биты: - VME – расширение V-режима. При VME = 1 поддерживаются флаги прерываний VIF и VIP; - PVI – виртуальное прерывание защищенного режима. При PVI = 1 позволяет выполнять программы уровня привилегий 0 на уровне привилегий 3; - TSD – разрешение маркера времени. При TSD = 1 допускается выполнение команды RDTSC; - DE – расширение отладки. При DE = 1 разрешаются точки останова по I/O; - PSE – расширение размера страниц. При PSE = 1 страницы имеют размер в 4 Мб; - MCE – контроль машины. При MCE = 1 допускается расширенный контроль. Регистры отладки К регистрам отладки МП i386, i486, Pentium относятся 8 регистров DR0DR7. Регистры DR4, DR5 в этих МП зарезервированы. В регистры DR0DR3 при отладке программ загружаются 4 линейных 32-разрядных адреса однобайтной команды INT 3 (код операции CCh) контрольных точек останова 0, 1, 2, 3. Эта команда временно программно заменяет первый байт кода операции команды, на котором необходимо остановить вычисления для контроля правильности выполнения участка программы. Каждая из контрольных точек описывается отдельно в DR7, а состояние отладки в DR6. Формат регистров DR6 и DR7 показан на рис. 2.3. Информационные разряды DR6 имеют следующее назначение: B0...B3 – фиксация контрольной точки. Bi=1 (i = 03) при совпадении соответствующего адреса в DR0 DR3 с адресом обрабатываемой команды в устройстве предвыборки команд; - BD – использование отладочных регистров. При BD = 1 следующая команда будет читать или записывать в один из отладочных регистров; - BS – пошаговый режим. BS = 1 при трассировке и TF = 1; - BT – многозадачный режим. BT = 1 при переключении задачи и T = 1 в TSS.  Рис.2.3. Формат регистров отладки DR6 и DR7 Регистр управления отладкой DR7 имеет следующие информационные биты: - Li/Gi – разрешение локальных и глобальных i-х контрольных точек. При Li = 1 разрешена установка контрольной точки задачи, а при Gi = 1, так же, как и при Li = 1, но для всех задач. При переключении задач Li очищаются; - LE, GE – контрольные точки данных. При LE = 1 и GE = 1 МП выдает сообщение после завершения соответствующей команды по обработке данных. При переключении задач LE очищается, GE – нет; - LENi – длина проверяемого интервала памяти для каждой контрольной точки (область остановки, внутри которой условия останова могут сработать). При 1) <00> – 1 байт; 2) <01> – 2 байта; 3) <10> – не определено; 4) <11> – 4 байта; - R/Wi – прерывание по типу доступа к памяти, возникает при 1) <00> – при выполнении команды; 2) <01> – при записи данных; 3) <10> – не определено; 4) <11> – при чтении/записи; - GD – защита отладчика. При GD = 1 устанавливается защита обращения к регистрам отладки. При вызове процедур отладки GD сбрасывается. Регистры отладки доступны только в R- и Р-режиме при уровне привилегий 0. Регистры проверки Регистры проверки TR3TR7 предназначены в i386, i486 для тестового контроля КЭШ и буфера TLB в устройстве страничного преобразования. Регистры TR3TR5 используются для проверки кэш-памяти i486 и имеют формат, показанный на рис. 2.4.  Рис. 2.4. Формат регистров проверки TR3 TR5 Регистр данных TR3 позволяет осуществить доступ к 128-разрядным буферам чтения и заполнения кэш. Загрузка TR3 в буфер или чтение двойного слова (ячейки) из буфера в TR3 осуществляется последовательно, и место чтения/записи в буфере определяется состоянием регистра TR5. Регистр TR4 определяет состояние тестирования кэш. Младшие биты TR4(2, 0) зарезервированы, старшие 21 бит TR4(31, 11) используются для хранения информации о значении тэга. Остальные разряды имеют следующие назначения: - Дос – биты достоверности, используются при операциях считывания для того множества, к которому производилось обращение; - LRU – содержит 3 бита LRU при поиске того множества, к которому производилось обращение; - V – бит верности, при считывании копирует соответствующий бит Дос, при записи становится новым битом достоверности для выбранных направления и множества. Регистр управления TR5 содержит 7-битное поле SET SEL выбора одной из 128 строк множества, а поле CTL предназначено для задания следующих функций: - < 00> – запись/считывание в буфер заполнения; - < 01> – запись в кэш; - <10> – считывание из кэш; - <11> – очистка кэш, фиксация всех строк недостоверности. Поле ENT регистра TR5 управляет выбором направления при записи/считывании в кэш или определяет ячейку при обращении к буферу заполнения в соответствии с хранимой в нем кодовой комбинацией. Регистры TR6, TR7 используются для тестирования буфера TLB в i386, i486, более подробно рассмотрены в гл.III. п.7. Регистры сопроцессора Сопроцессор – это специализированный математический процессор. Он предназначен для параллельного вычисления арифметических операций с плавающей точкой и разгрузки процессора. Сопроцессоры i87, i287, i387, i487SX устанавливались отдельно от МП на системной плате для параллельного вычисления специальных функций и длительных арифметических операций с плавающей точкой под управлением МП. В i486 и Pentium сопроцессор включен в структуру МП как устройство с плавающей точкой – FPU. В процессоре Pentium был полностью переконструирован FPU процессора Intel 486, он поддерживает оба стандарта для двоичной арифметики с плавающей точкой IEEE 754 и 854. Для общих команд, включая ADD, MUL и LOAD, были разработаны более быстрые алгоритмы, которые обеспечивают увеличение в скорости как минимум в 3 раза по сравнению с FPU процессора Intel 486. Большинство приложений могут достигнуть пятикратного увеличения в скорости по сравнению с FPU процессора Intel 486 или даже большей производительности при конвейерной обработке. В состав FPU входит УУ, операционный блок, 8 регистров стека R0 R7, регистры управления CW и состояния SW, регистр тэгов TW, указатель команды IP и указатель данных DP. Структура регистров показана на рис. 2.5.  Рис. 2.5. Регистры сопроцессора Восемь 80-битных регистров R0R7 предназначены для хранения чисел с плавающей точкой в расширенном вещественном формате. Состояние 3-битного поля TOP регистра SW указывает на вершину стека. Эта часть регистра SW выполняет функции реверсивного двоичного счетчика, который при декременте из состояния <000> устанавливается в состояние <111>. При инкременте состояния <111> правый разряд увеличивается на единицу, и устанавливается 3-разрядный код, равный значению поля TOP – <000>. Тем самым вершина стека изменяет свое значение при инкременте циклически. Если, например, в поле TOP содержится код <100>, то за вершину стека ST (0) или ST принят регистр R4, а низ стека ST (7) будет в R3. При записи в стек R0R7 осуществляется декремент поля TOP и передача операнда в низ стека. Так, при ST = <100> после записи получим ST = <011> и передачу операнда в R3. При чтении из стека осуществляется чтение по адресу ST (0), затем инкремент поля TOP. В результате обращение к стеку автоматически изменяет значение указателя стека, который является единственным источником для определения адреса регистра стека. В поле M регистров R0R7 заносится мантисса, знак которой располагается в 79 разряде. В поле Е располагается смещенный порядок числа. Мантисса числа – правильная дробь, нормализована как 1/2 |М| < 1, сдвинута в ОЗУ влево на один разряд и хранится без старшей единицы. При приеме операнда в сопроцессор она сдвигается на один разряд вправо так, что старшая цифра 1 с весом 2-1 восстанавливается, размещаясь в 63-м бите разрядной сетки. Для определения состояния стека предназначен регистр тэгов TW, в котором 2-битные поля TAG (i), где i = 0,1,...,7, определяют соответственно состояния регистров R0R7 Состояние TAG(i) используется для упрощения контроля и правильного обращения к стеку. Так, TAG (3) определяет состояние R3. Поля TAG (i) интерпретируются следующим образом: - 00 – допустимое ненулевое число; - 01 – нуль; - 10 – специальное число (не число, неподдерживаемый формат, бесконечность или денормализованное число); - 11 – отсутствие данных. Разряды регистра управления CW имеют следующее наименование и назначение: - IC (только в i87, i287) – управление бесконечностью. При IC = 0 опускается знак в выражении , а при IC = 1 – аффинная арифметика, знак присутствует в наличии - и + ; - RC – округление, 2-битное состояние определяет один из способов округления результата в четырех арифметических операциях; - PC – точность, применяется совместно с полем RC для изменения точности вычислений; - IEM (i87) маскирует флаг запроса прерывания IR. При IEM = 1 запрещает генерацию сигнала прерываний при ошибках сопроцессора; - PM, UM, OM, ZM, DM, IM – маски исключений. Биты, исключающие прерывания на соответствующие ошибки FPU. Регистр состояния SW имеет в своем составе следующие информационные разряды: - B (i87, i287) – занятость. B=1 при обработке команд и прерываниях. В = 0, когда сопроцессор свободен; - TOP – указатель стека; - C0 C3 – флаги арифметических операций; по аналогии с EFLAGS, С0 = CF, C2 = PF, C3 = ZF. Флаг С1 используется в некоторых командах FPU для определения ошибок. Так, при переполнении С1=0, при антипереполне-нии С1 = 1; - ES (IR для i87) – суммарная ошибка. ES = 1 при возникновении ошибок FPU. В 8087 IR = 1 характеризует незамаскированную исключительную ситуацию; - SF (i387, i487, Pentium) – стековая ошибка. При выходе за пределы стека SF = 1, IE = 1, причем при выходе за верхнюю границу С1 = 1, а за нижнюю - С1 = 0; - PE, UE, OE, ZE, DE, IE – флаги исключительных ситуаций: - PE – неточный результат; - UE – антипереполнение; - OE – переполнение; - ZE – деление на ноль; - DE – денормализованный операнд; - IE – недействительная операция. Эти флаги устанавливаются операционным блоком FPU при вычислениях в случае возникновения соответствующей особой ситуации, и при отсутствии маски (PM, UM, OM, ZM, DM, IM) в регистре управления CW. Содержимое указателя и селектора команд IP и указателя и селектора данных DP используется процедурами обработки особых случаев. В регистр IP сопроцессора МП передает адрес обрабатываемой числовой команды и 11 бит кода операции, а в DP – адрес её операнда. Регистры SIMD В потоковом расширении SIMD используются восемь 128-разрядных регистров общего назначения с прямой адресацией. SIMD-регистры содержат упакованные 128-разрядные данные. Команды SSE обращаются к SIMD-регистрам используя регистровые имена XMM0 и до XMM7 (рис. 2.6). SIMD-регистры могут быть использованы для вычислений над данными; но не могут быть использованы для адресации памяти. Адресация выполняется с помощью определенных в IA режимов адресации и регистров общего назначения (EAX, EBX, ECX, EDX, EBP, ESI, EDI и ESP). MMX регистры MMX0(63,0)- MMX7(63,0) физически реализованы на стандартных для архитектуры Intel 80-разрядных регистрах данных с плавающей точкой (см. рис. 2.5). Поэтому переход от операций MMX к операциям с плавающей точкой требует запуска команды emms. Но так как SIMD-регистры с плавающей точкой являются отдельным регистровым файлом, то команды MMX и команды с плавающей точкой могут быть смешаны с командами SSE без выполнение специальных инструкций, таких какemms. Новый регистр контроля/состояния MXCSR используется для маскирования и демаскирования обработки числовых исключительных ситуаций, для определения режима округления, для установки режима сброса в ноль и для просмотра состояния флагов.

| ||||||||||||||||||||||||