Лачин Электроника. Электроника рекомендовано Министерством образования Российской Федерации в качестве учебного пособия ля студентов высших технических учебных заведений РостовнаДону Феникс 2001 Рецензенты

Скачать 7.57 Mb. Скачать 7.57 Mb.

|

|

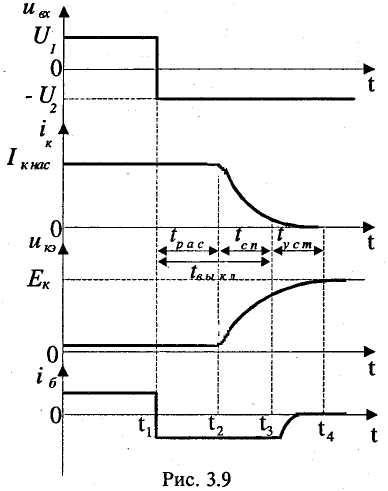

1б.нас.мин. Через 1к.порогобозначен ток коллектора, соответствующий напряжению ибэ.порог. Интервал t1...t2называют интервалом задержки включения, интервал t2....t3— интервалом формирования фронта, а интервал t3...t4— интервалом накопления заряда. Разность t3—t1называют временем включения. Длительность интервала формирования фронта определяется током базы, током насыщения коллектора 1к.нас, величиной b транзистора, а также временем жизни неосновных носителей в базе. На интервале задержки включения изменяются напряжения на эмиттерном и коллекторном переходах, и поэтому изменяются объемные нескомпенсированные заряды в области этих переходов. Это находит отражение в том, что возникают токи электродов транзистора. Но ток коллектора на рассматриваемом интервале мал. Указанное явление изменения зарядов условно называют перезарядом барьерных емкостей эмиттерного и коллекторного переходов. Однако не следует забывать, что барьерные емкости, как и диффузионные, являются по определению дифференциальными емкостями. Поэтому к термину «перезаряд» следует относиться с осторожностью. Например, если напряжение между базой и эмиттером равно нулю, это Не означает, что некомпенсированный заряд в области эмиттерного перехода равен нулю (а заряд «обычной» емкости равен нулю при нулевом напряжении). К концу интервала задержки напряжение между базой и эмиттером увеличивается до значения ибэ.парог. На интервале формирования фронта токи электродов транзистора являются значительными. В начале этого интервала продолжается изменение напряжения на эмиттер-ном переходе. В течение всего интервала изменяется напряжение на коллекторном переходе. Это вызывает изменение соответствующих нескомпенсированных объемных зарядов. На интервале формирования фронта, кроме этого, происходит накопление неравновесных носителей электричества в базе транзистора. Это условно называют процессом накопления неосновных носителей. Но следует учитывать, что заряд неосновных носителей практически мгновенно компенсируется зарядом основных носителей. Подробнее этот вопрос рассмотрен при изучении полупроводникового диода и явления диэлектрической релаксации (релаксации Максвелла). Чем больше коэффициент насыщения, тем меньше длительность фронта tф. На интервале накопления заряда продолжается накопление неравновесных носителей электричества. При этом напряжение икэнезначительно уменьшается, а ток коллектора незначительно увеличивается. Изобразим временные диаграммы, иллюстрирующие процесс выключения (рис. 3.9). На рис. 3.9 введены следующие обозначения интервалов времени:

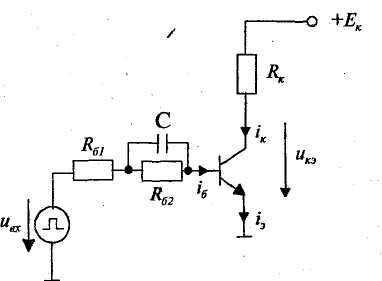

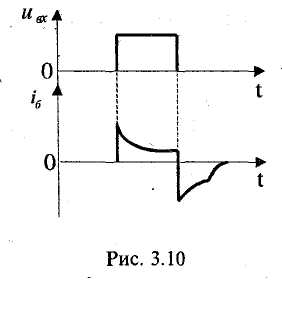

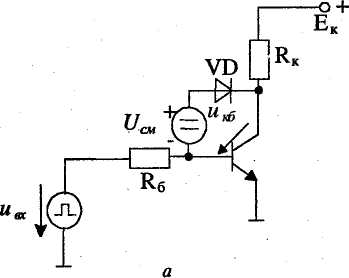

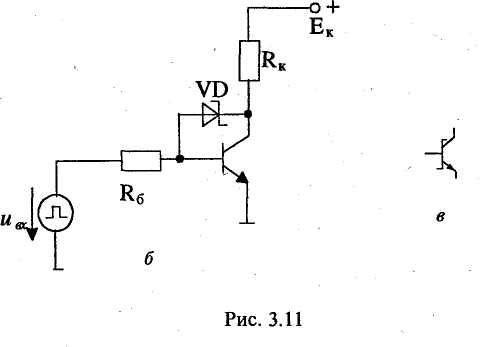

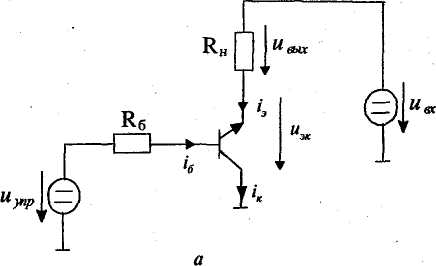

Разность t3 — t1называют временем выключения. На интервале рассасывания ток базы отрицательный и ограничивается резистором Rб. .Если пренебречь напряжением и6э, то  i6=-U2/Rб . На этом интервале происходит уменьшение концентрации неравновесных носителей электричества, и к концу интервала транзистор выходит из режима насыщения. Чем больше коэффициент насыщения, тем больше время рассасывания tpac. Чем больше по модулю ток i6, тем меньше время рассасывания. i6=-U2/Rб . На этом интервале происходит уменьшение концентрации неравновесных носителей электричества, и к концу интервала транзистор выходит из режима насыщения. Чем больше коэффициент насыщения, тем больше время рассасывания tpac. Чем больше по модулю ток i6, тем меньше время рассасывания.На интервале форсирования спада продолжается уменьшение концентрации неравновесных носителей, ток iкзначительно уменьшается, а напряжение на коллекторном переходе и напряжение икэзначительно возрастает. Изменение напряжения на коллекторном переходе приводит к изменению объемных нескомпенсированых зарядов в области этого перехода (говорят, что барьерная коллекторная емкость перезаряжается). На интервале установления напряжение ибэизменяется от величины ибэ.порогдо —U2. При этом изменяются не-скомпенсированные объемные заряды переходов транзистора. После момента времени t3ток коллектора становится равным току базы, эмиттерный переход смещается в обратном направлении, ток базы быстро уменьшается по модулю и становится нулевым. Количественный анализ динамических режимов транзисторных ключей настоятельно рекомендуется выполнить с помощью пакетов программ для машинного анализа электронных схем (Micro-Cap V и др.). Эти пакеты программ позволяют анализировать переходные процессы при самых сложных входных сигналах. Ранее для расчета переходных процессов в транзисторных ключах применялись упрощенные методики, предполагающие к тому же использование простых входных сигналов. В настоящее время эти методики рекомендуются применять только в учебных целях.   Из изложенного следует, что время включения ключа можно уменьшить, увеличивая отпирающий ток базы. В то же время увеличивать коэффициент насыщения нежелательно, так как это удлиняет время выключения. Аналогично время выключения можно уменьшить, увеличивая запирающий (отрицательный) ток базы. Представим схему транзисторного ключа с форсирующим конденсатором, который увеличивает положительную и отрицательную амплитуды тока базы и тем самым повышает быстродействие (рис. 3.10). Работу ключа поясняют временные диаграммы. Подобные схемы широко используются на практике. 3.2.2. Ненасыщенные ключи на биполярных транзисторах Одним из способов повышения быстродействия является предотвращение насыщения транзистора. Это, как отмечалось выше, уменьшает время рассасывания. Важно учитывать, что предотвращение насыщения обычно достигается не уменьшением отпирающего базового тока, так как этот способ предотвращения насыщения имеет существенные недостатки. Во-первых, если ориентироваться на уменьшение тока базы, то придется принять меры по точной регулировке этого тока. Иначе ключ на одном экземпляре транзистора, имеющего малый коэффициент р, не будет полностью открываться, а ключ на другом экземпляре транзистора, имеющего большой коэффициент р, все-таки будет входить в режим насыщения. Во-вторых, работа ключа может оказаться нестабильной. Например, существенное дестабилизирующее воздействие может оказать температура. В-третьих, длительность фронта импульса будет значительной. Вначале рассмотрим идеализированную схему ненасыщенного ключа (рис. 3.11, а), принцип действия которого легко понять. Напряжение смещения Uсмдолжно быть порядка 0,4...0,6 В. До тех пор, пока режим работы транзистора не приближается к режиму насыщения, диод VD остается закрытым и весь ток источника входного сигнала поступает в базу транзистора, вызывая его быстрое отпирание. На границе активного режима и режима насыщения напряжение икбоказывается близким к нулевому, и   диод начинает открываться. После этого часть тока источника входного сигнала ответвляется в цепь диода, ток базы уменьшается, и транзистор не входит в режим насыщения. Таким образом, в схеме имеет место нелинейная отрицательная обратная связь по напряжению. В таких схемах должны использоваться высокочастотные диоды. Очень хорошие результаты дает использование диодов Шоттки (рис. 3.11, б). При рассмотрении этих диодов отмечалось, что они отличаются большим быстродействием и малым падением напряжения (время восстановления может быть порядка 0,1 нс и меньше, напряжение отпирания около 0,25 В). При использовании диодов Шоттки источники напряжения смещения не требуются. Биполярный транзистор с диодом Шоттки стали называть «транзистор Шоттки» и обозначать, как показано на рис. 3.11, в. Кроме достоинств, следует иметь в виду и следующие недостатки ненасыщенных ключей:

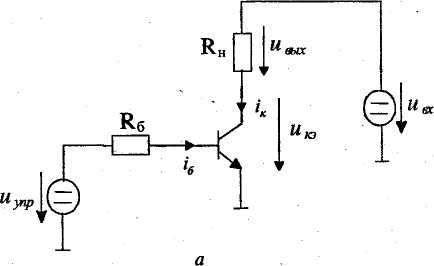

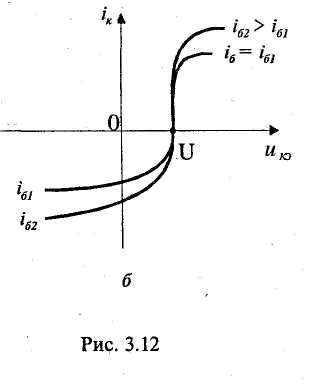

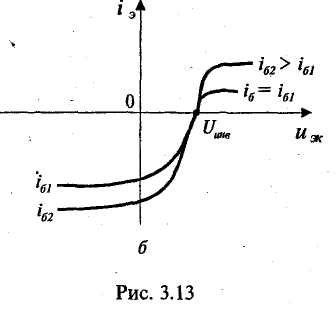

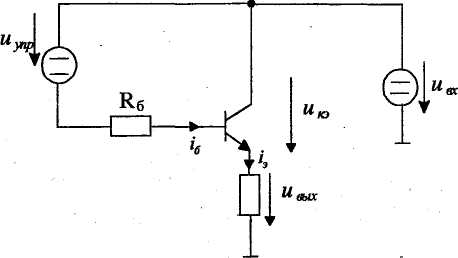

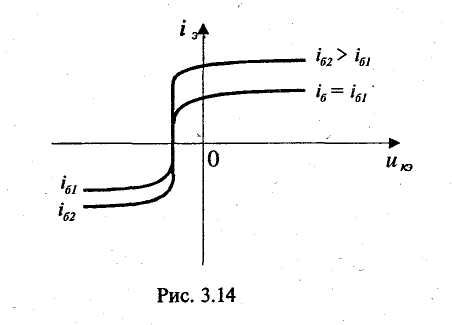

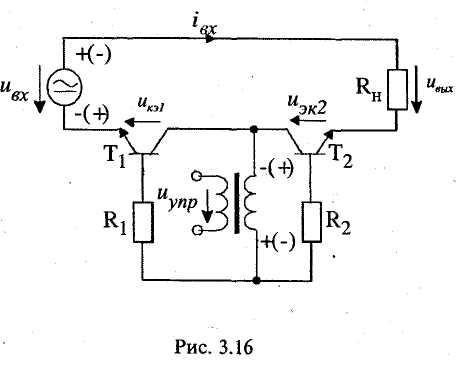

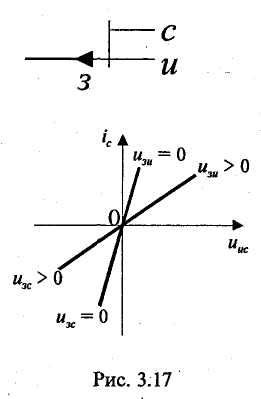

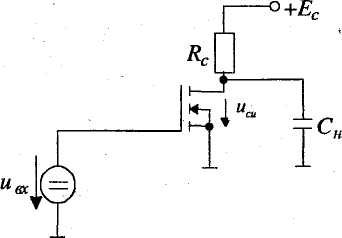

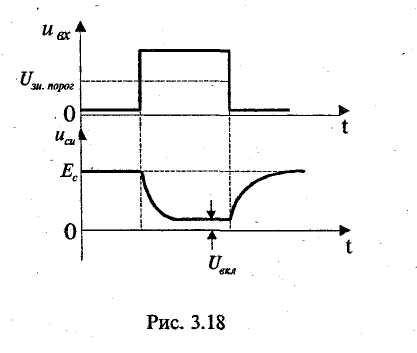

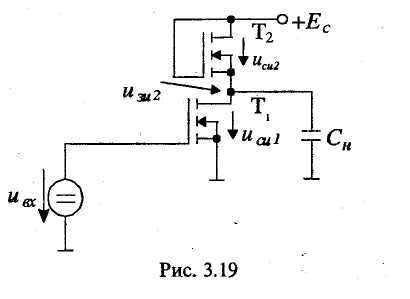

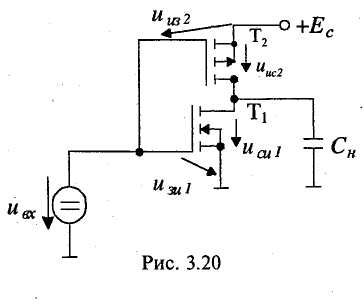

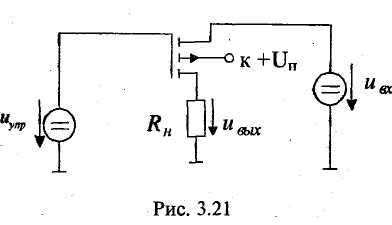

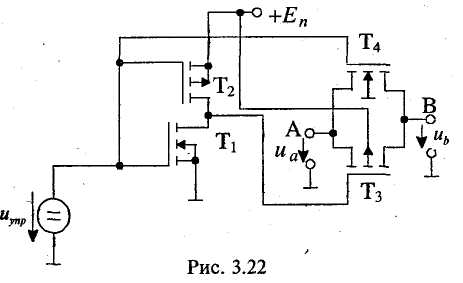

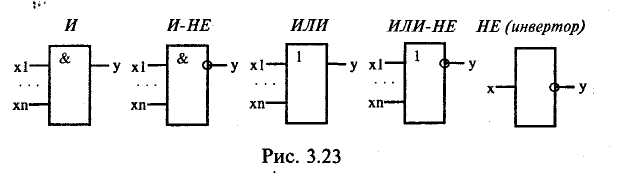

3.2.3. Аналоговые коммутаторы (аналоговые ключи) на биполярных транзисторах Выше рассмотрены ключи, в выходных цепях которых используются источники постоянного напряжения (источники питания). Назначение таких ключей состоит в том, чтобы создать на выходе или напряжение, близкое к нулю (когда ключ открыт), или напряжение, близкое к напряжению питания (когда ключ закрыт, а ток, потребляемый нагрузкой, подсоединенной к ключу, достаточно мал). Такая работа характерна для ключей цифровой электроники (их называют цифровыми ключами) и силовой электроники. В информативной электронике используются также и ключи, имеющие другое назначение. Оно состоит в том, чтобы соединять или рассоединять источник входного, содержащего информацию аналогового сигнала и приемник этого сигнала. Такие ключи принято называть аналоговыми. Их также называют аналоговыми коммутаторами.   Рассмотрим простейшие схемы аналоговых ключей на биполярных транзисторах. На рис. 3.12, а представлена схема с общим эмиттером. Изобразим выходные характеристики транзистора для прямого и инверсного включения в области, близкой к началу координат (рис. 3.12, б). Через ивхобозначено входное напряжение, которое в зависимости от управляющего сигнала иупрподается или не подается на нагрузку RH. Напряжение ивх может быть как положительным, так и отрицательным. Если иех > 0, то рассматриваемый аналоговый ключ работает так же, как изученный ключ с постоянным напряжением питания. Если ивх < 0, транзистор работает в инверсном режиме. Одним из недостатков биполярного транзистора с точки зрения применения его в аналоговых ключах является то, что выходные характеристики не проходят через начало координат. Вследствие этого ток iки напряжение ивых будут равны нулю не тогда, когда ивх = 0, а при некотором положительном входном напряжении U. Напряжение Uобычно составляет 10... 100 мВ. Это напряжение называют остаточным или напряжением смещения. На практике для уменьшения величины Uтранзистор включают так, чтобы роль эмиттера играл коллектор, а роль коллектора — эмиттер. Изобразим соответствующие характеристики и схему, которую иногда назьгеают схемой с общим эмиттером при инверсном включении транзистора (рис. 3.13). И   з-за несимметрии структуры транзистора, различия в концентрациях примесей в различных его областях остаточное напряжение для инверсного включения Uинвобычно значительно меньше напряжения U. Часто Uинвсоставляет 1...5мВ. Но, используя инверсное включение, следует помнить, что максимально допустимое запирающее напряжение эмиттерного перехода обычно значительно меньше соответствующего напряжения для коллекторного перехода. з-за несимметрии структуры транзистора, различия в концентрациях примесей в различных его областях остаточное напряжение для инверсного включения Uинвобычно значительно меньше напряжения U. Часто Uинвсоставляет 1...5мВ. Но, используя инверсное включение, следует помнить, что максимально допустимое запирающее напряжение эмиттерного перехода обычно значительно меньше соответствующего напряжения для коллекторного перехода.Обратимся к третьей простейшей схеме — схеме с общим коллектором (рис. 3.14). Можно заметить, что последняя схема фактически повторяет предыдущую, отличаясь только условно-положительными направлениями токов и напряжений. Подобным образом соотносятся и характеристики.    Рассмотрим компенсационный аналоговый ключ на биполярных транзисторах. С целью уменьшения напряжения на открытом ключе используют последовательное включение одинаковых транзисторов. Промышленность выпускает интегральные схемы, содержащие пары транзисторов, Рассмотрим компенсационный аналоговый ключ на биполярных транзисторах. С целью уменьшения напряжения на открытом ключе используют последовательное включение одинаковых транзисторов. Промышленность выпускает интегральные схемы, содержащие пары транзисторов,предназначенные для такого использования. Изобразим принципиальную схему интегральной микросхемы 101КТ1А (рис. 3.15). Такие устройства называют также прерывателями. Изобразим схему аналогового ключа на основе такой микросхемы (рис. 3.16). Входной сигнал иехможет быть постоянным любой полярности или переменным. Управляющий сигнал передается через трансформатор. Пусть в некоторый момент времени имеют место те полярности входного напряжения и напряжения на вторичной обмотке трансформатора, которые указаны без скобок, тогда транзисторы будет открыты и входной ток iexбудет положительным. Транзистор Т1 будет работать в нормальном режиме, причем он включен по схеме с общим коллектором. В соответствии с приведенными выше характеристиками в режиме насыщения икэ1 < 0. Транзистор Т2будет работать в инверсном режиме. В соответствии с приведенными выше характеристиками для схемы с общим эмиттером при инверсном включении иэк2> 0. Таким образом, остаточные напряжения на транзисторах будут взаимно компенсироваться. Поэтому такие аналоговые  ключи называют компенсированными. Благодаря этому общее напряжение на транзисторах оказывается очень малым. Для указанной микросхемы это напряжение не более 100 мкВ. Для уяснения особенностей работы схемы полезно учитывать сделанное выше замечание о том, что используемые в рассматриваемом ключе простейшие схемы фактически совпадают. В случае такой полярности напряжения на вторичной обмотке трансформатора, которая указана в скобках, ключ будет закрыт. Для данной микросхемы ток утечки не более 40 нА. Максимальный ток открытого ключа — 10 мА. Компенсированные транзисторные ключи входят в состав различных микросхем серий 124, 129, 162. 3.2.4. Ключи на полевых транзисторах Ключи на полевых транзисторах широко используются для коммутации аналоговых и цифровых сигналов. В аналоговых ключах обычно используют транзисторы с управляющим p-n-переходом или МДП-транзисторы с индуцированным каналом. В цифровых ключах обычно используют МДП-транзисторы с индуцированным каналом. В последнее время полевые транзисторы все чаще используют в силовой импульсной электронике. Ключи на полевых транзисторах отличаются малым остаточным напряжением. Они могут коммутировать слабые сигналы (в единицы микровольт и меньше). Это следствие того, что выходные характеристики полевых транзисторов проходят через начало координат. Для примера изобразим выходные характеристики транзистора с управляющим переходом и каналом р-типа в области, прилегающей к началу координат (рис. 3.17). Обратим внимание, что характеристики в третьем квадранте  соответствуют заданным напряжениям между затвором и стоком. Однако минимальное сопротивление включенного ключа на полевом транзисторе может быть больше, чем ключа на биполярном транзисторе (т. е. наклон самой круто поднимающейся характеристики полевого транзистора может быть меньше, чем наклон соответствующей характеристики на биполярном транзисторе). Поэтому при значительном токе падение напряжения на полевом транзисторе может быть больше, чем падение напряжения на биполярном транзисторе. Иногда остаточным напряжением на ключе называют не то напряжение, которое соответствует нулевому току, а то, которое соответствует некоторому значительному току ключа. Это нужно иметь в виду, чтобы понять смысл на первый взгляд парадоксального утверждения, встречающегося у некоторых авторов и состоящего в том, что остаточное напряжение ключей на полевых транзисторах больше, чем ключей на биполярных транзисторах, и поэтому «полевой транзистор обладает худшими ключевыми свойствами по сравнению с биполярным». Кстати будет сказать, что наличие подобных на первый взгляд противоречивых утверждений полезно воспринимать как знак того, что выбор конкретного решения (в данном случае выбор для коммутации полевого или биполярного транзистора) следует осуществлять на основе всестороннего анализа. В статическом состоянии ключ на полевом транзисторе потребляет очень малый ток управления. Однако этот ток увеличивается при увеличении частоты переключения. Очень большое входное сопротивление ключей на полевых транзисторах фактически обеспечивает гальваническую развязку входных и выходных цепей. Это позволяет обойтись без трансформаторов в цепях управления. Ключи на полевых транзисторах часто менее быстродействующие в сравнении с ключами на биполярных транзисторах. Изобразим схему цифрового ключа на МДП-транзис-торе с индуцированным каналом n-типа и резистивной нагрузкой и соответствующие временные диаграммы (рис. 3.18). На схеме изображена емкость нагрузки Сн, моделирующая емкость устройств, подключенных к транзисторному ключу. Очевидно, что при нулевом входном сигнале транзистор заперт и исн= Eс. Если напряжение ивх больше порогового напряжения Uзи.порогтранзистора, то он открывается и напряжение исиуменьшается. Ключи на полевых транзисторах с управляющим р-п-переходом входят в состав различных микросхем серий 284, 504 и др.. Напряжение на ключе в его включенном состоянии Uвкл зависит от сопротивления стока Rc, величины входного сигнала и особенностей стоковых характеристик транзистора. Скорость изменения напряжения на выходе определяется сопротивлением Rc, емкостью Сни частотными свойствами транзистора.   Изобразим схему цифрового ключа на МДП-транзисторе с нагрузочным МДП-транзистором (с динамической нагрузкой) (рис. 3.19). Отметим, что при использовании интегральной технологии такой ключ, как ни странно на первый взгляд, изготовить проще в сравнении с рассмотренным выше, имеющим нагрузочный резистор. Транзистор Т1называют активным, а транзистор Т2— нагрузочным. В  начале рассмотрим закрытое состояние ключа. При этом ивх< Uзи.nopoгl ,где Uзи.nopoгl— пороговое напряжение для транзистора T1. начале рассмотрим закрытое состояние ключа. При этом ивх< Uзи.nopoгl ,где Uзи.nopoгl— пороговое напряжение для транзистора T1.В этом случае транзистор Т1закрыт и через оба транзистора протекает очень малый ток (обычно не более 1 нА). При этом напряжение иси1близко к напряжению Ес, а напряжение иси1близко к нулю. В рассматриваемом состоянии транзистор Т2также закрыт, хотя напряжение между затвором и истоком этого транзистора положительно (очевидно, что изи2= иси2). Но соотношение между параметрами транзисторов обеспечивается именно такое, чтобы в закрытом состоянии ключа выполнялось соотношение иси1= Ес. По крайней мере очевидно, что напряжение иси2не может быть больше порогового напряжения Uзu.nopoe2для транзистора Т2, иначе бы транзистор Т2открылся и напряжение на нем уменьшилось. Теперь рассмотрим открытое состояние ключа. При этом ивх>изи.пврог1. Транзистор Т1открыт и напряжение иси1 близко к нулю, а напряжение на транзисторе Т2близко к напряжению питания. В рассматриваемом состоянии транзистор Т2также открыт, при этом изи2 = иси2= Ес. Но транзисторы конструируют таким образом, чтобы удельная крутизна транзистора Т2была намного меньше, чем удельная крутизна транзистора T1 .Именно поэтому в открытом состоянии ключа иси1 = 0 (часто это напряжение лежит в пределах 50...100 мВ). Так как удельная крутизна транзистора Т2мала, ток, протекающий через открытый ключ, сравнительно мал. Изобразим схему цифрового ключа на комплементарных МДП-транзисторах (комплементарный МДП-ключ, КМОП-ключ) (рис. 3.20). Здесь использованы взаимодополняющие друг друга (комплементарные) транзисторы: транзистор Т, с каналом n-типа и транзистор Т2с каналом p-типа. Обозначим через Uзи.порог1и Uзи.порог2пороговые напряжения для транзисторов соответственно Т1и Т2. Стоит обратить внимание, что каждое из указанных пороговых напряжений является положительным. Пусть ивх= 0, тогда, очевидно, транзистор T1закрыт, а транзистор Т2открыт. При этом исн1 = Ес, иис2 = 0. Если иех > Uзи.порог1l, тогда транзистор Т1открыт. Пусть, кроме того, ивх>Ес— Uзи.порог2, тогда транзистор Т2закрыт. При этом иси1 =0, иис2=Ес. Надо отметить, что если Ес < Uзи.порог1 + Uзи.порог2, то при изменении входного сигнала не возникает ситуация, когда оба транзистора включены. Но если данное неравенство не выполняется, то такая ситуация будет иметь место при некотором промежуточном напряжении иех, и тогда через транзисторы протекает так называемый сквозной ток. Если длительность переднего фронта и длительность среза (заднего фронта) входного импульса мала, то сквозной ток  протекает короткое время, но и в этом случае он оказывает негативное влияние на работу схемы. Как следует из изложенного, в каждом из двух установившихся режимов, т. е. и в открытом, и в закрытом состоянии, ключ практически не потребляет ток от источника питания. Это первое важное достоинство комплементарного ключа. Вторым важным достоинством комплементарного ключа является резкое отличие выходного напряжения в открытом состоянии ключа (единицы микровольт и менее) и выходного напряжения в закрытом состоянии (это напряжение меньше напряжения питания всего лишь на единицы микровольт и менее). Это обеспечивает высокую помехоустойчивость цифровых схем на комплементарных ключах. Третьим важным достоинством комплементарного ключа является его повышенное быстродействие. Оно может быть на порядок больше, чем у двух других ранее изученных ключей на полевых транзисторах. Повышенное быстродействие объясняется тем, что как разряд емкости Сн, так и ее заряд происходит через соответствующий открытый транзистор (емкость разряжается через транзистор T1и заряжается через транзистор Т2). При этом в начале заряда или разряда через соответствующий транзистор протекает большой ток, который быстро изменяет напряжение емкости. Естественно предположить, что входной сигнал поступает от такого же ключа, т. е. или ивх=0, или ивх= Ес. В этом случае, чем больше напряжение питания Ес, тем больше отпирающий сигнал на соответствующем транзисторе и тем больше его начальный ток (к примеру, при ивх=0, ииз2= Ес). Поэтому при увеличении напряжения питания быстродействие комплементарного ключа увеличивается. Описанные достоинства, а также отработанность технологии изготовления явились причиной широкого использования КМОП-ключей. Рассмотрим простейшую схему аналогового ключа на МДП-транзисторе (рис. 3.21). Эта схема получается из предыдущей при замене транзистора Т1резистором нагрузки, а источника питания — источником входного сигнала.  Подложка транзистора подключена к положительному полюсу источника питания, т. е. к точке с наибольшим потенциалом, для того чтобы p-n-переходы между подложкой и истоком и подложкой и стоком не открывались. Транзистор этого аналогового ключа работает подобно тому, как работает транзистор Т2рассмотренного комплементарного ключа. Например, для отпирания транзистора необходимо, чтобы напряжение иупр было малым. Ключ может коммутировать как положительное, так и отрицательное входное напряжение. Р  ассмотрим теперь двунаправленный аналоговый ключ (передающий вентиль) на комплементарных транзисторах (рис. 3.22). Ключ предназначен для передачи напряжения иас вывода А на вывод В или напряжение иьс вывода В на вывод А. Предполагается, что эти напряжения находятся в пределах от 0 до +Еп. Транзисторы Т1 и Т2образуют рассмотренный выше комплементарный ключ. Двунаправленный ключ открыт, когда иупр= +Еn. В этом случае по крайней мере один из транзисторов Т3 и Т4открыт. Ключ закрыт, когда иупр= 0. ассмотрим теперь двунаправленный аналоговый ключ (передающий вентиль) на комплементарных транзисторах (рис. 3.22). Ключ предназначен для передачи напряжения иас вывода А на вывод В или напряжение иьс вывода В на вывод А. Предполагается, что эти напряжения находятся в пределах от 0 до +Еп. Транзисторы Т1 и Т2образуют рассмотренный выше комплементарный ключ. Двунаправленный ключ открыт, когда иупр= +Еn. В этом случае по крайней мере один из транзисторов Т3 и Т4открыт. Ключ закрыт, когда иупр= 0.Если схему изменить и на затворы транзисторов Т3и Т4 подавать не только положительные, но и отрицательные напряжения, то ключ будет в состоянии работать не только при положительных, но и отрицательных напряжениях иаи иb . Ключи на полевых транзисторах с изолированным затвором входят в состав микросхем серий 168, 547 и др., а на комплементарных транзисторах — в состав микросхем серий 590, 591, 176, 561, 1564. 3.3. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ Логический элемент (логический вентиль) — это электронная схема, выполняющая некоторую простейшую логическую операцию. На рис. 3.23 приведены примеры условных графических обозначений некоторых логических элементов. Логический элемент может быть реализован в виде отдельной интегральной схемы. Часто интегральная схема содержит несколько логических элементов.  Логические элементы используются в устройствах цифровой электроники (логических устройствах) для выполнения простого преобразования логических сигналов. 3.3.1. Классификация и основные параметры Рассмотрим наиболее широко используемую исторически сложившуюся классификацию. Она построена и с учетом того, какие электронные приборы являются основными в соответствующих интегральных схемах, и с учетом особенностей использованных схемотехнических решений. Выделяются следующие классы логических элементов (так называемые логики):

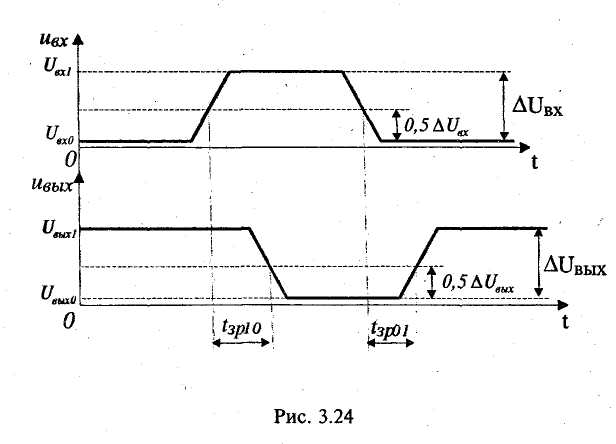

В настоящее время наиболее широко используются следующие логики: ТТЛ, ТТЛШ, КМОП, ЭСЛ. Устарела и практически не используется РТЛ. Для разрабатываемых в настоящее время устройств можно рекомендовать использовать КМОП-логику, а также логику на основе GaAs. Логические элементы и другие цифровые электронные устройства выпускаются в составе серий микросхем. Серия микросхем — это совокупность микросхем, характеризуемых общими технологическими и схемотехническими решениями, а также уровнями электрических сигналов и напряжения питания. Приведенная классификация охватывает не только собственно логические элементы, но и другие цифровые устройства, в том числе микропроцессорные. Однако здесь следует учитывать, что при производстве сложных цифровых устройств некоторые логики не использовались и не используются. Приведем примеры серии микросхем: ТТЛ — К155, КМ155, К133, КМ133; ТТЛШ - 530, КР531, КМ531, КР1531, 533, К555, КМ555, 1533, КР1533; ЭСЛ - 100, К500, К1500; КМОП - 564, К561, 1564, КР1554; GaAs -К6500; Каждая серия микросхем, несмотря на то, что она обычно содержит самые разнообразные цифровые устройства, характеризуется некоторым набором параметров, дающих достаточно подробное представление об этой серии. При определении этих параметров ориентируются именно на логические элементы — простейшие устройства серии микросхем. В соответствии с этим говорят о параметрах не серии микросхем, а о параметрах логических элементов данной серии. Рассмотрим наиболее важные из параметров. Быстродействие характеризуют временем задержки распространения сигнала tзри максимальной рабочей частотой Fмaкс. Обратимся к идеализированным временным диаграммам, соответствующим элементу НЕ (инвертору) (рис. 3.24). Через Uвхlи Uвыxlобозначены уровни входного и выходного напряжений, соответствующие логической единице, а через Uвх0 и Uвыx0— соответствующие логическому нулю. Различают время задержки tзр10 распространения при переключении из состояния 1 в состояние 0 и при переключении из состояния 0 в состояние 1 — tзр01 ,а также среднее время задержки распространения tзр ,причем tзр=0,5(tзр10+tзр01). Время задержки принято определять по перепадам уровней 0,5ΔUвхи 0,5ΔUвыx. Максимальная рабочая частота Fмaкс — это частота, при которой сохраняется работоспособность схемы. Нагрузочная способность характеризуется коэффициентом объединения по входу Коб и коэффициентом разветвления по выходу Kраз (иногда используют термин «ко-  эффициент объединения по выходу»). Величина Ко6 — это число логических входов, величина Краз — максимальное число однотипных логических элементов, которые могут быть подключены к выходу данного логического элемента. Типичные значения их таковы: Ко6 = 2...8, Краз = 4...10. Для элементов с повышенной нагрузочной способностью Краз = 20...30. Помехоустойчивость в статическом режиме характеризуют напряжением Uпст, которое называют статической помехоустойчивостью. Это такое максимально допустимое напряжение статической помехи на входе, при котором еще не происходит изменение выходных уровней логического элемента. Важным параметром является мощность, потребляемая микросхемой от источника питания. Если эта мощность различна для двух логических состояний, то часто указывают среднюю потребляемую мощность для этих состояний. Важными являются также следующие параметры:

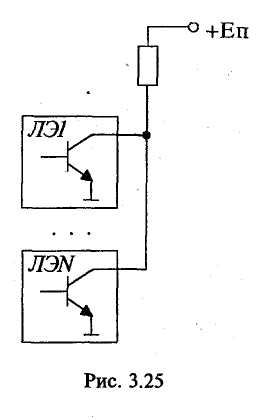

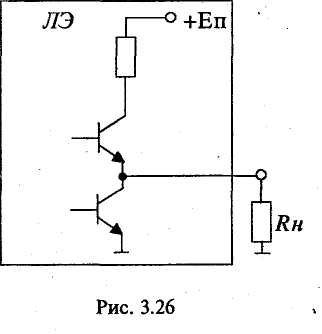

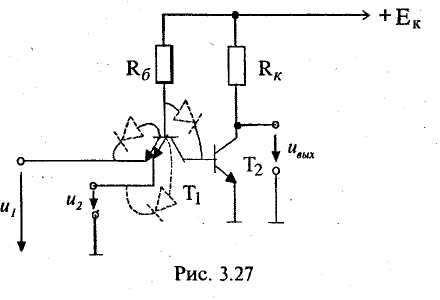

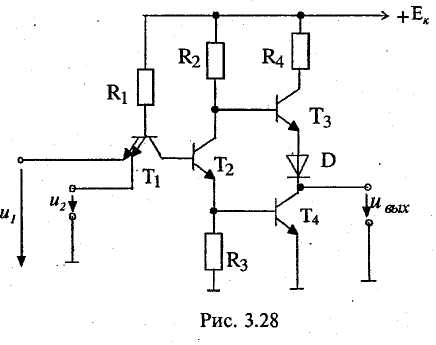

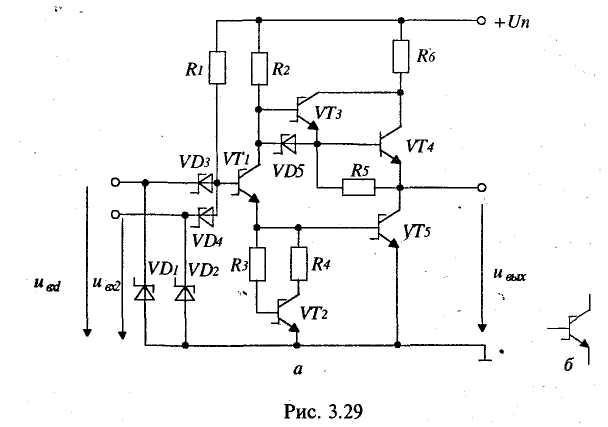

Используют и другие параметры. 3.3.2. Особенности выходных каскадов цифровых микросхем Ч  асто возникает необходимость подключения выходов нескольких цифровых микросхем к одной нагрузке. Одним из способов объединения выходов является использование в выходных каскадах микросхем транзисторов, один из выводов которых (коллектор, эмиттер, сток, исток) никуда не подключен. Такой вывод называют открытым. асто возникает необходимость подключения выходов нескольких цифровых микросхем к одной нагрузке. Одним из способов объединения выходов является использование в выходных каскадах микросхем транзисторов, один из выводов которых (коллектор, эмиттер, сток, исток) никуда не подключен. Такой вывод называют открытым.Покажем схематически (рис. 3.25), как объединяются выходы микросхем с открытым коллектором. Такую схему называют «монтажным (проводным) ИЛИ». Если открытым является коллектор транзистора п-р-п-типа, эмиттер транзистора р-n-р-типа, сток транзистора с каналом n-типа, исток транзистора с каналом р-типа, то вывод обозначают символом Q. . Если открытым является коллектор транзистора р-п-р-типа, эмиттер транзистора п-р-п-типа, сток транзистора с каналом р-типа, исток транзистора с каналом и-типа, вывод обозначают символом О. Выходные каскады некоторых микросхем могут работать в таком режиме, когда микросхема оказывается фактически отключенной от нагрузки. Это так называемое третье (высокоимпедансное) состояние микросхемы. Использование третьего состояния является еще одним способом объединения выходов микросхем, который широко используется в вычислительной технике, при подключении к общей шине многих устройств. Приведем фрагмент схемы, поясняющей возникновение третьего состояния (рис. 3.26). Если оба транзистора закрыты, то микросхема и нагрузка фактически являются разъединенными. Наличие третьего состояния обозначают символом ◊.  При использовании в едином цифровом устройстве микросхем различных серий, и в особенности различных логик, может возникнуть проблема согласования уровней входных и выходных напряжений. Для указанных целей производятся специальные микросхемы, которые называют преобразователями уровня сигналов. 3.3.3. Особенности логических элементов различных логик Для конкретной серии микросхем характерно использование типового электронного узла — базового логического элемента. Этот элемент является основой построения самых разнообразных цифровых электронных устройств. Ниже рассмотрим особенности базовых логических элементов различных логик. Элементы транзисторно-транзисторной логики. Характерной особенностью ТТЛ является использование мно-гоэмиттерных транзисторов. Эти транзисторы сконструированы таким образом, что отдельные эмиттеры не оказывают влияния друг на друга. Каждому эмиттеру соответствует свой p-n-переход. В первом приближении многоэмиттерный транзистор может моделироваться схемой на диодах (см. пунктир на рис. 3.27). Упрощенная схема ТТЛ-элемента приведена на рис. 3.27. При мысленной замене многоэмиттерного транзистора диодами получаем элемент диодно-транзисторной логики «И-НЕ». Из анализа схемы можно сделать вывод, что если на один из входов или на оба входа подать низкий уровень напряжения, то ток базы транзистора Т2 будет равен нулю, и на коллекторе транзистора Т2 будет высокий уровень напряжения. Если на оба входа подать высокий уровень напряжения, то через базу Т2 транзистора будет протекать большой базовый ток и на коллекторе транзистора Т2 будет низкий уровень напряжения, т. е. д  анный элемент реализует функцию И-НЕ: ивых = и1 и2 . Базовый элемент ТТЛ содержит многоэмиттерный транзистор, выполняющий логическую операцию И, и анный элемент реализует функцию И-НЕ: ивых = и1 и2 . Базовый элемент ТТЛ содержит многоэмиттерный транзистор, выполняющий логическую операцию И, ис  ложный инвертор (рис. 3.28). Если на один или оба входа одновременно подан низкий уровень напряжения, то многоэмиттерный транзистор находится в состоянии насыщения и транзистор Т2 закрыт, а следовательно, закрыт и транзистор Т4, т. е. на выходе будет высокий уровень напряжения. Если на обоих входах одновременно действует высокий уровень напряжения, то ложный инвертор (рис. 3.28). Если на один или оба входа одновременно подан низкий уровень напряжения, то многоэмиттерный транзистор находится в состоянии насыщения и транзистор Т2 закрыт, а следовательно, закрыт и транзистор Т4, т. е. на выходе будет высокий уровень напряжения. Если на обоих входах одновременно действует высокий уровень напряжения, то транзистор Т2 открывается и входит в режим насыщения, что приводит к открытию и насыщению транзистора Т4 и запиранию транзистора Т3, т. е. реализуется функция И-НЕ. Для увеличения быстродействия элементов ТТЛ используются транзисторы с диодами Шоттки (транзисторы Шоттки).  Б  азовый логический элемент ТТЛШ (на примере серии К555). В качестве базового элемента серии микросхем К555 использован элемент И-НЕ. На рис. 3.29,а изображена схема этого элемента, а условное графическое обозначение транзистора Шоттки приведено на рис. 3.29,б. Такой транзистор эквивалентен рассмотренной выше паре из обычного транзистора и диода Шоттки. Транзистор VT4 — обычный биполярный транзистор. азовый логический элемент ТТЛШ (на примере серии К555). В качестве базового элемента серии микросхем К555 использован элемент И-НЕ. На рис. 3.29,а изображена схема этого элемента, а условное графическое обозначение транзистора Шоттки приведено на рис. 3.29,б. Такой транзистор эквивалентен рассмотренной выше паре из обычного транзистора и диода Шоттки. Транзистор VT4 — обычный биполярный транзистор.Если оба входных напряжения ивх1и ивх2имеют высокий уровень, то диоды VD3 и VD4 закрыты, транзисторы VT1, VT5 открыты и на выходе имеет место напряжение низкого уровня. Если хотя бы на одном входе имеется напряжение низкого уровня, то транзисторы VT1 и VT5 закрыты, а транзисторы VT3 и VT4 открыты, и на входе имеет место напряжение низкого уровня. Полезно отметить, что транзисторы VT3 и VT4 образуют так называемый составной транзистор (схему Дарлингтона). Микросхемы ТТЛШ серии К555 характеризуются следующими параметрами:

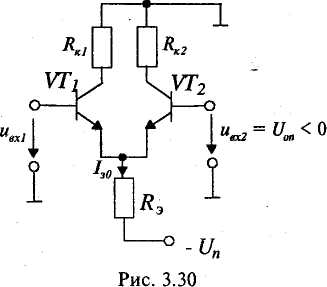

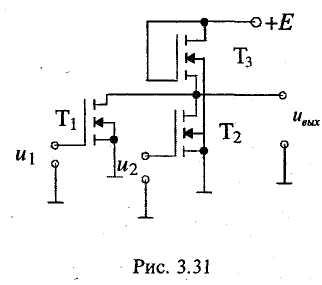

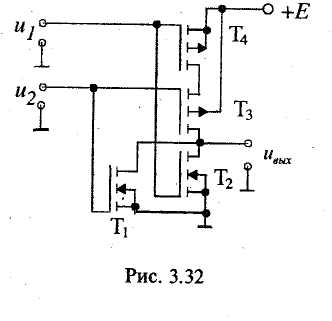

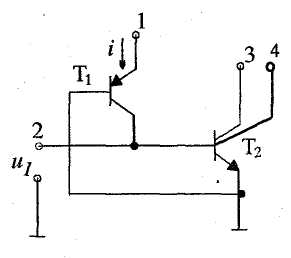

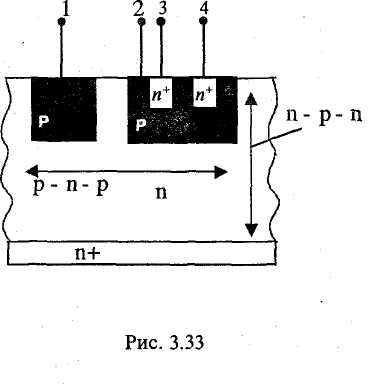

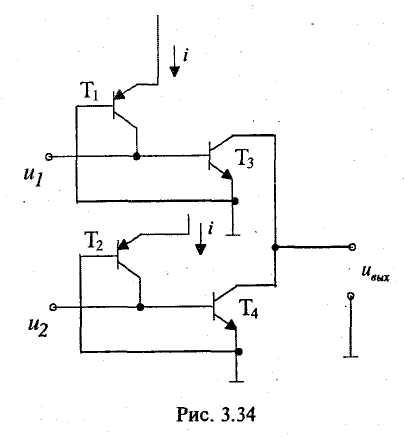

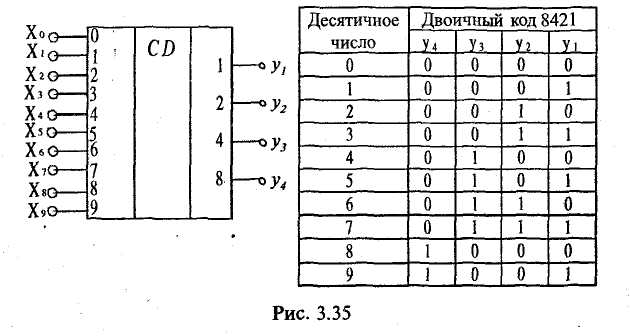

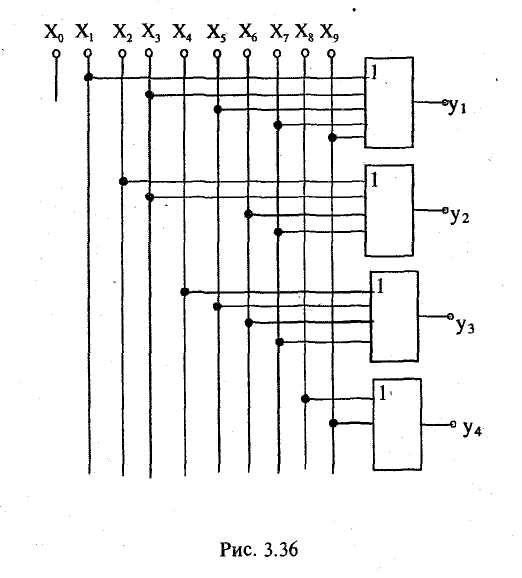

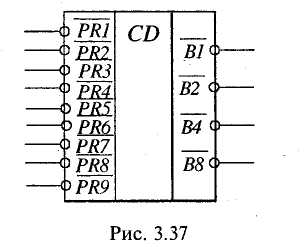

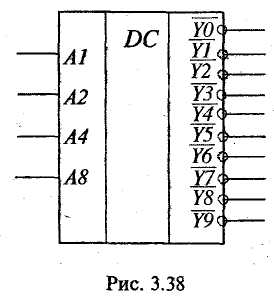

Микросхемы ТТЛШ обычно совместимы по логическим уровням, помехоустойчивости и напряжению питания с микросхемами ТТЛ. Время задержки распространения сигнала элементов ТТЛШ в среднем в два раза меньше по сравнению с аналогичными элементами ТТЛ. Особенности других логик. Основой базового логического элемента ЭСЛ является токовый ключ. Схема токового ключа (рис. 3.30) подобна схеме дифференциального усилителя. Необходимо обратить внимание на то, что микросхемы ЭСЛ питаются отрицательным напряжением (к примеру, —4,5 В для серии К1500). На базу транзистора VT2 подано отрицательное постоянное опорное напряжение Uоп. .Изменение входного напряжения ивх1 приводит к перераспределению постоянного тока /эо, заданного сопротивлением Rэ между транзисторами, что имеет следствием изменение напряжений на их коллекторах. Транзисторы не входят в режим насыщения, и это является одной из причин высокого быстродействия элементов ЭСЛ. Микросхемы серий 100, 500 имеют следующие параметры: напряжение питания- -5,2 В; потребляемая мощность — 100 мВт; коэффициент разветвления по выходу — 15; задержка распространения сигнала — 2,9 нс.  В микросхемах n-МОП и р-МОП используются ключи соответственно на МОП-транзисторах с n-каналом и динамической нагрузкой (рассмотрены выше) и на МОП-транзисторах с p-каналом. В качестве примера рассмотрим элемент логики п-МОП, реализующий функцию ИЛИ-НЕ (рис. 3.31). Он состоит из нагрузочного транзистора Т3 и двух управляющих транзисторов Т1 и Т2. Если оба транзистора Т1и Т2 закрыты, то на выходе устанавливается высокий уровень  н  апряжения. Если одно или оба напряжения и1 и и2имеют высокий уровень, то открывается один или оба транзистора Т1 и Т2 и на выходе устанавливается низкий уровень напряжения, т. е. реализуется функция ивых =и1+и2 . Для исключения потребления мощности логическим элементом в статическом состоянии используются комплементарные МДП — логические элементы (КМДП или КМОП-логика). В микросхемах КМОП используются комплементарные ключи на МОП-транзисторах. Они отличаются высокой помехоустойчивостью. Логика КМОП является очень перспективной. Рассмотренный ранее комплементарный ключ фактически является элементом НЕ (инвертором). апряжения. Если одно или оба напряжения и1 и и2имеют высокий уровень, то открывается один или оба транзистора Т1 и Т2 и на выходе устанавливается низкий уровень напряжения, т. е. реализуется функция ивых =и1+и2 . Для исключения потребления мощности логическим элементом в статическом состоянии используются комплементарные МДП — логические элементы (КМДП или КМОП-логика). В микросхемах КМОП используются комплементарные ключи на МОП-транзисторах. Они отличаются высокой помехоустойчивостью. Логика КМОП является очень перспективной. Рассмотренный ранее комплементарный ключ фактически является элементом НЕ (инвертором).Р  ассмотрим КМОП — логический элемент, реализующий функцию ИЛИ-НЕ (рис. 3.32). Если входные напряжения имеют низкие уровни (и, и и2 меньше порогового напряжения n-МОП-транзистора Uзи.порог.п), то транзисторы Т1 и Т2 закрыты, транзисторы Т3 и Т4 открыты и выходное напряжение имеет высокий уровень. Если одно или оба входных напряжения и1 и и2имеют высокий уровень, превышающий Uзи.порог.п, то открывается один или оба транзистора Т1 и Т2, а между истоком и затвором одного или обоих транзисторов Т3 и Т4 устанавливается низкое напряжение, что приводит к запиранию одного или обоих транзисторов Т3 и Т4, а следовательно, на выходе устанавливается низкое напряжение. Таким образом, этот элем ассмотрим КМОП — логический элемент, реализующий функцию ИЛИ-НЕ (рис. 3.32). Если входные напряжения имеют низкие уровни (и, и и2 меньше порогового напряжения n-МОП-транзистора Uзи.порог.п), то транзисторы Т1 и Т2 закрыты, транзисторы Т3 и Т4 открыты и выходное напряжение имеет высокий уровень. Если одно или оба входных напряжения и1 и и2имеют высокий уровень, превышающий Uзи.порог.п, то открывается один или оба транзистора Т1 и Т2, а между истоком и затвором одного или обоих транзисторов Т3 и Т4 устанавливается низкое напряжение, что приводит к запиранию одного или обоих транзисторов Т3 и Т4, а следовательно, на выходе устанавливается низкое напряжение. Таким образом, этот элем ент реализует функцию ивых=и1+и2и потребляет мощность от источника питания лишь в короткие промежутки времени, когда происходит его переключение. ент реализует функцию ивых=и1+и2и потребляет мощность от источника питания лишь в короткие промежутки времени, когда происходит его переключение.Интегральная инжекционная логика (ИИЛ или И2Л) построена на использовании биполярных транзисторов и применении оригинальных схемотехнических и технологических решений. Для нее характерно очень экономичное использование площади кристалла полупроводника. Элементы И2Л могут быть реализованы только в интегральном исполнении и не имеют аналогов в дискретной схемотехнике.  Структура такого элемента и его эквивалентная схема приведены на рис. 3.33, из которого видно, что транзистор T1 (р-п-р) расположен горизонтально, а многоколлекторный транзистор Т2 (п-р-п) расположен вертикально. Транзистор T1 выполняет роль инжектора, обеспечивающего поступление дырок из эмиттера транзистора T1 (при подаче на него положительного напряжения через ограничивающий резистор) в базу транзистора Т2. Если и1соответствует логическому «0», то инжекционный ток не протекает по базе многоколлекторного транзистора Т2 и токи в цепях коллекторов транзистора Т2 не протекают,   т. е. на выходах транзистора Т2 устанавливаются логические «1». При напряжении и1соответствующем логической «1», инжекционный ток протекает по базе транзистора Т2 и на выходах транзистора Т2 — логические нули. Рассмотрим реализацию элемента ИЛИ-НЕ на основе элемента, представленного на рис. 3.34 (для упрощения другие коллекторы многоколлекторных транзисторов Т3 и Т4 на рисунке не показаны). Когда на один или оба входа подается логический сигнал «1», то напряжение иеыхсоответствует логическому нулю. Если на обоих входах логические сигналы «0», то напряжение иеыхсоответствует логической единице. Логика на основе полупроводника из арсенида галлия GaAs характеризуется наиболее высоким быстродействием, что является следствием высокой подвижности электронов (в 3...6 раз больше по сравнению с кремнием). Микросхемы на основе GaAs могут работать на частотах порядка 10 ГГц и более.  3.4. КОМБИНАЦИОННЫЕ ЦИФРОВЫЕ УСТРОЙСТВА Логические устройства разделяют на два класса: комбинационные и последовательностные. Устройство называют комбинационным, если его выходные сигналы в некоторый момент времени однозначно определяются входными сигналами, имеющими место в этот момент времени. . Иначе устройство называют последовательностным или конечным автоматом (цифровым автоматом, автоматом с памятью). В последовательностных устройствах обязательно имеются элементы памяти. Состояние этих элементов зависит от предыстории поступления входных сигналов. Выходные сигналы последовательностных устройств определяются не только сигналами, имеющимися на входах в данный момент времени, но и состоянием элементов памяти. Таким образом, реакция последовательностного устройства на определенные входные сигналы зависит от предыстории его работы. Среди как комбинационных, так и последовательностных устройств выделяются типовые, наиболее широко используемые на практике. 3.4.1. Шифраторы, дешифраторы и преобразователи кодов Шифратор — это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду. Шифратор иногда называют «кодером» (от англ. coder) и используют, например, для перевода десятичных чисел, набранных на клавиатуре кнопочного пульта управления, в двоичные числа. Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением п = 2т, где п — число входов, т — число выходов. Так, для преобразования кода кнопочного пульта в четырехразрядное двоичное число достаточно использовать лишь 10 входов, в то время как полное число возможных входов будет равно 16 (n = 24= 16), поэтому шифратор 10x4 (из 10 в 4) будет неполным. Рассмотрим пример построения шифратора для преобразования десятиразрядного единичного кода (десятичных чисел от 0 до 9) в двоичный код. При этом предполагается, что сигнал, соответствующий логической единице, в каждый момент времени подается только на один вход. Условное обозначение такого шифратора и таблица соответствия кода приведены на рис. 3.35. Используя данную таблицу соответствия, запишем логические выражения, включая в логическую сумму те входны переменные, которые соответствуют единице некоторой выходной переменной. Так, на выходе у1будет логическая «1» тогда, когда логическая «1» будет или на входе Х1 ,или Х3, или Х5, или Х7, или X9, т. е. у1= Х1 + Х3 + Х5 + Х7 + X9. Аналогично получаем у2= Х2 + Х3 + Х6 + X7. у3= Х4 + Х5 + Х6 + Х7, у4= Х8 + X9. Представим на рис. 3.36 схему такого шифратора, используя элементы ИЛИ.  На практике часто используют шифратор с приоритетом. В таких шифраторах код двоичного числа соответствует наивысшему номеру входа, на который подан сигнал На практике часто используют шифратор с приоритетом. В таких шифраторах код двоичного числа соответствует наивысшему номеру входа, на который подан сигнал «1», т. е. на приоритетный шифратор допускается подавать сигналы на несколько входов, а он выставляет на выходе код числа, соответствующего старшему входу. Рассмотрим в качестве примера (рис. 3.37) шифратор с приоритетом (приоритетный шифратор) К555ИВЗ серии микросхем К555 (ТТЛШ). Шифратор имеет 9 инверсных  в   ходов, обозначенных через PRl,...,PR9 . Аббревиатура PRобозначает «приоритет». Шифратор имеет четыре инверсных выхода Bl,...,B8 . Аббревиатура В означает «шина» (от англ. bus). Цифры определяют значение активного уровня (нуля) в соответствующем разряде двоичного числа. Например, B8обозначает, что ноль на этом выходе соответствует числу 8. Очевидно, что это неполный шифратор. ходов, обозначенных через PRl,...,PR9 . Аббревиатура PRобозначает «приоритет». Шифратор имеет четыре инверсных выхода Bl,...,B8 . Аббревиатура В означает «шина» (от англ. bus). Цифры определяют значение активного уровня (нуля) в соответствующем разряде двоичного числа. Например, B8обозначает, что ноль на этом выходе соответствует числу 8. Очевидно, что это неполный шифратор.Если на всех входах — логическая единица, то на всех выходах также логическая единица, что соответствует числу 0 в так называемом инверсном коде (1111). Если хотя бы на одном входе имеется логический ноль, то состояние выходных сигналов определяется наибольшим номером входа, на котором имеется логический ноль, и не зависит от сигналов на входах, имеющих меньший номер. Н  апример, если на входе PR1 — логический ноль, а на всех остальных входах — логическая единица, то на выходах име- апример, если на входе PR1 — логический ноль, а на всех остальных входах — логическая единица, то на выходах име-ются следующие сигналы: В1 - 0, В2 - 1,В4- 1,В8 - I, что соответствует числу 1 в инверсном коде (1110). Е  сли на входе PR9 логический ноль, то независимо от других входных сигналов на выходах имеются следующие сли на входе PR9 логический ноль, то независимо от других входных сигналов на выходах имеются следующиесигналы: В1-0 ,В2-1 ,В4-1, В8-0, что соответствует числу 9 в инверсном коде (0110). Основное назначение шифратора — преобразование номера источника сигнала в код (например, номера нажатой кнопки некоторой клавиатуры). Дешифратором называется комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду. Число входов и выходов в так называемом полном дешифраторе связано соотношением т = 2n, где п — число входов, а т — число выходов. Если в работе дешифратора используется неполное число выходов, то такой дешифратор называется неполным. Так, например, дешифратор, имеющий 4 входа и 16 выходов, будет полным, а если бы выходов было только 10, то он являлся бы неполным. Обратимся для примера к дешифратору К555ИД6 серии К555 (рис. 3.38). Дешифратор имеет 4 прямых входа,  обозначенных через А1, ..., А8. Аббревиатура А обозначает «адрес» (от англ. address). Указанные входы называют адресными. Цифры определяют значения активного уровня (единицы) в соответствующем разряде двоичного числа. Дешифратор имеет 10 инверсных выходов Y0,...,Y9 . Цифры определяют десятичное число, соответствующее заданному двоичному числу на входах. Очевидно, что этот дешифратор неполный. Значение активного уровня (нуля) имеет тот выход, номер которого равен десятичному числу, определяемому двоичным числом на входе. Например, если на всех входах — логические нули, то на выходе Y0— логический ноль, а на остальных выходах — логическая единица. Если на входе А2 — логическая единица, а на остальных входах — логический ноль, то на выходе Y2 — логический ноль, а на остальных выходах — логическая единица. Если на входе — двоичное число, превышающее 9 (например, на всех входах единицы, что соответствует двоичному числу 1111 и десятичному числу 15), то на всех выходах — логическая единица. Дешифратор — одно из широко используемых логических устройств. Его применяют для построения различных комбинационных устройств. Рассмотренные шифраторы и дешифраторы являются примерами простейших преобразователей кодов. |