Лачин Электроника. Электроника рекомендовано Министерством образования Российской Федерации в качестве учебного пособия ля студентов высших технических учебных заведений РостовнаДону Феникс 2001 Рецензенты

Скачать 7.57 Mb. Скачать 7.57 Mb.

|

|

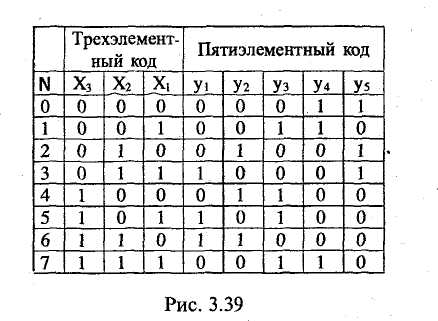

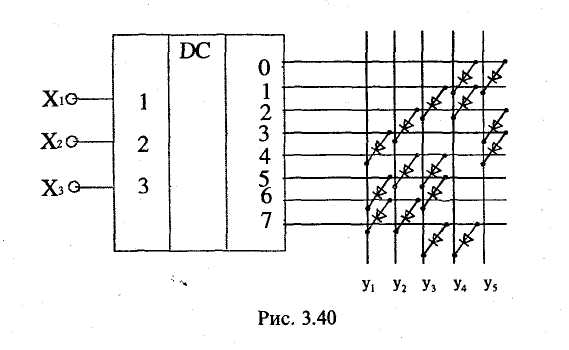

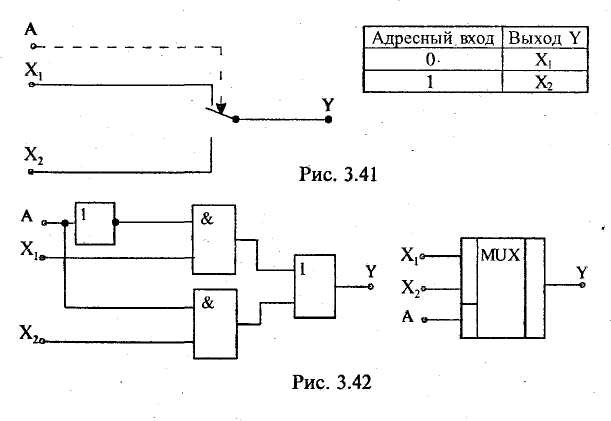

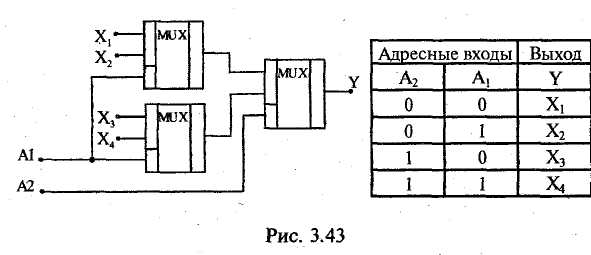

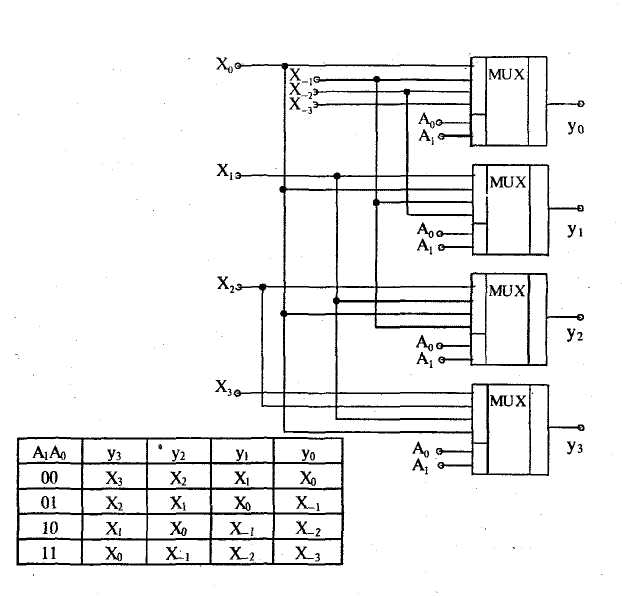

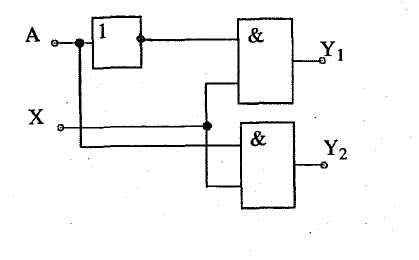

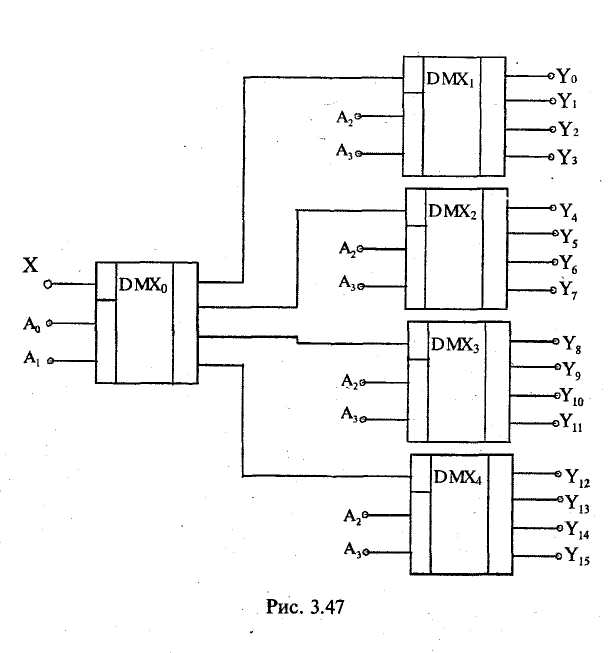

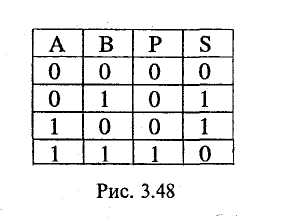

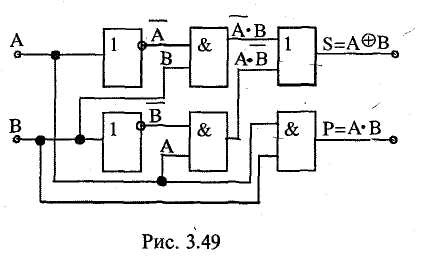

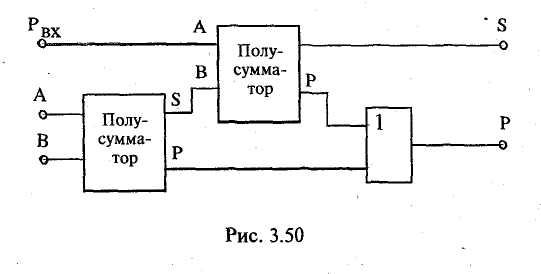

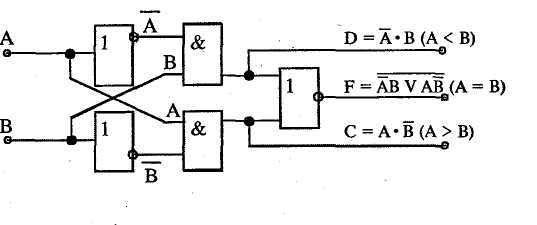

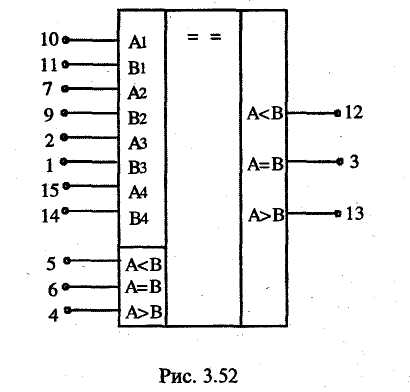

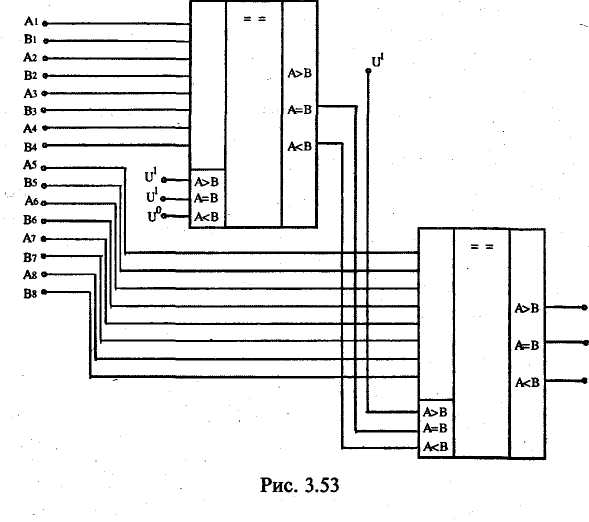

Преобразователями кодов, в общем случае, называют устройства, предназначенные для преобразования одного кода в другой, при этом часто они выполняют нестандартные преобразования кодов. Преобразователи кодов обозначают через X/Y. Рассмотрим особенности реализации преобразователя на примере преобразователя трехэлементного кода в пя-тиэлементный. Допустим, что необходимо реализовать таблицу соответствия кодов, приведенную на рис. 3.39. Здесь через N обозначено десятичное число, соответствующее входному двоичному коду. Преобразователи кодов часто создают по схеме дешифратор — шифратор. Дешифратор преобразует входной код в некоторое десятичное число, а затем шифратор формирует выходной код. Схема преобразователя, созданного по такому принципу, приведена на рис. 3.40, где использован матричный диодный шифратор. Принцип работы такого преобразователя довольно прост. Например, когда на всех входах дешифра-   тора логический «О», то на его выходе 0 появляется логическая «1», что приводит к появлению «1» на выходах у4и у5, т. е. реализуется первая строка таблицы соответствия кодов. Промышленность выпускает большое число шифраторов, дешифраторов и преобразователей кодов, таких как дешифратор 4x16 со стробированием (К555ИДЗ), преобразователь кода для управления светодиодной матрицей 7x5 (К155ИД8), преобразователь кода для управления шкальным индикатором (К155ИД15) и др. 3.4.2. Мультиплексоры и демультиплексоры Мультиплексором называют комбинационное устройство, обеспечивающее передачу в желаемом порядке цифровой информации, поступающей по нескольким входам на один выход. Мультиплексоры обозначают через MUX (от англ. multiplexor), а также через MS (от англ. multiplexorselector). Схематически мультиплексор можно изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких входов (их называют информационными) к одному выходу устройства. Кроме информационных входов в мультиплексоре имеются адресные входы и, как правило, разрешающие (стробирующие). Сигналы на адресных входах определяют, какой конкретно информационный канал подключен к выходу. Если между числом информационных входов и и числом адресных входов т действует соотношение п = 2т, то такой мультиплексор называют полным. Если п < 2т, то мультиплексор называют неполным. Разрешающие входы используют для расширения функциональных возможностей мультиплексора. Они используются для наращивания разрядности мультиплексора, синхронизации его работы с работой других узлов. Сигналы на разрешающих входах могут разрешать, а могут и запрещать подключение определенного входа к выходу, т. е. могут блокировать действие всего устройства. Рассмотрим функционирование двухвходового мультиплексора (2—>1), который условно изображен в виде коммутатора, а состояние его входов Х1 Х2 и выхода Y приведено в таблице (рис. 3.41). Исходя из таблицы, можно записать следующее уравнение: Y = X1A+X2A. На рис. 3.42 показаны реализация такого устройства и его условное графическое обозначение. Основой данной схемы являются две схемы совпадения на элементах И, которые при логическом уровне «1» на одном из своих входов повторяют на выходе то, что есть на другом входе. Если необходимо расширить число входов, то используют каскадное включение мультиплексоров. В качестве примера рассмотрим мультиплексор с четырьмя входами (4->1), построенный на основе мультиплексоров (2->1).  Схема и таблица состояний такого мультиплексора приведены на рис.3.43. Мультиплексоры являются универсальными логическими устройствами, на основе которых создают различные комбинационные и последовательностные схемы. Мультиплексоры могут использоваться в делителях частоты, триггерных устройствах, сдвигающих устройствах и др. Мультиплексоры часто используют для преобразования  параллельного двоичного кода в последовательный. Для такого преобразования достаточно подать на информационные входы мультиплексора параллельный двоичный код, а сигналы на адресные входы подавать в такой последовательности, чтобы к выходу поочередно подключались входы, начиная с первого и кончая последним. Рассмотрим пример использования мультиплексоров для реализации так называемого комбинационного устройства сдвига, обеспечивающего сдвиг двоичного, числа по разрядам. Принцип функционирования данного устройства понятен из схемы устройства и таблицы состояний его входов и выходов (рис. 3.44). В  обозначении мультиплексоров используют две русские буквы КП, например, промышленностью выпускаются такие мультиплексоры, как К155КП1, К531КШ8, К561КПЗ, К555КП17 и др. обозначении мультиплексоров используют две русские буквы КП, например, промышленностью выпускаются такие мультиплексоры, как К155КП1, К531КШ8, К561КПЗ, К555КП17 и др.Демультиплексором называют устройство, в котором сигналы с одного информационного входа, поступают в желаемой последовательности по нескольким выходам в зависимости от кода на адресных шинах. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. Демультиплексоры обозначают через DMX или DMS. Если соотношение между числом выходов п и числом адресных входов т определяется равенством п = 2т, то такой демультиплексор называется полным, при п < 2т де-мультиплексор является неполным. Р  ассмотрим функционирование демультиплексора с двумя выходами, который условно изображен в виде коммутатора, а состояние его входов и выходов приведено в таблице (рис. 3.45). Из этой таблицы следует: ассмотрим функционирование демультиплексора с двумя выходами, который условно изображен в виде коммутатора, а состояние его входов и выходов приведено в таблице (рис. 3.45). Из этой таблицы следует:Y1 = X А; Y2 = X А, т. е. реализовать такое устройство можно так, как показано на рис. 3.46.  Д  ля наращивания числа выходов демультиплексора используют каскадное включение демультиплексоров. В качестве примера (рис. 3.47) рассмотрим построение демультиплексоров с 16 выходами (1->16) на основе демультиплексоров с 4 выходами (1->4). При наличии на адресных шинах А0 и А1 нулей информационный вход X подключен к верхнему выходу DМХ0 и в зависимости от состояния адресных шин А2 и А3 он может быть подключен к одному из выходов DMX1 .Так, при А2 = А3 = О вход X подключен к Y0. При А0 = 1 и А1 = 0 вход X подключен к DMX2, в зависимости от состояния А2 и А3 вход соединяется с одним из выходов Y4-Y7 и т.д. ля наращивания числа выходов демультиплексора используют каскадное включение демультиплексоров. В качестве примера (рис. 3.47) рассмотрим построение демультиплексоров с 16 выходами (1->16) на основе демультиплексоров с 4 выходами (1->4). При наличии на адресных шинах А0 и А1 нулей информационный вход X подключен к верхнему выходу DМХ0 и в зависимости от состояния адресных шин А2 и А3 он может быть подключен к одному из выходов DMX1 .Так, при А2 = А3 = О вход X подключен к Y0. При А0 = 1 и А1 = 0 вход X подключен к DMX2, в зависимости от состояния А2 и А3 вход соединяется с одним из выходов Y4-Y7 и т.д.Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно рассматривать как де-мультиплексор, у которого информационный вход поддерживает напряжение выходов в активном состоянии, а адресные входы выполняют роль входов дешифратора. Поэтому в обозначении как дешифраторов, так и демультиплексоров используются одинаковые буквы — ИД. Выпускают дешифраторы (демультиплексоры) К155ИДЗ, К531ИД7 и др. При использовании КМОП-технологии можно построить двунаправленные ключи, которые обладают возможностью пропускать ток в обоих направлениях и передавать не только цифровые, но и аналоговые сигналы. Благодаря этому можно строить мультиплексоры-демультиплек-соры, которые могут использоваться либо как мультиплексоры, либо как демультиплексоры. Мультиплексоры-демультиплексоры обозначаются через MX. Среди выпускаемых мультиплексоров-демультиплексоров можно выделить такие, как К564КП1, К590КП1. Мультиплексоры-демультиплексоры входят в состав серий К176, К561, К591, К1564. 3.4.3. Сумматоры Сумматоры — это комбинационные устройства, предназначенные длясложения чисел. Рассмотрим сложение двух одноразрядных двоичных чисел, для чего составим таблицу сложения (таблицу истинности), в которой отразим значения входных чисел А и В, значение результата суммирования S и значение переноса в старший разряд Р (см. рис. 3.48).  Работа устройства, реализующего таблицу истинность (рис. 3.48), описывается следующими уравнениями S  = АВ + АВ;Р = АВ . Очевидно, что по отношении: к столбцу S реализуется логическая функция «исключающее ИЛИ», т. е. S = А + В. Устройство, реализующее таблицу (рис. 3.48), называют полусумматором, и оно имеет логическую структуру, изображенную на рис. 3.49. Поскольку = АВ + АВ;Р = АВ . Очевидно, что по отношении: к столбцу S реализуется логическая функция «исключающее ИЛИ», т. е. S = А + В. Устройство, реализующее таблицу (рис. 3.48), называют полусумматором, и оно имеет логическую структуру, изображенную на рис. 3.49. Посколькуполусумматор имеет только два входа, он может использоваться для суммирования лишь в младшем разряде. При суммировании двух многоразрядных чисел для каждого разряда (кроме младшего) необходимо использовать устройство, имеющее дополнительный вход переноса. Такое устройство (рис. 3.50) называют полным сумматором и его можно представить как объединение двух полусумматоров (Рвх — дополнительный вход переноса). Сумматор обозначают через SM.  3.4.4. Цифровые компараторы Цифровые компараторы выполняют сравнение двух чисел, заданных в двоичном коде. Они могут определять равенство двух двоичных чисел А и В с одинаковым количеством разрядов либо вид неравенства А>В или А<В. Цифровые компараторы имеют три выхода. Схема одноразрядного компаратора представляет собой структуру логического элемента «исключающее ИЛИ-НЕ» (рис. 3.51).  Из анализа схемы следует, что если А = В, то F = 1, в противном случае, т. е. при А /=В, F = 0. Если А > В, т. е. А = 1, В = 0, то С = 1, а если А < В, т. е. А = 0, В = 1, то D = l. Если попарно равны между собой все разряды двух п-разрядных двоичных чисел, то равны и эти два числа А и В. Применяя цифровой компаратор для каждого разряда, например, четырехзначных чисел, и определяя значения F1, F2, F3, F4 логических переменных на выходах компараторов, факт равенства А = В установим в случае, когда F = F1 • F2 • F3 • F4 = 1. Если же F = 0, то А/=В. Неравенство А > В обеспечивается (для четырехразрядного числа) в четырех случаях: или А4 > В4, или А4 = В4 и А3 > В3, или А4 = В4, А3 = В3 и А2>В2, или А4 = В4, А3 = В3, А2 = В2 и A1 > В1 (где А4 и В4 — старшие разряды чисел А и В). Очевидно, что если поменять местами А1 и B1 ,то будет выполняться неравенство А < В. Цифровые компараторы выпускают, как правило, в виде самостоятельных микросхем. Так, микросхема К564ИП2 (рис. 3.52) является четырехразрядным компаратором, в котором каждый из одноразрядных компараторов аналогичен рассмотренной ранее схеме. Данная микросхема имеет расширяющие входы А<В, А=В, А>В, что позволяет наращивать разрядность обоих чисел. Для этого компараторы соединяют каскадно или параллельно (пирамидально).  Р  ассмотрим каскадное соединение компараторов К564ИП2 для сравнения двух восьмиразрядных чисел (рис. 3.53). При этом соединении выходы А = В и А < В предыдущей микросхемы (младшие разряды) подключают к соответствующим входам последующей. На входы А<В, А=В, А>В микросхемы младших разрядов подают соответственно потенциалы U0, U1иU1( U0 соответствует логическому 0, a U1— «1»). В последующих микросхемах на входах А > В поддерживают потенциал логической единицы U1. ассмотрим каскадное соединение компараторов К564ИП2 для сравнения двух восьмиразрядных чисел (рис. 3.53). При этом соединении выходы А = В и А < В предыдущей микросхемы (младшие разряды) подключают к соответствующим входам последующей. На входы А<В, А=В, А>В микросхемы младших разрядов подают соответственно потенциалы U0, U1иU1( U0 соответствует логическому 0, a U1— «1»). В последующих микросхемах на входах А > В поддерживают потенциал логической единицы U1.3.5. ПОСЛЕДОВАТЕЛЬНОСТНЫЕ ЦИФРОВЫЕ УСТРОЙСТВА 3.5.1. Триггеры Триггер — простейшее последовательностное устройство, которое может находиться в одном из двух возможных состояний и переходить из одного состояния в дру- гое под воздействием входных сигналов. Триггер является базовым элементом последовательностных логических устройств. Входы триггера разделяют на информационные и управляющие (вспомогательные). Это разделение в значительной степени условно. Информационные входы используются для управления состоянием триггера. Управляющие входы обычно используются для предварительной установки триггера в некоторое состояние и для синхронизации. Триггеры могут иметь 2 выхода: прямой Qи инверсный Q. Триггеры классифицируют по различным признакам, поэтому существует достаточно большое число классификаций. К сожалению, эти классификации не образуют стройной системы, но инженеру необходимо их знать. Триггеры классифицируют по следующим признакам:

Различают асинхронные и синхронные триггеры. Асинхронный триггер изменяет свое состояние непосредственно в момент появления соответствующего информационного сигнала. Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают терминами «строб», «такт». Синхронные триггеры в свою очередь подразделяют на триггеры со статическим (статические) и динамическим (динамические) управлением по входу синхронизации С. Статические триггеры воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход). Динамические триггеры воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вхОд) или от 1 к 0 (инверсный динамический С-вход). Статические триггеры в свою очередь подразделяют на одноступенчатые (однотактные) и двухступенчатые (двухтактные). В одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом —две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают через ТТ. По функциональным возможностям триггеры разделяют на следующие классы:

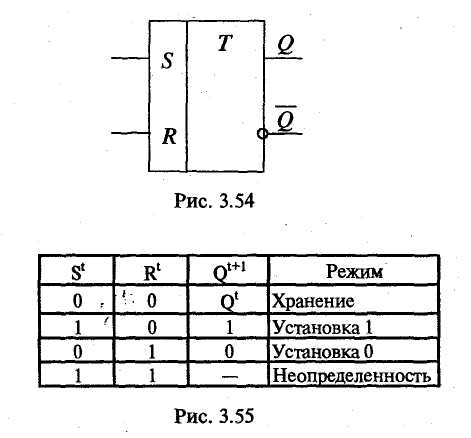

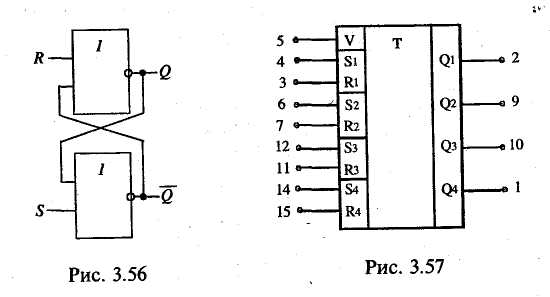

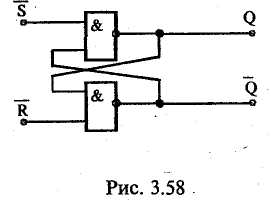

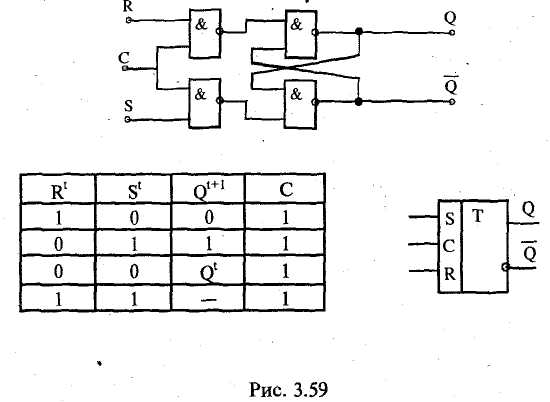

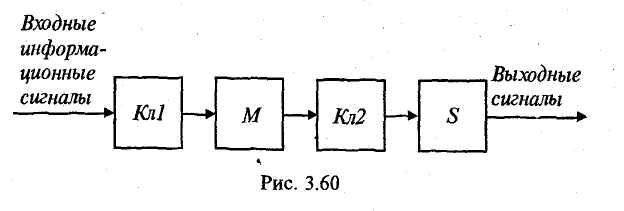

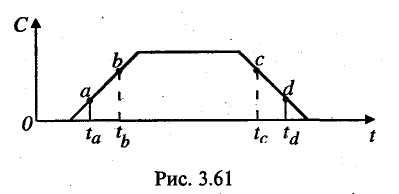

Входы триггеров обычно обозначают следующим образом: S — вход для установки в состояние «1»; R — вход для установки в состояние «0»; J — вход для установки в состояние «1» в универсальном триггере; К — вход для установки в состояние «0» в универсальном триггере; Т — счетный (общий) вход; D — вход для установки в состояние «1» или в состояние «0»; V — дополнительный управляющий вход для разрешения приема информации (иногда используют букву Е вместо V). Рассмотрим некоторые типы триггеров и их реализацию на логических элементах. Обратимся к асинхронному RS-триггеру, имеющему условное графическое обозначение, приведенное на рис. 3.54. Триггер имеет два информационных входа: S (от англ. set) и R (от англ. reset). З  акон функционирования триггеров удобно описывать таблицей переходов, которую иногда также называют таблицей истинности (рис. 3.55). Через S',R',Q' обозначены акон функционирования триггеров удобно описывать таблицей переходов, которую иногда также называют таблицей истинности (рис. 3.55). Через S',R',Q' обозначенысоответствующие логические сигналы, имеющие место в некоторый момент времени t, а черезQt+1— выходной сигнал в следующий момент времени t+1. Комбинацию входных сигналов S' =l,R' =1 часто называют запрещенной, так как после нее триггер оказывается в состоянии (1 или 0), предсказать которое заранее невозможно. Подобных ситуаций нужно избегать. Рассматриваемый триггер может быть реализован На двух элементах ИЛИ-НЕ (рис. 3.56). Необходимо убедиться, что эта схема функционирует в полном соответствии с приведенной выше таблицей переходов. М  икросхема К564ТР2 содержит 4 асинхронных RS-триггера и один управляющий вход (рис. 3.57). При подаче на вход V низкого уровня выходы триггеров отключаются от выводов микросхем и переходят в третье так называемое высокоимпедансное состояние. При подаче на вход V логического сигнала «1» триггеры работают в соответствии с вышеприведенной таблицей переходов. икросхема К564ТР2 содержит 4 асинхронных RS-триггера и один управляющий вход (рис. 3.57). При подаче на вход V низкого уровня выходы триггеров отключаются от выводов микросхем и переходят в третье так называемое высокоимпедансное состояние. При подаче на вход V логического сигнала «1» триггеры работают в соответствии с вышеприведенной таблицей переходов.В асинхронном RS-триггере на элементах И-НЕ переключение производится логическим «0», подаваемым на вход Rили S, т. е. реализуется обратная рассмотренной ранее таблица переходов (рис. 3.58). Запрещенная комбинация соответствует логическим «0» на обоих входах.  Р  ассмотрим синхронный RS-триггер (рис. 3.59). Если на входе С — логический «0», то и на выходе верхнего входного элемента «И-НЕ», и на выходе нижнего будет логическая «1». А это, как отмечалось выше, обеспечивает хранение информации. Таким образом, если на входе С — логический «0», то воздействие на входы R, S не приводит к изменению состояния триггера. Если же на вход синхронизации С подана логическая единица, то схема реагирует на входные сигналы точно так же, как и рассмотренная ранее (рис. 3.56). ассмотрим синхронный RS-триггер (рис. 3.59). Если на входе С — логический «0», то и на выходе верхнего входного элемента «И-НЕ», и на выходе нижнего будет логическая «1». А это, как отмечалось выше, обеспечивает хранение информации. Таким образом, если на входе С — логический «0», то воздействие на входы R, S не приводит к изменению состояния триггера. Если же на вход синхронизации С подана логическая единица, то схема реагирует на входные сигналы точно так же, как и рассмотренная ранее (рис. 3.56).Рассмотрим принцип построения двухступенчатого триггера, который называют также триггером типа MS (от англ. master, slave, что переводят обычно как «ведущий» и «ведомый»). Его упрощенная структурная схема приведена на рис. 3.60. В схеме имеются два одноступенчатых триггера (ведущий М и ведомый S) и два электронных ключа (Кл1 и Кл2).   Временная диаграмма сигнала синхронизации, поясняющая работу триггера, приведена на рис. 3.61. Рассмотрим ряд временных интервалов указанной диаграммы:

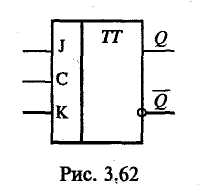

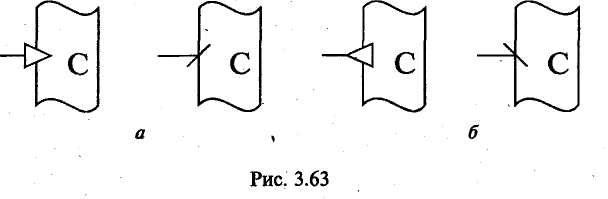

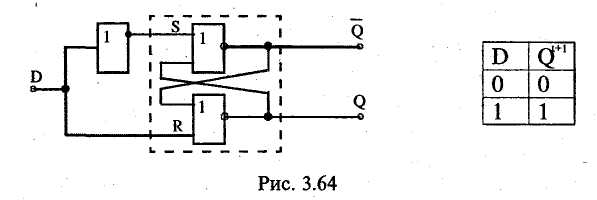

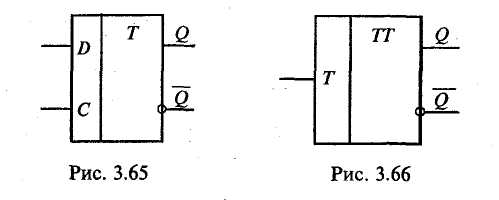

Рассмотрим JK-триггер (от англ. jumpи keep), отличающийся от рассмотренного RS-триггера тем, что появление на обоих информационных входах (J и К) логических единиц (для прямых входов) приводит к изменению состояния триггера. Такая комбинация сигналов для Ж-триг-гера не является запрещенной. В остальном JK-триггер подобен RS-триггеру, причем роль входа S играет вход J, а роль входа R — вход К. JK-триггеры реализуют в виде триггеров типа MS или в виде динамических триггеров (т. е. JK-триггеры являются синхронными). На рис. 3.62 приведено условное графическое обозначение двухступенчатого Ж-триггера.  Обратимся к динамическим триггерам. Для них характерно блокирование информационных входов в тот момент, когда полученная информация передается на выход. Нужно отметить, что в отношении реакции на входные сигналы динамический триггер, срабатывающий при изменении сигнала на входе С от 1 к 0, подобен рассмотренному двухступенчатому триггеру, хотя они отличаются внутренним устройством. Для прямого динамического С-входа используют обозначения, приведенные на рис. 3.63, а, а для инверсного динамического С-входа, используют обозначения, приведенные на рис. 3.63, б. Рассмотрим D-триггер (от англ. delay), повторяющий на своем выходе состояние входа. Рассуждая чисто Теоретически, D-триггер можно образовать из любых RS- или  JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы (рис. 3.64). Хранение информации в D-триггерах обеспечивается за счет синхронизации, поэтому все реальные D-тригге-ры имеют два входа: информационный D и синхрониза-  ции С. В этом триггере сигнал на входе по сигналу синхронизации записывается и передается на выход. Так как информация на выходе остается неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защелкой. Условное графическое обозначение D-триггера приведено на рис. 3.65. Р  ассмотрим Т-триггер, который изменяет свое логическое состояние на противоположное по каждому активному сигналу на информационном входе Т. Условное графическое ассмотрим Т-триггер, который изменяет свое логическое состояние на противоположное по каждому активному сигналу на информационном входе Т. Условное графическоеобозначение двухступенчатого Т-триггера приведено на рис. 3.66. 3.5.2. Счетчики импульсов Счетчик импульсов — это последовательностное цифровое устройство, обеспечивающее хранение слова информации и выполнение над ним микрооперации счета, заключающейся в изменении значения числа в счетчике на 1. По существу счетчик представляет собой совокупность соединенных определенным образом триггеров. Основной параметр счетчика — модуль счета. Это максимальное число единичных сигналов, которое может быть сосчитано счетчиком. Счетчики обозначают через СТ (от англ. counter). Счетчики классифицируют: по модулю счета:

по способу формирования внутренних связей: • с последовательным переносом;

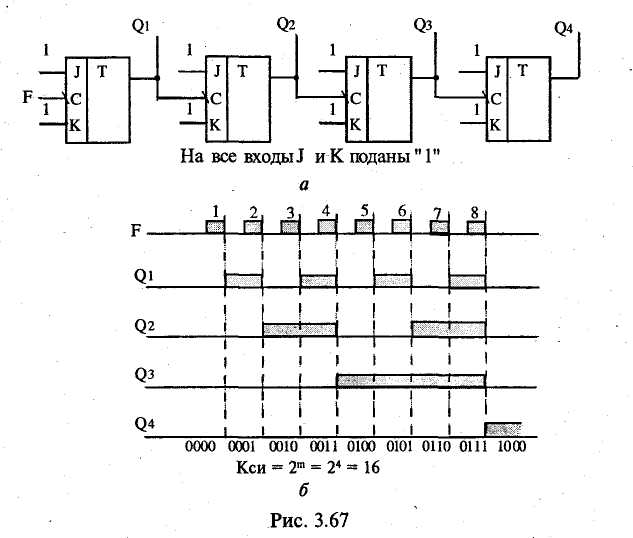

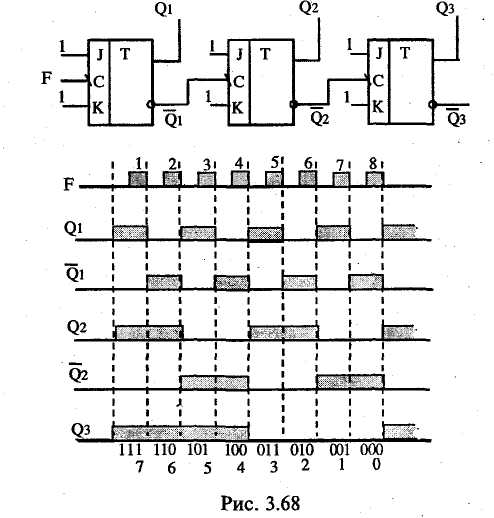

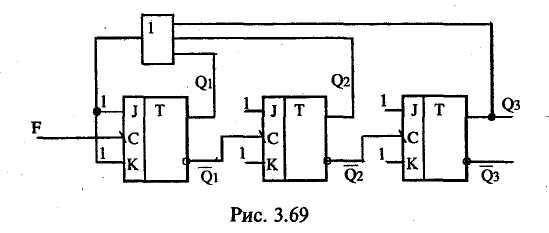

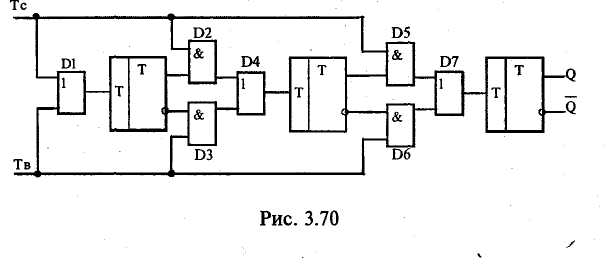

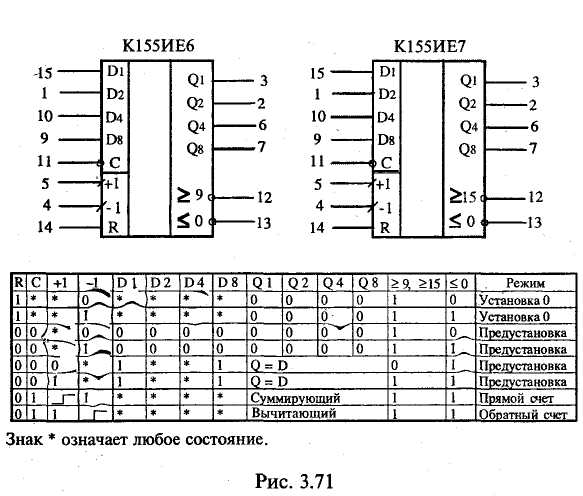

Рассмотрим суммирующий счетчик (рис. 3.67, а). Такой счетчик построен на четырех JK-триггерах, которые при наличии на обоих входах логического сигнала «1» переключаются в моменты появления на входах синхронизации отрицательных перепадов напряжения. Временные диаграммы, иллюстрирующие работу счетчика, приведены на рис. 3.67, б. Через Кси обозначен модуль счета (коэффициент счета импульсов). Состояние левого триггера соответствует младшему разряду двоичного числа, а правого — старшему разряду. В исходном состоянии на всех триггерах установлены логические нули. Каждый триггер меняет свое состояние лишь в тот момент,  когда на него действует отрицательный перепад напряжения. Таким образом, данный счетчик реализует суммирование входных импульсов. Из временных диаграмм видно, что частота каждого последующего импульса в два раза меньше, чем предыдущая, т. е. каждый триггер делит частоту входного сигнала на два, что и используется в делителях частоты. Рассмотрим трехразрядный вычитающий счетчик с последовательным переносом, схема и временные диаграммы работы которого приведены на рис. 3.68. В счетчике используются три JK-триггера, каждый из которых работает в режиме Т-триггера (триггера со счетным входом). На входы J и К каждого триггера поданы логические 1, поэтому по приходу заднего фронта импульса,  подаваемого на его вход синхронизации С, каждый триггер изменяет предыдущее состояние. Вначале сигналы на выходах всех триггеров равны 1. Это соответствует хранению в счетчике двоичного числа 111 или десятичного числа 7. После окончания первого импульса Fпервый триггер изменяет состояние: сигнал Q1 станет равным 0, a Q1— 1. Остальные триггеры при этом свое состояние не изменяют. После окончания второго импульса синхронизации первый триггер вновь изменяет свое состояние, переходя в состояние 1, {Qx=0). Это обеспечивает изменение состояния второго триггера (второй триггер изменяет состояние с некоторой задержкой по отношению к окончанию второго импульса синхронизации, так как для его опрокидывания необходимо время, соответствующее времени срабатывания его самого и первого триггера). После первого импульса F счетчик хранит состояние ПО. Дальнейшее изменение состояния счетчика происходит аналогично изложенному выше. После состояния 000 счетчик вновь переходит в состояние 111. Рассмотрим трехразрядный самоостанавливающийся вычитающий счетчик с последовательным переносом (рис. 3.69). После перехода счетчика в состояние 000 на выходах всех триггеров возникает сигнал логического 0, который подается через логический элемент ИЛИ на входы J и К первого триггера, после чего этот триггер выходит   из режима Т-триггера и перестает реагировать на импульсы F. Рассмотрим трехразрядный реверсивный счетчик с последовательным переносом (рис. 3.70). В режиме вычитания входные сигналы должны подаваться на вход Тв. На вход Тс при этом подается сигнал логического 0. Пусть все триггеры находятся в состоянии 111. Когда первый сигнал поступает на вход Тв, на входе Т первого триггера появляется логическая 1, и он изменяет свое состояние. После этого на его инверсном входе возникает сигнал логической 1. При поступлении второго импульса на вход Тв на входе второго триггера появится логическая 1, поэтому второй триггер изменит свое состояние (первый триггер также изменит свое состояние по приходу второго импульса). Дальнейшее изменение состояния происходит аналогично. В режиме сложения счетчик работает аналогично 4-разрядному суммирующему счетчику. При этом сигнал подается на вход Тс. На вход Тв подается логический 0. В качестве примера рассмотрим микросхемы реверсивных счетчиков (рис: 3.71) с параллельным переносом серии 155 (ТТЛ): ИЕ6 — двоично-десятичный реверсивный счетчик; И  Е7 — двоичный реверсивный счетчик. Е7 — двоичный реверсивный счетчик.Направление счета определяется тем, на какой вывод (5 или 4) подаются импульсы. Входы 1,9,10, 15 — информационные, а вход 11 используется для предварительной записи. Эти 5 входов позволяют осуществить предварительную запись в счетчик (предустановку). Для этого нужно подать соответствующие данные на информационные входы, а затем подать импульс записи низкого уровня на вход 11, и счетчик запомнит число. Вход 14 — вход установки О при подаче высокого уровня напряжения. Для построения счетчиков большей разрядности используются выходы прямого и обратного переноса (выводы 12 и13 соответственно). С вывода 12 сигнал должен подаваться на вход прямого счета следующего каскада, а с 13 — на вход обратного счета. 3.5.3. Регистры Регистр — это последовательностное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами. Типичными являются следующие операции:

• установка регистра в начальное состояние (сброс). Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединенных друг с другом при помощи комбинационных цифровых устройств. Регистры классифицируются по следующим видам:

В свою очередь сдвигающие регистры делятся: • по способу ввода-вывода информации на

• по направлению передачи информации на

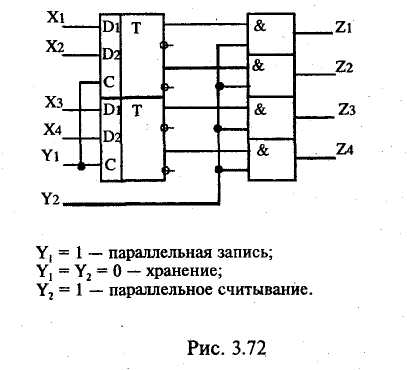

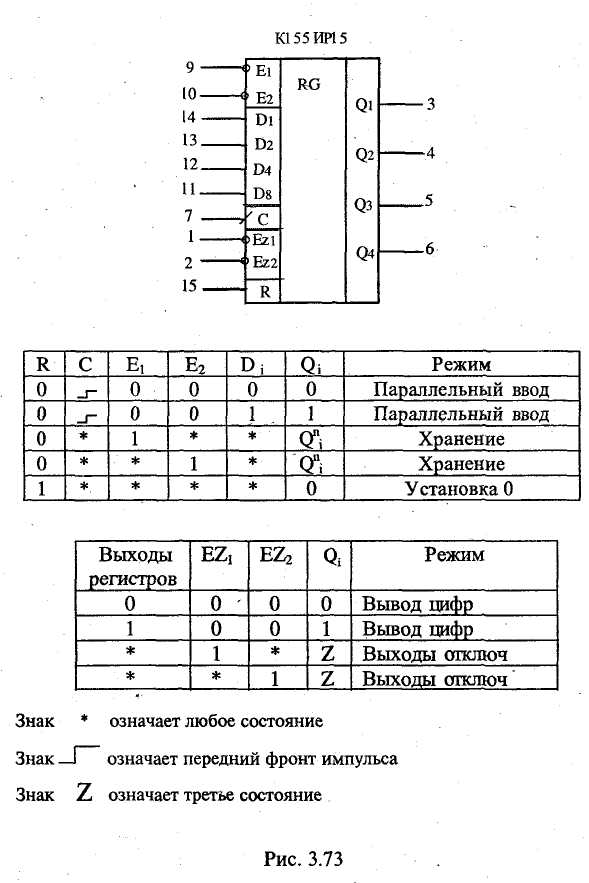

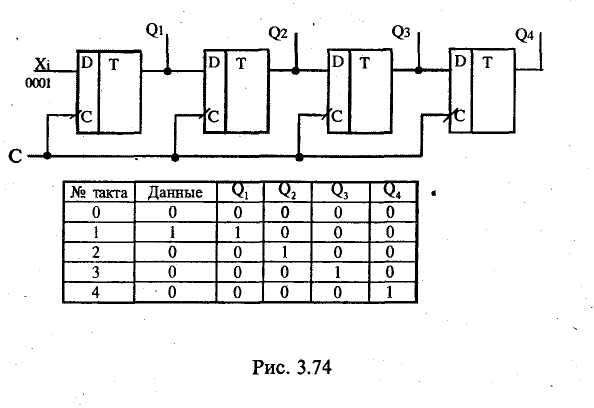

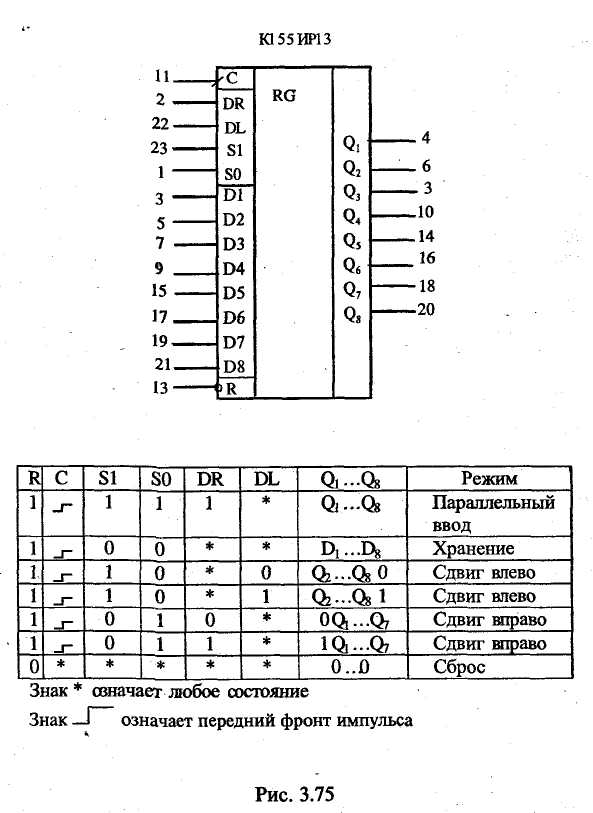

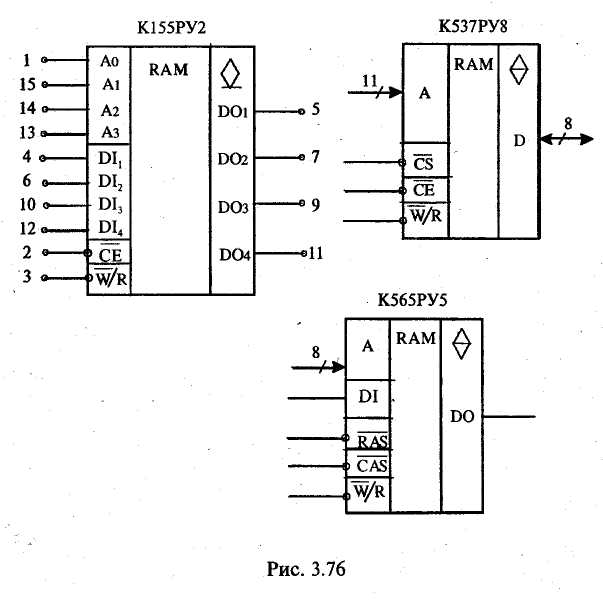

Р  ассмотрим накопительный регистр с параллельными вводом и выводом информации (рис. 3.72). Основой ассмотрим накопительный регистр с параллельными вводом и выводом информации (рис. 3.72). Основой регистра являются D-триггеры, которые на своих выходах повторяют значения сигналов на входах X1 —Х4 (информационные входы) при логическом сигнале 1 на входе синхронизации (т. е. осуществляется параллельный ввод входной информации в регистр). На четырех двухвходо-вых элементах «И» реализованы схемы совпадения, входные сигналы которых совпадают с выходными сигналами триггеров в том случае, когда йа вход Y2 подана логическая единица. Таким образом осуществляется параллельный вывод информации. В качестве примера рассмотрим микросхему регистра К155ИР15. Приведем условное обозначение и таблицы внутренних и выходных состояний (рис. 3.73).  На рис. 3.74 представлен сдвигающий регистр. В исходном состоянии на выходах всех триггеров логический сигнал «О». При подаче логического сигнала «1» младшего разряда числа на вход 1 -го триггера он запоминается в нем в момент действия положительного перепада тактового импульса. Состояние же остальных триггеров не меняется, так как на их входах были логические сигналы «0». Во время второго тактового импульса на входе первого триггера На рис. 3.74 представлен сдвигающий регистр. В исходном состоянии на выходах всех триггеров логический сигнал «О». При подаче логического сигнала «1» младшего разряда числа на вход 1 -го триггера он запоминается в нем в момент действия положительного перепада тактового импульса. Состояние же остальных триггеров не меняется, так как на их входах были логические сигналы «0». Во время второго тактового импульса на входе первого триггера действует логический сигнал «0», на входе второго триггера — логический сигнал «1», на входе третьего и четвертого — логические сигналы «0». Эти сигналы запоминаются триггерами, на входе которых они действовали, т. е. осуществляется сдвиг единицы вправо и т. д. Таким образом, за четыре такта осуществляется последовательный ввод в регистр 4-разрядного двоичного числа.  В качестве примера приведем микросхему сдвигающего регистра К155ИР13 и его таблицу состояний (рис. 3.75). В качестве примера приведем микросхему сдвигающего регистра К155ИР13 и его таблицу состояний (рис. 3.75).3.6. ЦИФРОВЫЕ ЗАПОМИНАЮЩИЙ УСТРОЙСТВА 3.6.1. Общая характеристика устройств Цифровыми запоминающими называют устройства, предназначенные для записи, хранения и считывания информации, представленной в цифровом коде. Запоминающие устройства (ЗУ) классифицируют по назначению, технологии изготовления, способу адресации, способу хранения информации и т.д. По назначению запоминающие устройства подразделяют на оперативные запоминающие устройства (ОЗУ) и постоянные запоминающие устройства (ПЗУ). ОЗУ обеспечивает режим записи, хранения и считывания информации в процессе ее обработки. ПЗУ в рабочем режиме допускает только считывание информации. По технологии изготовления ЗУ делятся на биполярные (ТТЛ-,ТТЛШ-, ЭСЛ-, И2Л-технологии) и униполярные (n-МОП, КМОП- и другие технологии). По способу адресации все ЗУ делятся на адресные и безадресные (ассоциативные). В адресных ЗУ обращение к элементам памяти производится в соответствии с их адресом, задаваемым двоичным кодом. Большинство ЗУ являются адресными. В ассоциативных ЗУ считывание информации осуществляется по ее содержанию и не зависит от физических координат элементов памяти. Ассоциативные ЗУ не имеют входов адресных сигналов. К основным параметрам ЗУ относятся информационная емкость, потребляемая мощность, время хранения информации, быстродействие и др. Информационная емкость определяется числом ячеек памяти ЗУ и указывает максимальный объем хранимой информации. Если ЗУ рассчитано на хранение п чисел (слов), каждое из которых имеет от разрядов, то информационная емкость N определяется выражением N = п • т. Так, например, если ЗУ предназначено для хранения 16 слов, каждое из которых содержит 4 разряда, то ЗУ имеет структурную организацию 16 х 4 и информационную емкость N=16x4 = 64 бит. ЗУ емкостью 64 бит может быть организовано и как ЗУ 32 х 2 (32 слова по 2 разряда каждое). Емкость часто выражают в байтах (1 байт = 8 бит). Емкость ЗУ составляет от нескольких десятков до нескольких миллионов бит. Потребляемая мощность — мощность, потребляемая ЗУ в установившемся режиме работы. Время хранения информации — интервал времени, в течение которого ЗУ сохраняет информацию в заданном режиме. Быстродействие — промежуток времени, необходимый для записи или считывания информации. Основой любого ЗУ является матрица памяти (накопитель), которая состоит из п строк. Каждая строка имеет т ячеек памяти, образующих m.-разрядное слово. Соответствующие шины в матрице памяти управляются от дешифраторов строк и столбцов. Выбор требуемой ячейки памяти осуществляется с помощью дешифраторов строк и столбцов путем подачи на них соответствующих адресных сигналов. 3.6.2. Оперативные запоминающие устройства ОЗУ (их обозначают английской аббревиатурой RAM) подразделяются на статические и динамические. В статических ОЗУ запоминающая ячейка представляет собой триггер на биполярных или полевых транзисторах, что определяет потенциальный характер управляющих сигналов и возможность считывания информации без ее разрушения. В динамических ОЗУ элементом памяти является емкость (например, затвора полевого транзистора), что требует периодического восстановления (регенерации) записанной информации в процессе ее хранения. ОЗУ динамического типа позволяют реализовать большой объем памяти, но они сложнее в использовании, так как необходимо наличие специальной схемы управления режимами работы. В современных динамических ОЗУ имеются встроенные системы регенерации и синхронизации. Такие ОЗУ по внешним сигналам управления не отличаются от статических ОЗУ. Рассмотрим в качестве примера некоторые микросхемы ОЗУ (рис. 3.76).  Выводы микросхем имеют следующие назначения: CS — выбор микросхемы, Аi — адресные входы, DIi — информационные входы, DOi — информационные выходы, W/R — разрешение записи/считывания, RAS — строб адреса строки, CAS — строб адреса столбца, СЕ — сигнал разрешения. Микросхема К155РУ2 — это статическое ОЗУ с открытым коллекторным выходом — выполнена на основе ТТЛ-структур емкостью 64 бит. Имеет структуру 16x4, т. е. может хранить 16 слов длиной 4 разряда каждое. Микросхема К537РУ8 — это статическое ОЗУ объемом 2 Кбайта, выполнена на основе структур КМОП, по входу и выходу совместима с ТТЛ-структурами. Имеет двунаправленную 8-разрядную шину данных, которая используется и для записи, и для считывания информации. Микросхема К565РУ5 — это динамическое ОЗУ на основе n-МОП-структур, по входам и выходам совместима с ТТЛ-структурами, имеет организацию 64Кх1. Шина адреса работает в мультиплексном режиме. Вначале на ней выставляются адреса строк, которые запоминаются во внутреннем регистре по спаду сигнала RAS. Затем выставляются адреса столбцов, которые запоминаются по спаду сигнала CAS. 3.6.3. Постоянные запоминающие устройства Все ПЗУ можно разделить на следующие группы:

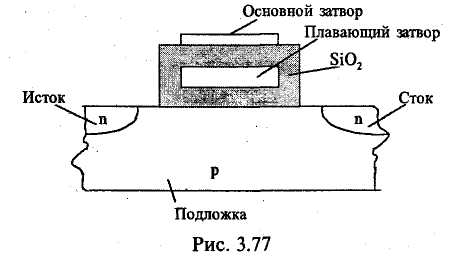

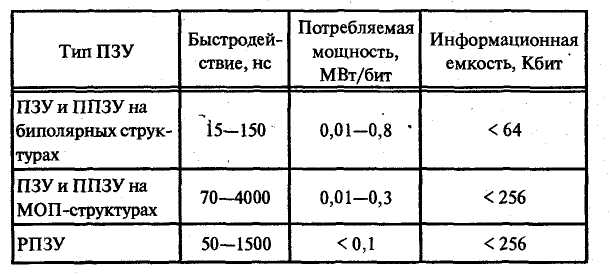

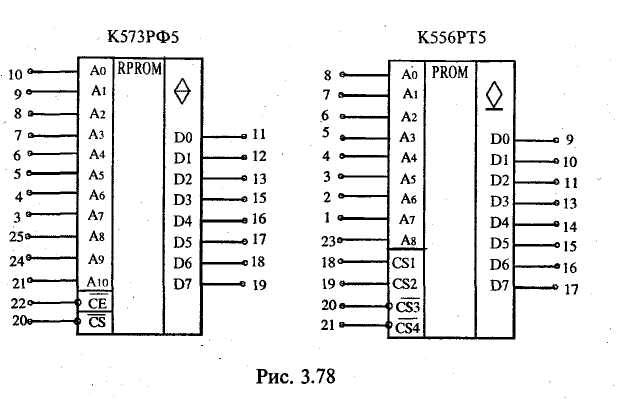

Для обеспечения возможности объединения по выходу при наращивании памяти все ПЗУ имеют выходы с тремя состояниями или открытые коллекторные выходы. В ППЗУ накопитель построен на запоминающих ячейках с плавкими перемычками, изготовленными из нихрома или других тугоплавких материалов. Процесс записи состоит в избирательном пережигании плавких перемычек. В РПЗУ запоминающие ячейки строятся на основе МОП-технологий. Используются различные физические явления хранения заряда на границе между двумя различными диэлектрическими средами или проводящей и диэлектрической средой. В первом случае диэлектрик под затвором МОП-транзистора делают из двух слоев: нитрида кремния и двуокиси кремния (SiN4 — SiO2). Было обнаружено, что в сложной структуре SiN4 — SiO2 при изменении электрического напряжения возникает гистерезис заряда на границе раздела двух слоев, что и позволяет создавать запоминающие ячейки. Во втором случае основой запоминающей ячейки является лавинно-инжекционный МОП-транзистор с плавающим затвором (ЛИПЗ МОП). Упрощенная структура такого транзистора приведена на рис. 3.77.  В лавинно-инжекционном транзисторе с плавающим затвором при достаточно большом напряжении на стоке происходит обратимый лавинный пробой диэлектрика, и в область плавающего затвора инжектируются носители заряда. Поскольку плавающий затвор окружен диэлектриком, то ток утечки мал и хранение информации обеспечивается в течение длительного промежутка времени (десятки лет). При подаче напряжения на основной затвор происходит рассасывание заряда за счет туннельного эффекта, т. е. стирание информации. Приведем некоторые характеристики ПЗУ (табл. 3.1). Таблица 3.1  Промышленность выпускает большое количество микросхем ПЗУ. Приведем в качестве примера две микросхемы ПЗУ (рис. 3.78). На схемах использованы следующие обозначения: Ai — адресные входы; Di — информационные выходы; CS — выбор микросхемы; СЕ — разрешение выхода. Микросхема К573РФ5 — это репрограммируемое ПЗУ (РПЗУ) с ультрафиолетовым стиранием, имеющее структуру 2Кх8. По входу и выходу эта микросхема совместима с ТТЛ-структурами. Микросхема К556РТ5 — это одно-  кратно программируемая ПЗУ, выполнена на основе ТТЛШ-структур, по входу и выходу совместима с ТТЛ-структурами, имеющая структуру 512 бит х 8. |