Щербаков а. Н., Проскурін м. П., Грушко с. С. Прикладна теорія цифрових автоматів

Скачать 2.54 Mb. Скачать 2.54 Mb.

|

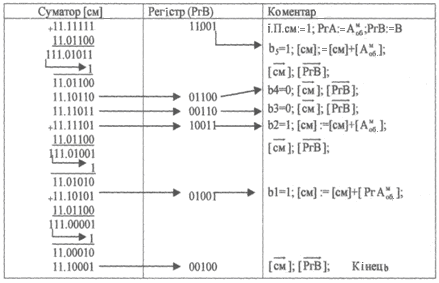

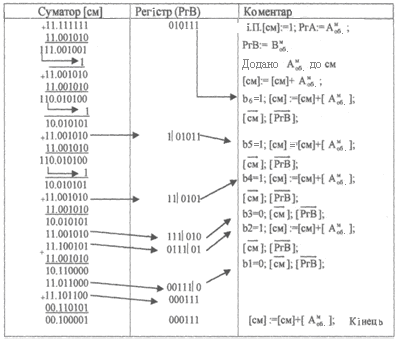

13 МНОЖЕННЯ ЧИСЕЛ НА ДСОК13.1 Множення чисел на ДСОК при позитивному множникуЗа аналогією із ДСДК, при множенні операндів заданих у оберненому модифікованому коді, розглянемо два випадки: В>0 і В<0. Випадок В0. Добуток обернених кодів співмножників дорівнює оберненому коду результату тільки у випадку позитивного множника. Доказ. Нехай множене А=Аоб., а множник В>0. Тоді: АВ=Аоб0,b1b2...bn = Аобb12-1+Аобb22-2+...+Аобbn2-n. У правій частині виходить обернений код результату тому що В=Воб. Це означає, що множник В позитивний. Алгоритм. Множення на ДСОК (при В>0) виконується в наступній послідовност (наведена в таблиці 13.2): - у суматор записуються 11.111...1 (машинний нуль оберненого коду); - у регістр В записується множник у прямому коді. Ведеться аналіз розрядів РгВ (починаючи з молодшого), і якщо там "1", то до вмісту суматора додається обернений код множеного. Якщо там 0, то до суматора нічого не додається; - після циклу додавання і аналізу, виробляється зсув вправо вмісту суматора і РгВ на один розряд (можна з переносом молодших розрядів суматора в старші розряди РгВ); - якщо знак результату негативний, то він у оберненому коді і необхідне перетворення в прямий код; -після перетворення в прямий код, перевіряємо нормалізацію результату. Приклад. Помножити на ДСОК числа: А = 0/10011; В = 0/11001. Запишемо числа в машинному зображенні: Амоб=11/01100; Вмоб=00/11001. Таблиця 13.1 Множення на ДСОК при позитивному множнику В0  Відповідь Смоб=11/1000100100; Спр= 111011011. 13.2 Множення чисел на ДСОК при негативному множникуВипадок В0. Якщо множник негативний, то добуток чисел на суматорі ДСОК є додатком виправленя А і [A]об2-n до отриманого добутку обернених кодів співмножників. Доказ. Нехай А=[A]об і В<0, тоді Алгоритм. Множення на ДСОК (при В0) виконується в наступній послідовності (наведена в таблиці 13.2): - у суматор записуються 11.111...1 (машинний нуль оберненого коду); - у регістр В записується множник у оберненому коді (без знака); - у суматор додається множене у оберненому коді Аоб; - ведеться аналіз розрядів РгВ (починаючи з молодшого), і якщо там «1» («0»), то до вмісту суматора додається (нічого не додається) обернений код множеного; - після циклу додавання і аналізу робиться зсув вправо вмісту суматора і РгВ на один розряд (можна з переносом молодших розрядів суматора в старші розряди РгВ); - після аналізу і зсуву старшого розряду множника до результату додають виправлення [ - якщо знак результату негативний, то він у оберненому коді і необхідне перетворення у прямий код; - після перетворення в прямий код, необхідно перевірити нормалізацію результату. Приклад. Метод 2, множення чисел на ДСОК. А=0/110101; В=0/101000; АВ=+2120. Рішення: Запишемо машинне зображення чисел. Амоб = 11/001010; Вмоб = 11/010111; Послідовність виконання операції множення наведена в таблиці 13.2. З урахуванням розрядів РгВ будемо мати 100\100001000111. Переповнення «1» із знакового розряду Sg1 додається до молодшого розряду числа. Тоді, одержимо відповідь: Спр=00\100001001000=2120(10). Існує ряд методів множення заснованих на роздільному під-сумковуванні груп часткових доданків з наступним об’єднанням сум з урахуванням переносів. Роздільна обробка проміжних сум і переносів вимагає так званого "дерева суматорів" (використано в IBM-360). Таблиця 13.2 Множення на ДСОК при негативному множнику  Існують також прискорені методи множення, засновані на використанні матриць проміжних результатів. Розглянемо схему множення: A = a5, a4, а3, а2, a1 *B = b5, b4, b3, b2, b1 a5b1 а4b1 а3b1 а2b1 а1b1 +......................................... а5b5 а4b5 а3b5 а2b5 а1b5 С10 С9.......................С2 С1 Цю схему можна представити також у вигляді матриці таблиці 13.3. Кожний елемент цієї матриці дорівнює "0" або "1". Таблиця 13.3 Матричне множення чисел  Добуток двох чисел можна одержати, якщо підсумувати елементи матриці в діагональному порядку. Cкладати доводиться тільки 0 або 1, тому операцію додавання можна виконувати за допомогою напівсуматорів і суматорів на один двійковий розряд.  Рисунок 13.1 Структурна схема пристрою множення для реалізації матричного алгоритму Рисунок 13.1 Структурна схема пристрою множення для реалізації матричного алгоритму Рисунок 13.2 Схема множного пристрою за алгоритмом Дадда Найбільше поширення одержали алгоритми Дадда, Уоллеса (матричний) і алгоритм збереження переносів [1-21]. На рис. 13.1 представлена структурна схема матричного пристрою множення для реалізації матричного алгоритму. Алгоритми відрізняються друг від друга групуванням часткових добут-ків, кількістю етапів перетворень. Для матричного алгоритму чотири етапи перетворення, для алгоритму Дадда – три етапи. Однак, матричні методи множення, незважаючи на більший об’єм устаткування, дають великий виграш часу, а використання ВІС значно знижує обмеження на устаткування. Розглянуті методи множення знайшли широке застосування в практиці бінарної арифметики. |