Курс лекций схемотенхника. Курс лекций схемотехника. Курс лекций по дисциплине Цифровая схемотехника для специальности

Скачать 0.83 Mb. Скачать 0.83 Mb.

|

|

Тема 1.7 Минимизация переключательных функций Совершенные нормальные формы С помощью эквивалентных преобразований логической функции можно получить различные формы ее представления. Одной из основных задач по преобразованию логических формул является получение равносильных формул в. так называемой, нормальной форме, и установления типа заданной формулы алгебры высказываний. Формула имеет нормальную форму, если в пси путем равносильных замен устранены операции эквиваленции, импликации, исключающей дизъюнкции, двойного отрицания, и при этом знаки отрицания находятся только при переменных. Таким образом, формула имеет нормальную форму, если она записана с помощью конъюнкции и дизъюнкции, действующих на совокупность переменных, и отрицания, действующего на отдельные переменные. Такие нормальные формулы называются дизъюнктивно-нормальную и конъюнктивно-нормальную формы. Они являются наиболее удобными для определения тождественной истинности и тождественной ложности формул. Для более корректного введения понятий дизъюнктивно-нормальную и конъюнктивно-нормальную формы, дадим определение основной конъюнкции и основной дизъюнкции. Основная (элементарная) конъюнкция - это конъюнкция основных высказываний или их отрицаний. Например,  Основная (элементарная) дизъюнкция - это дизъюнкция основных высказываний иди их отрицаний. Например,  . .Основная конъюнкция и дизъюнкция характеризуются рангом (порядком), который определяется количеством логических переменных в конъюнкции и дизъюнкции. С помощью основной конъюнкции и основной дизъюнкции можно определить дизъюнктивно-нормальную и конъюнктивно-нормальную формы. Конъюнктивно-нормальной формой (КНФ)данной формулы называется формула, равносильная данной, и представленная в виде конъюнкции основных дизъюнкций. Например,  . .Дизъюнктивно-нормальной формой (ДНФ)данной формулы называется формула, равносильная данной, и прсдставимая в виде дизъюнкций основных конъюнкций. Например, АВС+ ВС + С + АС. Алгоритм получения нормальной формы. Каждая логическая формула может быть представлена в форме КНФ или ДНФ. Не существует ДНФ только для логической константы 0, а также не существует КНФ для логической константы 1. Для получения дизъюнктивно-нормальной и конъюнктивно-нормальной форм используются законы инфолюции и де Моргана, а также первый и второй дистрибутивные законы. Для представления логической формулы в форме КНФ (ДНФ) необходимо: С помощью законов инфолюции представить формулу в базисе - {  } }С помощью законов де Моргана исключить отрицание над логическими операциями, а по закону двойного отрицания удалить двойные знаки отрицания. С помощью второго (первого) дистрибутивного закона удалить все суммы произведений (все произведения сумм) и произвести поглощение. Рассмотрим несколько примеров преобразования логических формул и получения их нормальных форм. Пример 1. Привести к конъюнктивно-нормальной форме логическую формулу.  Решение. В соответствии с предложенной методикой, получим эквивалентную ей формулу в базисе {  }. Для этого с помощью законов инфолюции исключим операцию эквиваленции, и используя закон двойного отрицания и закона де Моргана, получим }. Для этого с помощью законов инфолюции исключим операцию эквиваленции, и используя закон двойного отрицания и закона де Моргана, получим = = Пример 2. Привести к ДНФ логическую формулу:  Решение  = = Пример 3. Привести к нормальной форме и установить тип следующей формулы алгебры высказываний. F=  Решение Исключить операцию эквиваленнции Исключить операцию импликации Исключить общие отрицания и раскрыть скобки, выполнить преобразования. F=  = = Задачи F=  F=  F=  F=  F=(A  F=  F=AB  Тема 1.8 Логическое проектирование в базисах микросхем Для каждой логической операции существует свой логический элемент, выполненный в виде микросхемы той или иной серии. Таблица обозначений логических элементов

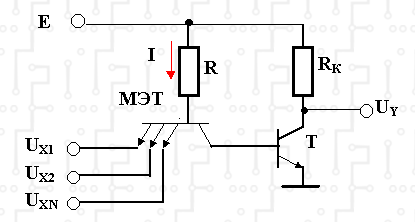

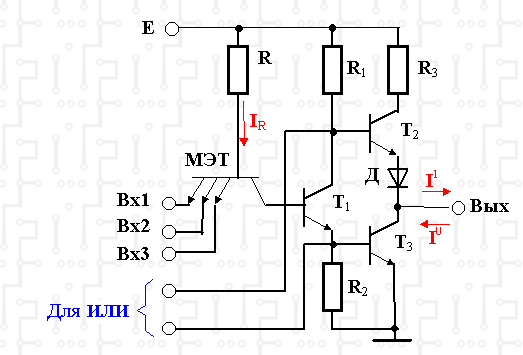

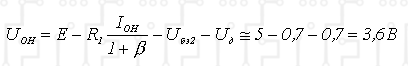

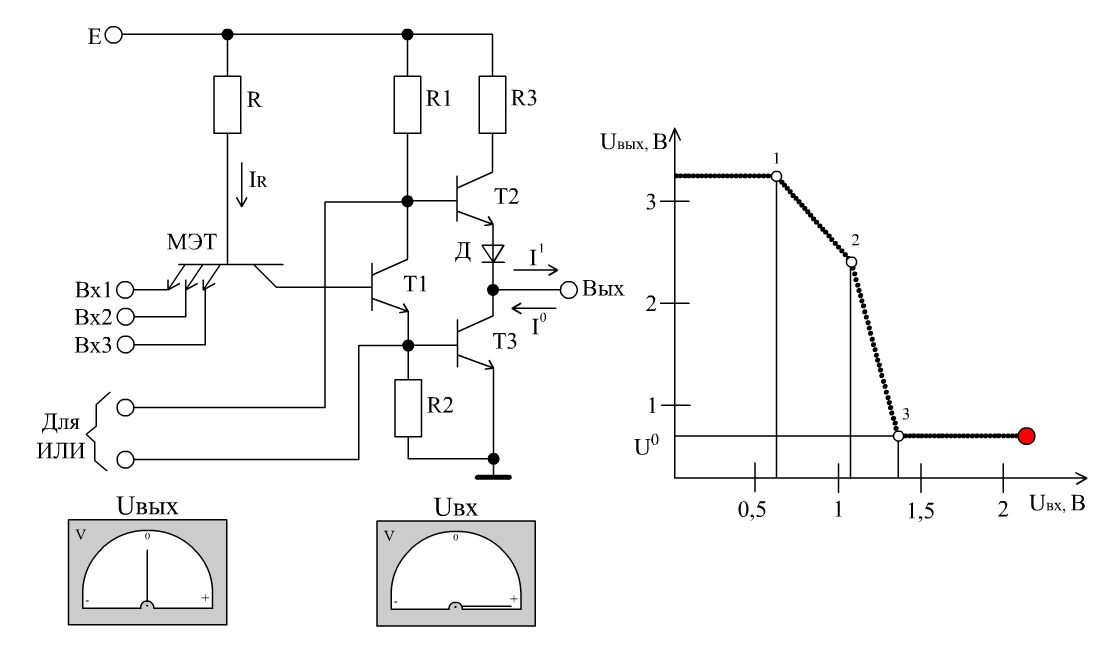

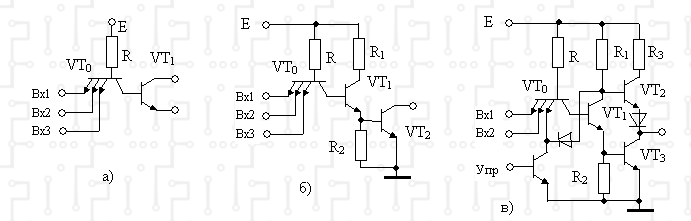

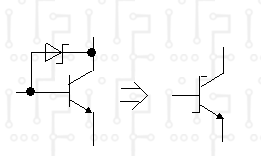

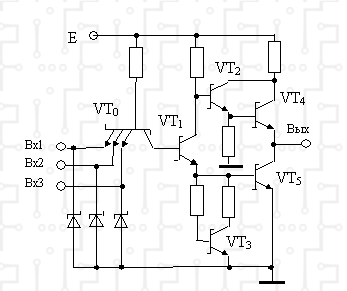

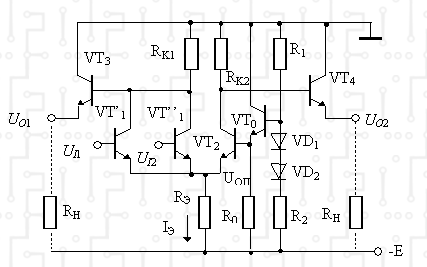

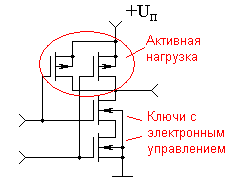

Тема 1.9 Цифровые интегральные микросхемы Логические соглашения Возможны два варианта представления логических переменных уровнями напряжения: 1) за 1 принимается более высокий уровень напряжения, обозначаемый H (high - высокий). Такой вариант называют соглашением положительной логики; 2) за 1 принимают низкий уровень напряжения - L (low - низкий). Этот вариант называется соглашением отрицательной логики. Логическое соглашение касается только представления логических переменных и не влияет на преобразование электрических сигналов в элементе. Описание элемента через соотношение между уровнями напряжения на его входах и выходе всегда однозначно и неизменно. Логические же операции могут изменяться в зависимости от способа представления переменных. Таким образом функция одного и того же элемента может быть разной. Совокупности микросхем, объединенные по признаку единства конструктивно-технологического исполнения, электрическим параметрам, условиям эксплуатации и логическому соглашению, образуют системы элементов. Микросхемы средней интеграции одной системы выпускаются в виде серий микросхем общего назначения. Самыми распространенными системами элементов являются системы ТТЛ, ЭСЛ, КМДП. Элементы транзисторно-транзисторной логики (ТТЛ) Схема простейшего элемента ТТЛ состоит из входной ступени на многоэмиттерном транзисторе VT1, которая реализует логическую функцию И, и выходной ступени VT2, реализующей функцию НЕ и обеспечивающей заданную нагрузочную способность (рис.1). Если на всех входах присутствует высокий уровень U1H , то многоэмиттерный транзистор оказывается в инверсном включении, так как его эмиттерный переход смещен в обратном направлении, а коллекторный - в прямом (эмиттер с коллектором как бы поменялись ролями). Эмиттерный ток при этом весьма мал, потому что в инверсном включении транзистора его коэффициент усиления  много меньше 1. много меньше 1. Рис 1. Простейший элемент ТТЛ Таким образом, ток базы выходного транзистора, близкий по значению к значению IR базы многоэмиттерного транзистора, насыщает этот транзистор и на выходе оказывается напряжение насыщения коллектор-эмиттер UкЭН, близкое к нулю (уровень логического «0»). Если же хотя бы на одном входе появится низкий уровень напряжения UП логического нуля, то многоэмиттерный транзистор с прямосмещенным эмиттерным переходом окажется в нормальном включении. В его коллекторе временно протекает ток, рассасывающий неосновные носители заряда из области базы выходного транзистора и быстро запирающий его. После запирания этого транзистора в коллекторе многоэмиттерного транзистора остается лишь малый обратный ток коллекторного перехода выходного транзистора. Поэтому многоэмиттерный транзистор оказывается в насыщении при нулевом коллекторном токе. Это обеспечивает надежное запирание выходного транзистора, поскольку к его базе через насыщенный многоэмиттерный транзистор поступает UП . На выходе в данном режиме формируется высокий уровень напряжения U0H , близкий к напряжению источника питания Е. Простейшей базовой схеме ТТЛ свойственны недостатки, по которым она не находит широкого применения: 1) низкий порог переключения и, следовательно, низкая помехозащищенность; 2) заметный входной ток при Ui =UiH, так как многоэмиттерный транзистор в инверсном включении имеет хотя и малый, но все же конечный коэффициент усиления  ; ;3) высокое выходное сопротивление U0H при на выходе, которое не может обеспечить хороших динамических свойств.  Рис 2. Элемент ТТЛ со сложным инвертором Ввиду этого практические схемы ТТЛ элементов в типовых сериях микросхем имеют более сложные структуры, из которых прежде всего следует назвать схему со сложным инвертором на выходе. Схема (рис.2) состоит из двух каскадов: многоэмиттерного транзистора VT0 , реализующего функцию И; сложного инвертора, состоящего из фазорасщепителя (VT1, R1, R2) и выходного двухтактного усилителя мощности (R3, VD, VT2, VT3). Количество входов у элемента ТТЛ обычно не превышает восьми, поскольку с увеличением их числа ухудшаются динамические параметры элемента. Выходное напряжение логической 1 формируется, когда VT1 закрыт, при этом  (второй член мал при большом ). В наихудших режимах UOH 2,4 В. Резистор R3 ограничивает сквозной ток в режиме переключения, а R2 обеспечивает надежное запирание VТ3. Выходное напряжение логического 0 формируется, когда на всех входах присутствует UIL, при этом VТ1 и VТ3 оказываются в насыщении, а VТ2 - закрывается. VТ3 способен принять значительный ток нагрузки IOL, оставаясь в насыщенном режиме. Поэтому, в зависимости от нагрузки UOL = Uкэн = (0,05...0,4) В. Роль диода VD заключается в том, чтобы надежно закрыть верхний выходной транзистор при формировании UOL.  Рис 3. Передаточная характеристика элемента ТТЛ со сложным инвертором. Переход схемы из состояния 1 в состояние 0 проследим по передаточной характеристике, форма которой показана на рис.3. При увеличении UI от UIL напряжение на базе многоэмиттерного транзистора также увеличивается, при этом ток IR перераспределяется: уменьшается в эмиттере и увеличивается в коллекторе. Так как VТ1 закрыт и его ток коллектора близок к нулю, то потенциал базы VТ1 следит за UI. При UI 0,7 В транзистор VТ1 начинает открываться и переходит в активную область (точка 1). Так как транзистор VТ3 закрыт (его Rвх велико), а VТ2 находится в активном режиме (его Iб мал), то VТ1 работает как усилитель с коэффициентом передачи: -R1/R2 -1,6. Этот коэффициент определяет крутизну наклона характеристики от точки 1 к точке 2. В точке 2 при UI 1,4 В начинает открываться транзистор VТ3. При этом малое динамическое сопротивление перехода база-эмиттер VТ3 шунтирует R2 и коэффициент усиления каскада наVТ1 резко возрастает. Здесь мы имеем положительную обратную связь, когда, чем больше открывается VТ3, тем больше становится коэффициент усиления. Поэтому участок от точки 2 до точки 3 почти вертикален. В точке 3 транзистор VТ3 (и VТ1) переходит в насыщение, и дальнейшее уменьшение UO становится малозаметным. Необходимо заметить, что вблизи точки 3 наблюдается момент, когда открыты все транзисторы. Поэтому при переключении ТТЛ - элемента наблюдается резкий скачок тока потребления. Статические параметры элемента в диапазоне температур от -10 до 70С: UOL 0,4 В; UOH 2,4 В; IIH 40 мкА; IIL -1,6 мА; помехоустойчивость 0,4 В. Рассмотрим некоторые распространенные модификации элементов ТТЛ (рис.4). Расширитель по ИЛИ (схема а) коллектором и эмиттером своего выходного транзистора VT1’ присоединяется к базовой схеме и этот транзистор оказывается подключенным параллельно транзистору VТ1 (рис.2). В результате базовый элемент И-НЕ превращается в элемент И-ИЛИ-НЕ. Выходной каскад элемента с «открытым коллектором» (схема б) не имеет коллекторной нагрузки, поэтому его можно объединять по выходу с аналогичными элементами. Подобные элементы используются для подключения устройств к общим информационным шинам и реализации функции «монтажное ИЛИ».  Рис.4. Модификации элементов ТТЛ В качестве буфера при подключении к общей шине применяются также элементы с тремя состояниями выхода (рис.4в). Третье состояние высокого выходного сопротивления обеспечивается в элементе при поступлении высокого уровня логической 1 на вход управления. При этом одновременно закрываются верхний и нижний транзисторы в выходном каскаде элемента, что равносильно его отключению от выхода. Для получения функции И без инверсии перед выходным каскадом в элементе включают дополнительный инвертирующий транзисторный ключ. Наибольшим быстродействием среди схем ТТЛ обладают элементы на транзисторах Шоттки (ТТЛШ). В них параллельно коллекторному переходу транзистора подключен так называемый диод Шоттки. Диод Шоттки в интегральном исполнении представляет собой контакт металла с высокоомным полупроводником коллекторной области транзистора. Падение напряжения на таком диоде в прямом включении не превышает 0,4 В, что меньше падения напряжения на обычном кремниевом p-n переходе. Если диод Шоттки включить параллельно переходу база-коллектор биполярного кремниевого транзистора, то это будет предотвращать его насыщение (переход база-коллектор не открывается). В интегральном исполнении транзистор и диод составляют единую структуру- транзистор Шоттки. В элементе ТТЛШ (рис.5) многоэмиттерный транзистор тоже выполняется по технологии Шоттки для того, чтобы еще уменьшить u, что сокращает входные токи при высоком уровне входного напряжения. Диоды Шоттки на входах служат для гашения паразитных колебаний и устранения отрицательного выброса напряжения на входе при переходе входного напряжения к низкому уровню.   Рис.5 Элемент ТТЛШ Напряжение логического нуля UOL у элемента ТТЛШ несколько выше (до 0,5 В), так как выходной транзистор работает без насыщения. Эмиттерно-связанная логика (ЭСЛ) Элементы ЭСЛ являются наиболее быстродействующими из элементов, которые изготавливаются на основе кремния. Поэтому они получили широкое распространение. Высокое быстродействие обеспечивается благодаря: активному режиму работы транзисторов в обоих логических состояниях, благодаря чему устраняется этап рассасывания зарядов из области базы при запирании транзисторов; малому логическому перепаду, благодаря чему уменьшается время заряда/разряда собственных емкостей схемы; использованию эмиттерных повторителей на выходах для быстрого перезаряда емкости нагрузки. В схеме ЭСЛ (рис.6) можно выделить следующие составные части:  Рис.6. Схема элемента ЭСЛ переключатель тока на дифференциальной паре транзисторов VT1 и VT2 с общим генератором эмиттерного тока (-Е, Rэ); источник опорного напряжения Uоп на транзисторе VT0, включающий также делитель напряжения R1, R2, VD1, VD2 и эмиттерный резистор R0; выходные повторители напряжения на транзисторах VТ3, VТ4, Кроме уменьшения выходного сопротивления повторители служат также для сдвига уровней напряжения, что необходимо для согласования элементов по входам/выходам. Источник опорного напряжения вырабатывает напряжение Uоп, равное порогу переключения элемента, который выбирается средним между напряжениями логической 1 и логического 0. В этот источник входит также делитель напряжения, где диоды VD1 и VD2 служат для температурной компенсации падений напряжения на эмиттерных переходахVТ0 и VТ1. Эмиттерные повторители (VТ3, VТ4) служат для усиления сигналов по мощности и смещения коллекторных потенциалов VТ1 и VТ2 с целью согласования входных и выходных логических уровней. Наличие повторителей облегчает работу элемента на линию связи и обеспечивает возможность образования монтажного ИЛИ путем объединения элементов по выходам. Эмиттерные резисторы повторителей (Rн) являются внешними элементами схемы, что позволяет уменьшить рассеиваемую ее корпусом мощность. Логика на комплементарных МОП транзисторах (КМДП) Микросхемы на комплементарных транзисторах строятся на основе МОП транзисторов с n- и p-каналами. Один и тот же потенциал открывает транзистор с n-каналом и закрывает транзистор с p-каналом. При формировании логической единицы открыт верхний транзистор, а нижний закрыт. В результате ток через микросхему не протекает. При формировании логического нуля открыт нижний транзистор, а верхний закрыт. И в этом случае ток через микросхему не протекает. Простейший логический элемент - это инвертор. Его схема приведена на рисунке 7. Рисунок 7. Принципиальная схема инвертора, выполненного на комплементарных МОП транзисторах На этой схеме для упрощения понимания принципов работы микросхемы не показаны защитные и паразитные диоды. Особенностью микросхем на комплементарных МОП транзисторах является то, что в этих микросхемах в статическом режиме ток практически не потребляется. Потребление тока происходит только в момент переключения микросхемы из единичного состояния в нулевое и наоборот. Этим током производится перезаряд паразитной ёмкости нагрузки. Схема логического элемента "И-НЕ" на КМОП микросхемах практически совпадает с упрощенной схемой "И" на ключах с электронным управлением, которую мы рассматривали ранее. Отличие заключается в том, что нагрузка подключается не к общему проводу схемы, а к источнику питания. Принципиальная схема элемента "2И-НЕ", выполненного на комплементарных МОП транзисторах приведена на рисунке 8.  Рисунок 8. Принципиальная схема элемента "2И-НЕ", выполненного на комплементарных МОП транзисторах В этой схеме можно было бы применить в верхнем плече обыкновенный резистор, однако при формировании низкого уровня схема постоянно потребляла бы ток. Вместо этого, в качестве нагрузки используются p-МОП транзисторы. Эти транзисторы образуют активную нагрузку. Если на выходе требуется сформировать высокий потенциал, то транзисторы открываются, а если низкий - то закрываются. В приведённой на рисунке 2 схеме ток от источника питания на выход микросхемы будет поступать через один из транзисторов, если хотя бы на одном из входов (или на обоих сразу) будет присутствовать низкий потенциал (уровень логического нуля). Если же на обоих входах будет присутствовать уровень логической единицы, то оба p-МОП транзистора будут закрыты и на выходе микросхемы сформируется низкий потенциал. В этой схеме, так же как и в схеме на рисунке 1, если транзисторы верхнего плеча будут открыты, то транзисторы нижнего плеча будут закрыты, поэтому в статическом состоянии ток микросхемой от источника питания потребляться не будет. | |||||||||||||||