Последний вариант цифровой электроники. Последний вариант цифровой электроники (1). Тема Математическое введение в цифровую технику. 11

Скачать 2.28 Mb. Скачать 2.28 Mb.

|

|

Глава 9. Цифровые устройства последовательностного типа. 9.1. Триггеры. Цифровое устройство называется последовательностным (ПЦУ), если его выходные сигналы зависят не только от значений входных сигналов в данный момент времени, но и от значений входных сигналов, поступивших в предшествующие моменты времени. Иными словами, ПЦУ должно отслеживать последовательность поступления входных сигналов для формирования результата на своем выходе. Отсюда очевиден термин «последовательностое». В структуре ПЦУ обычно имеется комбинационная схема, и всегда присутствуют элементы, способные удерживать (фиксировать) устойчивые состояния ПЦУ в отсутствии внешних воздействий. Такие элементы обладают как бы эффектом памяти. Поэтому говорят, что ПЦУ обладают памятью. Простейший бинарный элемент памяти может принимать одно из двух состояний – логическую единицу или логический нуль. Это состояние может сохраняться сколь угодно долго до тех пор, пока не будет заменено на новое. ПЦУ называются еще цифровыми автоматами, конечными автоматами или автоматами с памятью. ПЦУ является основой тактируемых устройств, функционирование которых можно разбить на некоторые стадии во времени, поочередно сменяющиеся друг за другом. Такой принцип работы характерен для большинства измерительных цифровых схем. Например, почти все методы аналого-цифрового преобразования требуют реализации последовательных во времени циклических стадий. Совокупность правил, определяющих последовательность переключения состояний и последовательность выходных сигналов в зависимости от последовательности входных сигналов, принято называть законом функционирования ПЦУ. Роль элемента памяти в ПЦУ выполняет триггер, способный фиксировать и хранить значение логического нуля или единицы. Триггер представляет собой устройство с двумя устойчивыми состояниями. Устойчивым называется состояние, в котором устройство в отсутствии внешних воздействий может прибывать сколько угодно долго. В общем случае триггер имеет два выхода: прямой Функциональная классификация является наиболее общей и представляет собой классификацию триггеров по виду логического уравнения, характеризующего состояния входов и выходов триггера в момент времени до его срабатывания tn и после tn+1. В соответствии с функциональной классификацией различают RS-, D-, T- и JK-триггеры. Классификация по способу записи информации характеризует временную диаграмму работы триггера, т.е. определяет ход процесса записи информации в триггер. По этой классификации триггеры подразделяются на асинхронные и тактируемые. Отличительной особенностью асинхронных триггеров является то, что запись информации в них осуществляется статическим способом, т.е. непосредственно с поступлением информационного сигнала на его вход. Запись информации в тактируемый триггер, имеющий информационные и тактовые входы, осуществляется только при подаче разрешающего или тактирующего импульса. Среди тактируемых триггеров различают триггеры, срабатывающие по уровню (в момент прихода тактирующего сигнала или, что одно и то же, по его переднему фронту), и триггеры с внутренней задержкой, срабатывающие после окончания тактирующего сигнала (по заднему фронту). Такое управление тактируемыми триггерами называется динамическим. Кроме того, тактируемые триггеры подразделяются на однотактные и многотактные в зависимости от числа тактирующих сигналов, необходимых для перевода триггера из одного состояния в другое. При проектировании устройств с применением триггеров, кроме значения функции, выполняемой триггером, необходимо знать его основные схемотехнические параметры. К таким параметрам относятся как стандартные параметры любой логической микросхемы – это нагрузочная способность, коэффициент объединения по входу, время задержки и т.д., так и индивидуальные: минимальная длительность входного сигнала, при которой еще происходит переключение триггера из одного состояния в другое; максимальная частота переключения триггера, определяющая минимально допустимый временной интервал между двумя последовательными сигналами минимальной длительности. Закон функционирования триггера, да и вообще ПЦУ, удобно отображать с помощью так называемых таблиц переходов, в которых даются состояния входов и выходов триггера в момент времени до его срабатывания tn и после tn+1. При этом выходное состояние может обозначаться следующим образом: 0 - триггер находится в состоянии Q=0; 1 - триггер находится в состоянии Q=1; Q - состояние триггера не изменяется при изменении информации на входе; Х - неопределенное состояние триггера, характеризующееся тем, что в процессе действия информационного сигнала на входе логические уровни выходов триггера одинаковы ( 9.1.1. RS-триггер. Триггером RS-типа называется логическое устройство с двумя устойчивыми состояниями, имеющее два информационных входа R и S (от англ. «reset» - сбросить и «set» - установить), такие, что при S=1 и R=0 триггер принимает единичное состояние, а при S=0, R=1 - нулевое. Принцип работы RS-триггера можно задать таблицей переходов (таблица 9.1), где Qn – исходное состояние триггера: Таблица 9.1.

Для того, чтобы найти логическое уравнение RS-триггера, преобразуем таблицу переходов к виду таблицы истинности (таблица 9.2), в которой состояние Qn определим конкретными значениями и представим его в виде входной переменной: Таблица 9.2.

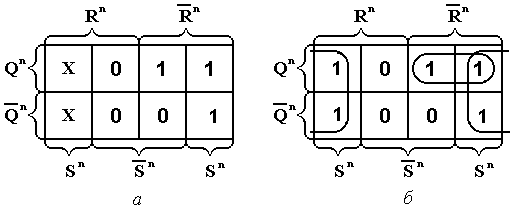

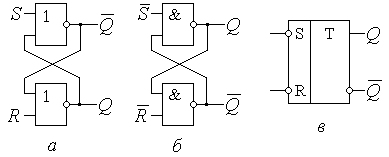

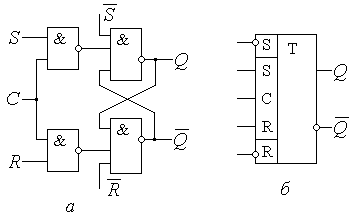

На основании данных таблицы заполним диаграмму Вейча, в которой отметим также неопределенные значения функции Qn+1 (рис. 9.1,а). Из диаграммы видно, что в результате склейки минтермов можно получить две простые импликанты  Рис. 9.1. Диаграмма Вейча для МДНФ асинхронного RS-триггера с неопределенными состояниями (а) и с доопределенными состояниями (б). Полученное уравнение задает работу асинхронного RS-триггера. Состояние такого триггера определяется только значениями сигналов R и S. Асинхронный RS-триггер можно построить на логических элементах И-НЕ, ИЛИ-НЕ. Для реализации триггера на элементах ИЛИ-НЕ выполним следующие преобразования, используя закон де Моргана и двойного отрицаня: Схема, реализующая полученную зависимость, представлена на рис.9.2,а. Для реализации RS-триггера на элементах И-НЕ, необходимо выполнить следующие преобразования: Схема асинхронного RS-триггера, соответствующая полученному уравнению, изображена на рис. 9.2,б. а условное графическое обозначение – на рис. 9.2,в. Из рисунка видно, что на вход триггера на элементах И-НЕ сигналы R и S необходимо подавать в инверсном виде.  Рис. 9.2. Схемы асинхронного RS-триггера на базе элементов ИЛИ-НЕ (а), И-НЕ (б) и его УГО с инверсными входами (в). В качестве самостоятельных устройств асинхронные RS-триггеры находят ограниченное применение, но являются базовыми схемами для более сложных триггерных устройств. В устройствах цифровой обработки находят применение тактируемые RS-триггеры, которые называются еще синхронными. Эти триггеры, кроме входов установки R и S, имеют еще вход разрешения записи C. Срабатывание синхронного триггера происходит только при наличии активного сигнала на этом входе. Работа синхронного RS-триггера задается таблицей переходов 9.3: Таблица 9.3.

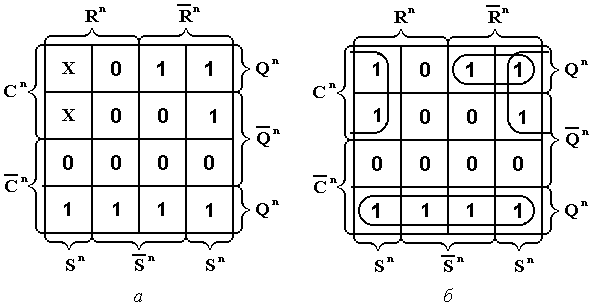

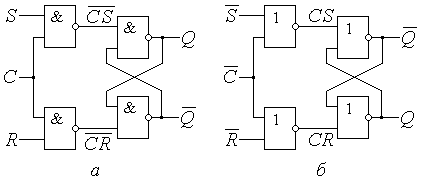

Из таблицы видно, что до тех пор, пока сигнал Cn имеет значение логического нуля, триггер сохраняет свое состояние неизменным. Как только Cn становится равным логической единице, работа синхронного триггера разрешается, и его состояния соответствуют состояниям асинхронного триггера. Алгоритм нахождения МДНФ синхронного RS-триггера аналогичен алгоритму нахождения МДНФ асинхронного RS-триггера. Приведем результат поиска этой МДНФ - диаграмму Вейча для таблицы 9.3 с неопределенными состояниями (рис. 9.3,а) и с доопределенными состояниями (рис. 9.3,б). Согласно диаграмме рис. 9.3,б запишем МДНФ и выполним следующее преобразование: Полученная ФАЛ содержит два слагаемых. Первое слагаемое представляет собой логическою конъюнкцию инверсного значения сигнала тактирования  Рис. 9.3. Диаграмма Вейча для МДНФ синхронного RS-триггера с неопределенными состояниями (а) и с доопределенными состояниями (б). Для реализации структурной схемы синхронного RS-триггера на элементах И-НЕ необходимо инверсные сигналы установки Аналогично для реализации структурной схемы синхронного RS-триггера на элементах ИЛИ-НЕ необходимо прямые сигналы установки S и сброса R асинхронного триггера стробировать сигналом разрешения C, т.е. получить комбинацию сигналов Из уравнений видно, что на вход схемы синхронного RS-триггера на элементах ИЛИ-НЕ все входные сигналы нужно подавать в инверсном виде. Схема такой реализации представлена на рис.9.4,б.  Рис. 9.4. Схема синхронного RS-триггера в базисе И-НЕ (а) и ИЛИ-НЕ (б). Часто синхронные триггеры любых типов имеют дополнительные входы асинхронной установки в ноль или единицу. Схема такого синхронного RS-триггера приведена на рис. 9.5,а, а его условное графическое обозначение на рис. 9.5,б. Поскольку триггер, изображенный на структурной схеме, реализован на элементах И-НЕ, то сигналы асинхронной установки R и S должны иметь инверсные активные уровни. Кроме того, поскольку сигналы асинхронной установки подаются непосредственно на выходной каскад (асинхронный RS-триггер), то они имеют больший приоритет перед остальными сигналами триггера.  Рис. 9.5. Схема синхронного RS-триггера с входами асинхронной установки (а) и его условное графическое обозначение (б). | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||