Последний вариант цифровой электроники. Последний вариант цифровой электроники (1). Тема Математическое введение в цифровую технику. 11

Скачать 2.28 Mb. Скачать 2.28 Mb.

|

|

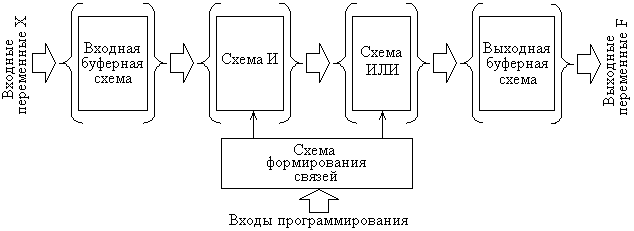

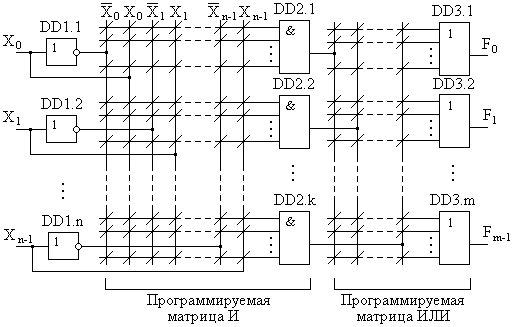

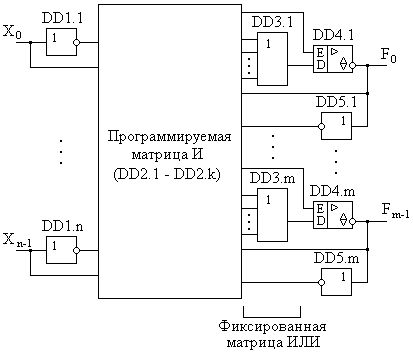

Глава 11. Программируемые логические интегральные схемы. 11.1. Принципы структурной организации программируемых логических интегральных схем. Из рассмотренного в главе 8 принципа синтеза КЦУ, а в последствии и ПЦУ, следует, что любая система ФАЛ этих устройств может быть задана в виде ДНФ, т.е. в виде универсальной структурной записи с конкретизацией в каждом случае отдельных минтермов. Из сказанного правомерно допустить возможность создания универсальной элементной базы, реализующей произвольную систему ФАЛ цифрового устройства путем задания определенных внутренних связей между стандартными базовыми логическими элементами И и ИЛИ. Причем целесообразным является исполнение подобных универсальных элементов в виде отдельных интегральных схем. Для задания внутренних связей между базовыми логическими элементами, позволяющих реализовывать необходимые ФАЛ, требуется осуществить предварительную настройку таких интегральных схем. Подобный процесс настройки носит название программирования. Поэтому, такие интегральные схемы получили название программируемых логических интегральных схем (ПЛИС). Обобщенная структурная схема ПЛИС приведена на рис. 11.1.  Рис. 11.1. Обобщенная структурная схема ПЛИС. Отличие структуры ПЛИС от других цифровых микросхем заключается в наличии настраиваемых программным путем в общем случае множества элементов И и ИЛИ, называемых соответственно матрицами И и ИЛИ. Настройка этих матриц на выполнение конкретной ФАЛ осуществляется путем подачи на микросхему ПЛИС специальных сигналов программирования, подобных сигналам программирования микросхем постоянной памяти ПЗУ (об организации, схемотехнической реализации и особенностях программирования полупроводниковых запоминающих устройств будет изложено в следующей главе). В результате реализуются внутренние связи в матрицах, структурно задающие соединения отдельных элементов И и ИЛИ в соответствие с описывающей работу цифрового устройства системе ФАЛ. Входные и выходные переменные подаются на ПЛИС и снимаются с нее через буферные схемы, которые, как правило, кроме состояния логического нуля или логической единицы, могут принимать пассивное Z-состояние. Первые ПЛИС в качестве программируемых содержали обычно обе матрицы - И и ИЛИ. Такие ПЛИС получили название программируемых логических матриц (ПЛМ), или в англоязычной аббревиатуре – PLA (Programmable Logic Array). Фрагмент структуры ПЛМ, отражающий только программируемые матрицы И и ИЛИ, представлен на рис. 11.2. Косой линией принято обозначать программируемую электрическую связь. Изображенные на рис. 11.2 программируемые матрицы обладают электрическим контактом во всех пересечениях. Наличие контактов во всех пересечениях в матрицах характерно для новых, незапрограммированных ПЛИС. Также как и в случае с ПЗУ, программирование ПЛИС осуществляется разрушением электрического контакта в необходимых пересечениях, выполненного в виде плавкой перемычки или транзисторной МДП-структуры (см. следующую главу). В зависимости от технической реализации этого контакта ПЛИС бывают прожигаемые и перепрограммируемые.  Рис. 11.2. Фрагмент структурной схемы ПЛМ. Поскольку конституенты единицы ФАЛ в виде ДНФ образуются как прямыми значениями входных переменных, так и инверсными, то и в структуре ПЛИС предусмотрено наличие входных инверторов DD1. Прямые и инверсные значения всех n входных переменных образуют столбцы программируемой матрицы И. Строки этой матрицы образуются n-входовыми элементами И DD2. В общем случае, если предположить, что выходная функция F на всех наборах входных переменных принимает единичные значения, то таких элементов И по числу конституент единицы должно быть k=2n. Синтез какой-либо схемы для такого случая является нецелесообразным, поскольку функция с единичными значениями на всех наборах является константой единицы и от входных переменных не зависит. В практических случаях выходная функция принимает единичные значения только на определенных наборах, а часто и вовсе является частично определенной. Поэтому ПЛИС содержат обычно количество k элементов И меньшее, чем 2n. Выходы этих элементов образуют k столбцов программируемой матрицы ИЛИ, а их выходные значения соответствуют конституентам единицы функции F. Для возможности реализации системы ФАЛ из нескольких различных выходных функций, матрица ИЛИ содержит m k-входовых элементов ИЛИ DD3. Каждый из этих элементов объединяет логическим сложением те конституенты единицы, которые входят в состав ДНФ реализуемой выходной функции F. Недостатком структуры ПЛМ является слабое использование ресурсов программируемой матрицы ИЛИ. Поэтому была предложена более простая, но тем не менее, более эффективная архитектура программируемой матричной логики (ПМЛ). В английской терминологии ее обозначение записывается как Programmable Array Logic (PAL). Суть этой архитектуры заключается в использовании в качестве программируемой только матрицы И. Матрица ИЛИ является фиксированной. Пример упрощенной структуры ПМЛ представлен на рис. 11.3. На рисунке не раскрывается структура программируемой матрицы И по причине ее аналогии с рассмотренной матрицей И в структуре ПЛМ. Входные переменные, также как и в ПЛМ, в ПМЛ подаются в прямом и инверсном виде. Из рисунка видно, что входы элементов ИЛИ DD3 являются не коммутируемыми. Таким образом, на каждый вход текущего элемента ИЛИ подается технологически определенный выход элемента И программируемой матрицы И. Кроме элементов ИЛИ, в изображенной на рисунке структуре ПМЛ содержатся буферные элементы DD4, позволяющие управляющим сигналом на входах E этих элементов, переводить соответствующие выходы F ПЛИС в высокоимедансное состояние. В этом случае эти выходы могут выполнять функции входов программируемой матрицы И. С этой целью выходы буферных элементов DD4 соединены с матрицей И напрямую и через инверторы DD5, т.е. организованы обратные связи. Если выход текущего элемента DD4 находится в активном состоянии, то через цепи обратной связи значение выходной функции F подается обратно в матрицу И. Это позволяет реализовывать схемы не только КЦУ, но и ПЦУ. Элементы DD3 и DD4 ПМЛ образуют так называемую макроячейку.  Рис. 11.3. Структурная схема ПМЛ. Приведенная на рис. 11.3. структура характерна для классических ПМЛ. В настоящее время большее распространение получили интегральные схемы универсальной ПМЛ, принципиально отличающейся от классической только структурой макроячеек. Макроячейка универсальной ПМЛ содержит элемент Исключающее ИЛИ, один вход которого программно связан с нулевым потенциалом общего провода. Нарушение этой связи позволяет инвертировать значения выходных функций F, меняя, таким образом, логические уровни выходных сигналов. Кроме того, макроячейки универсальной ПМЛ содержат обычно D-триггеры-защелки, позволяющие синхронизировать выдачу информации на выходы и предоставляющие более широкие возможности при реализации ПЦУ. Другим представителем ПЛИС, интенсивно развивающимся в настоящее время, особенно за рубежом, является комплексная ПЛИС. В английской терминологии она обозначается как CPLD (Complex Programmable Logic Devices). Такие ПЛИС содержат несколько логических блоков, каждый из которых представляет универсальную ПМЛ. Входы и выходы всех логических блоков объединяются в единую структуру программируемой коммутационной матрицей. 11.2. Особенности проектирования цифровых устройств на базе ПЛИС. Процесс проектирования и изготовления цифровых устройств традиционным способом, т.е. на основе стандартных интегральных схем комбинационного и последовательностного типов малой и средней степени интеграции, является узкоспециализированным. Это означает, что специалисты, участвующие в процессе создания устройств цифровой техники, выполняют определенные индивидуальные функции в этом процессе. Сам процесс создания состоит из проектных стадий, стадий подготовки производства, отработки технологии и пр. Аналогичной сложностью характеризуется и процесс создания цифровых устройств на основе специализированных интегральных схем высокой степени интеграции. Использование же ПЛИС позволяет существенно сократить объем этих стадий, фактически свести их только к этапам проектирования с помощью ЭВМ. Существенным преимуществом ПЛИС является их универсальность и возможность быстрого программирования под выполнение функций практически любого цифрового устройства. ПЛИС представляет собой полуфабрикат, на основе которого разработчик, обладающий персональным компьютером, несложными и относительно недорогими аппаратными средствами программирования и специальным программным обеспечением, называемым системой автоматизированного проектирования (САПР), имеет возможность проектирования цифрового устройства в рекордно короткие сроки. При этом весь цикл проектирования и программирования доступен всего одному человеку – проектировщику цифровых устройств на базе ПЛИС. Все современные САПР ПЛИС работают под управлением операционных систем семейства Windows и используют все преимущества ее графического интерфейса. Фирмы-производители интегральных схем ПЛИС осуществляют обычно поддержку своей продукции путем разработки и распространения таких САПР. Проектирование устройств на основе ПЛИС в системе САПР предполагает выполнение следующих этапов: разработка структурной формулы проектируемого цифрового устройства, ее минимизация и адаптация под тип и возможности используемой ПЛИС (для этих целей используются методы, рассмотренные в предыдущих главах); создание нового файла проекта, назначение семейства ПЛИС для проекта; ввод структурной формулы или схемы проектируемого устройства с помощью специальных программ – редакторов; компиляция введенной структурной формулы или схемы, т.е. получение битовой последовательности загружаемой в ПЛИС программы; временной анализ задержек в отдельных элементах и проверка работоспособности всей структуры цифрового устройства путем моделирования с помощью специальных программ – симуляторов; программирование микросхемы ПЛИС с помощью специальных аппаратных средств – программаторов. Проектировщику в системе САПР доступны обычно обширные программные библиотеки, задающие функции типовых интегральных схем ТТЛ и КМОП типов. Это позволяет синтезировать схему цифрового устройства не только в определенном базисе, т.е. из элементарных функций И, ИЛИ, НЕ, но и используя готовый программный аналог существующих реальных микросхем. Широкие возможности при проектировании представляет глобальная сеть Internet, через которую осуществляется распространение специально разрабатываемых библиотек компонентов, не имеющихся в стандартных версиях САПР. Для задания схемы проектируемого на базе ПЛИС цифрового устройства широко используются языки описания аппаратных средств, в общем случае называемые HDL (hardware device language). С помощью операторов такого языка можно задать типы комбинационных или последовательностных устройств, сформулировать входные воздействия на них и связи между ними, определить константы и переменные в проекте и т.д. Среди лидеров в производстве ПЛИС и САПР для них на сегодняшний день можно выделить такие фирмы, как Altera Corporation, Xilinx и Actel Corporation. На их долю приходится до 80 % от общего производства ПЛИС, быстродействие которых на сегодняшний день достигло порядка сотен МГц, емкость программируемых матриц И – нескольких миллионов элементов, а стоимость снизилась до десятков у.е. Все это, плюс кратчайшие сроки проектирования, высокая надежность, объясняемая высокой степенью интеграции отдельных элементов в едином кристалле полупроводника и, как следствие, минимальное количество внешних межсоединений, делает ПЛИС предпочтительной элементной базой по сравнению со стандартными логическими микросхемами комбинационного и последовательностного типов. Контрольные вопросы Опишите обобщенную структурную схему ПЛИС и поясните свойство их универсальности. Как реализуется принцип программной коммутации логических элементов в ПЛМ? Почему структура ПМЛ оказалась более перспективной по сравнению со структурой ПЛМ? Охарактеризуйте ПЛИС CPLD. Перечислите основные этапы проектирования цифровых устройств на базе ПЛИС. Перечислите основные преимущества использования ПЛИС по сравнению с микросхемами базовых логических элементов. |