Последний вариант цифровой электроники. Последний вариант цифровой электроники (1). Тема Математическое введение в цифровую технику. 11

Скачать 2.28 Mb. Скачать 2.28 Mb.

|

|

9.1.2. D-триггер. D-триггер представляет собой синхронный запоминающий бинарный элемент с одним информационным входом D и входом синхронизации C. D-триггер осуществляет запись информационного разряда по активному уровню сигнала C с последующим его хранением. Отсюда D-триггер имеет другие названия: триггер-защелка (data-триггер) и триггер задержки (delay-триггер), что объясняет происхождение символа «D» в его названии. Работа D-триггера задается таблицей переходов 9.4: Таблица 9.4.

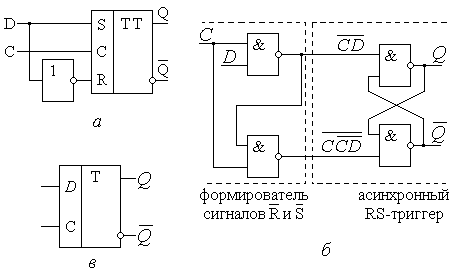

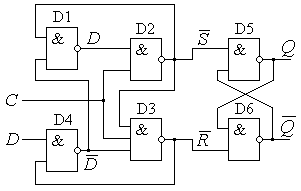

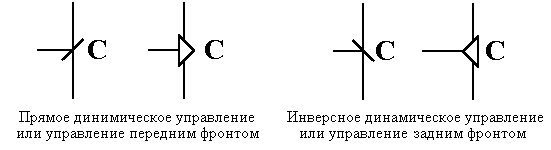

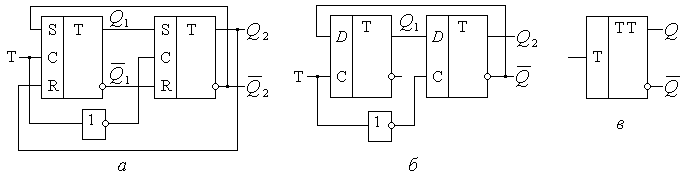

Проделав операции, как и в случае с RS-триггером, можно составить логическое уравнение D-триггера, соответствующее приведенной таблице переходов: Если RS-триггер относится к классу парафазных триггеров (для установки его в ноль или единицу необходимо подавать на входы R и S сигналы с противоположными значениями), то D-триггер является однофазным триггером. Из этого следует, что D-триггер можно реализовать на базе синхронного RS-триггера, задействовав вход S как вход D, а на вход R подав сигнал D через инвертор (рис.9.6,а). Можно реализовать D-триггер на базе RS-триггера и без дополнительного инвертора, несколько изменив связи в его внутренней структуре. Для этого выполним следующие преобразования над логическим уравнением D-триггера: Полученное уравнение совпадает по своей структуре с уравнением для асинхронного RS-триггера, при условии, что С учетом полученных выражений, схема D-триггера может быть представлена совокупностью двух каскадов (рис. 9.6,б). Первый выполняет функцию формирование сигналов  Рис. 9.6. Схема D-триггера на основе синхронного RS-триггера с внешним инвертором (а), на основе структуры RS-триггера без внешнего инвертора (б), условное графическое обозначение D-триггера (в). Рассмотренные ранее способы подачи входных сигналов характеризуются тем, что их активными уровнями являются статические состояния, т.е. сами уровни напряжения логического нуля или логической единицы. Такая форма управления цифровым устройством называется статической. Для тактируемых устройств эта форма управления в большинстве случаев является неудобной, поскольку в течение всего времени действия импульса сигнала синхронизации, устройство будет реагировать на любые изменения входных информационных сигналов. Таким образом, необходимо, чтобы информационные сигналы оставались неизменными на протяжении действия импульса синхронизации. Это значительно усложняет схему устройства, а в некоторых случаях и вовсе является не решаемой задачей, поскольку информационные сигналы могут носить характер последовательностей импульсов со случайным характером. Для устранения указанного недостатка используется принцип динамического управления. Согласно этому принципу, активным считается не статический уровень напряжения логической единицы или логического нуля, а процесс перехода из одного уровня в другой. Этот процесс представляет собой передний или задний фронт тактирующего импульса и, следовательно, характеризуется малым временным промежутком. Поэтому задача синхронизации значительно упрощается и представляет собой фиксацию входных информационных сигналов в строго определенный момент подачи или снятия импульса синхронизации. На рис. 9.7 на примере D-триггера показана организация динамического управления входом записи C по схеме трех триггеров.  Рис. 9.7. Схема D-триггера с динамическим управлением. Хранение информации в схеме на рис.9.7 осуществяет каскадом асинхронного RS-триггера на вентилях И-НЕ D5 и D6, имеющего инверсные входы установки и сброса. Два других каскада триггеров на вентилях D1, D2, D3 и D4 реализуют механизм динамического управления и коммутации информационного сигнала D и сигнала записи (синхронизации) C. Элемент D4 формирует инверсное значение сигнала  Рис. 9.8. Обозначения входов с динамическим управлением на УГО элементов. 9.1.3. T-триггер. Асинхронный триггер T-типа является одновходовым устройством с двумя устойчивыми состояниями, изменяющимися каждый раз на противоположные при подаче на вход Т управляющего сигнала. Работа асинхронного Т-триггера задается таблицей переходов 9.5: Таблица 9.5.

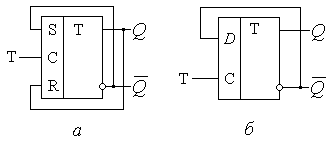

Составленное по таблице переходов СДНФ для Qn+1 уже имеет минимальный вид: Характерной особенностью T-триггера является то, что частота изменения потенциала на его выходах в два раза меньше частоты сигналов на входе T (рис. 9.9). Это свойство используется при построении двоичных счетчиков. Отсюда второе название T-триггера – счетный триггер. Вход Т принято называть счетным. Рис. 9.9. Диаграммы входного и выходного потенциалов T-триггера. Структуру асинхронного T-триггера можно определить путем преобразования его логической функции к удобному виду для синтеза в заданном базисе. Однако, из анализа работы асинхронного RS-триггера очевидно, что в том случае, если он находился в единичном состоянии (  Рис.9.10. Схема одноступенчатого асинхронного T-триггера на основе RS-триггера (а) и D-триггера (б) Т-триггер можно построить и на базе D-триггера. Если в логическом уравнении синхронного D-триггера принять Полученное выражение является ни чем иным, как логическим уравнением T-триггера при условии, что функцию входа T выполняет вход разрешения C D-триггера. При этом, на вход D необходимо подавать сигнал с инверсного выхода Рассмотренные на рис.9.10 структуры Т-триггера являются практически неработоспособными. Действительно, в течение всего времени, пока на входе T присутствует активный уровень сигнала, будет происходить непрерывная смена его состояний на противоположные с частотой, равной обратной величине удвоенного времени срабатывания триггера. В результате возникнет автоколебательный процесс. Триггер будет постоянно перебрасывать сам себя в период действия активно сигнала на входе T. Причина этого явления объясняется тем, что Т-триггер, обладая обратными связями, принимает информацию как из внешней среды, так и со своих собственных выходов. Поэтому для устойчивой работы Т-триггера необходимо разделить во времени функции приема тактирующего сигнала Т и фиксации на входах R, S или D сигналов с соответствующих выходов Q и  Рис. 9.11. Двухступенчатый T-триггер на базе синхронных RS-триггеров (а), D-триггеров (б) и его условное графическое обозначение (в). 9.1.4. JK-триггер. JK-триггер относится к двухвходовым устройствам и функционирует по правилам, похожим на правила функционирования RS-триггера. Отличие состоит в том, что в JK-триггере все состояния являются определенными. Можно провести аналогию входов JK- и RS-триггеров: вход K (от англ. «kill» – убить) JK-триггера выполняет функцию входа сброса R RS-триггера, а вход J (от англ. «jump» – прыгнуть) JK-триггера – функцию входа установки S RS-триггера. При этом, если в RS-триггере комбинация единичных значений входов R и S является запрещенной, то в случае аналогичной комбинации входов J и K, JK-триггер меняет свое состояние на противоположное. Правило работы синхронного JK-триггера можно сформулировать таблицей переходов 9.6: Таблица 9.6.

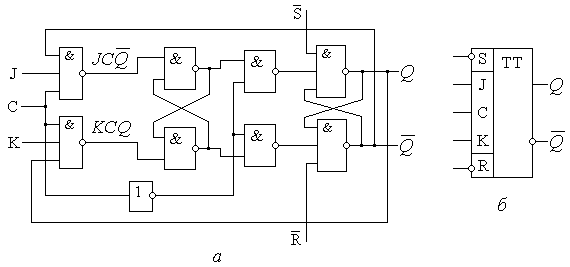

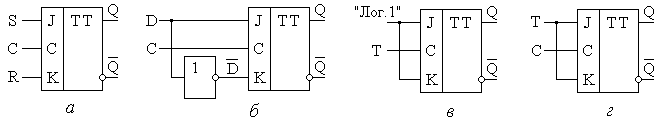

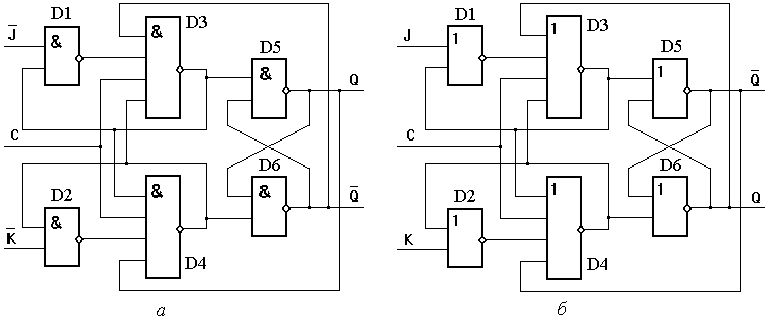

Соответствующее таблице логическое выражение имеет вид: Поскольку при подаче единицы на входы J- и K триггер инвертирует свое состояние, т.е. выполняет функцию Т-триггера, то логично предположить, что структура синхронного JK-триггера должна повторять структуру T-триггера, т.е. она должна быть двухступенчатой. В принципе схема JK-триггера будет отличаться от схемы T-триггера только тем, что входные стробирующие вентили, входящие в состав RS-триггера первой ступени, должны содержать дополнительные выводы для синхронизируемых входов J и K. Т.е. входной каскад формирования стробированных сигналов  Рис. 9.12. Структура синхронного JK-триггера с входами асинхронной установки (а) и его условное графическое обозначение (б). Триггер JK-типа относится к разряду универсальных, поскольку на его основе можно получить схемы, выполняющие функции RS-, D- и T-триггеров. Поскольку правила функционирования JK-триггера не нарушают правил функционирования RS-триггера, а только дополняют его неопределенное состояние конкретным, то для реализации функций RS-триггера JK-триггер можно использовать без каких либо изменений. Достаточно сигнал S подать на вход J, а сигнал R – на вход K (рис. 9.13,а). Для реализации на базе JK-триггера функций D-триггера необходимо избавиться от свойства парафазности JK-триггера, установив дополнительный инвертор, формирующий инверсное значение сигнала  Рис. 9.13. Реализация на базе синхронного JK-триггера функций синхронного RS-триггера (а), D-триггера (б), асинхронного T-триггера (в) и синхронного T-триггера (г). Также как и в случае D-триггера, в JK- и T-триггерах часто вход синхронизации C реализуется по принципу динамического управления. Пример построения схемы синхронного JK-триггера с динамическим управлением на основе элементов И-НЕ приведен на рис.9.14,а, а на основе элементов ИЛИ-НЕ – на рис.9.14,б. Обе схемы идентичны и построены по принципу трех триггеров, как и схема рис.9.7. Хранение записаной информации осуществляется асинхронным RS-триггером на вентилях D5 и D6, а коммутация входных сигналов и динамическое управление - триггерами на вентилях D1, D2, D3 и D4. В первой схеме срабатывание триггера будет осуществляться по переднему фронту сигнала С, а на второй – по заднему.  Рис.9.14. Схема синхронного JK-триггера с динамическим управлением на элементах И-НЕ (а) и ИЛИ-НЕ (б). В маркировке микросхем для обозначения функции RS-триггера используют комбинацию символов «ТР», функции D-триггера - комбинацию символов «ТМ» и функции JK-триггера – комбинацию символов «ТВ». Микросхемы триггеров T-типа встречаются редко, поскольку они легко получаются из JK-триггеров. | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||