Последний вариант цифровой электроники. Последний вариант цифровой электроники (1). Тема Математическое введение в цифровую технику. 11

Скачать 2.28 Mb. Скачать 2.28 Mb.

|

|

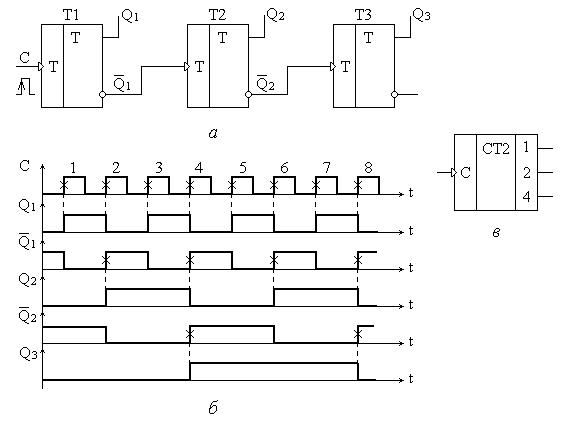

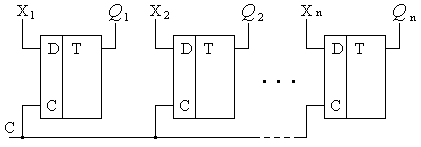

9.2. Счетчики. Счетчики представляют собой последовательностые цифровые устройства и предназначены для выполнения операций счета и хранения кода числа подсчитанных импульсов. Счетчики занимают важное место в качестве элементой базы цифровой измерительной аппаратуры, поскольку на их основе строятся делители частоты, счетные и интегрирующие аналого-цифровые преобразователи, частотомеры, фазометры и прочие устройства. Существуют различные схемы счетчиков, отличающихся назначением, типом используемых триггеров, организацией связи между ними, порядком смены состояний. По порядку изменения состояний счетчики бывают с естественным и произвольным порядком счета. В первых значение кода каждого последующего состояния счетчика отличается на единицу от кода предыдущего состояния. В счетчиках с произвольным порядком счета значения кодов соседних состояний могут отличаться более чем на единицу. Счетчики также подразделяются на простые и реверсивные. Простые счетчики делятся на суммирующие и вычитающие. В суммирующих счетчиках код последующего состояния имеет большее значение, чем код предыдущего состояния, а в вычитающих – меньшее значение. Реверсивные счетчики могут работать как в режиме суммирования, так и в режиме вычитания. Основными параметрами счетчика являются: модуль счета или коэффициент пересчета Ксч; быстродействие счетчика. Модуль счета Ксч характеризует число устойчивых состояний счетчика, т.е. предельное число импульсов, которое может быть им сосчитано. После поступления Ксч входных импульсов счетчик возвращается в исходное состояние. Такие счетчики называются также делителями на число, равное Ксч.. По модулю счета счетчики подразделяются на двоичные, у которых Быстродействие счетчика в свою очередь определяется двумя величинами: разрешающей способностью временем установки tуст кода счетчика, т.е. интервалом времени между моментом поступления входного сигнала и моментом завершения перехода счетчика в новое устойчивое состояние. Поскольку счетчики представляют собой класс ПЦУ, то и синтез их целесообразно выполнять на основе базовых элементов ПЦУ, т.е. триггерах. Количество триггеров для двоичных счетчиков определяется формулой: Для недвоичных счетчиков количество триггеров следует выбирать из условия: где 9.2.1. Двоичные счетчики. Наиболее удобным базовым элементом для построения счетчиков является счетный триггер Т-типа. Такой триггер по сути является простейшим счетчиком с  Рис. 9.15. Схема трехразрядного двоичного суммирующего счетчика на основе Т-триггеров с прямым динамическим счетным входом (а), его временная диаграмма (б) и УГО (в). Таблица 9.7.

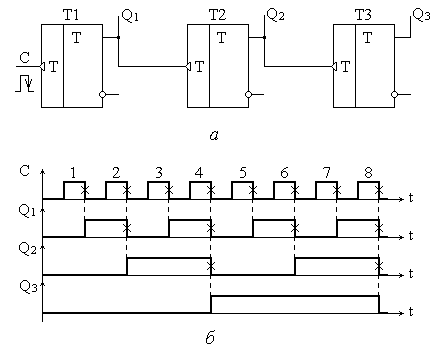

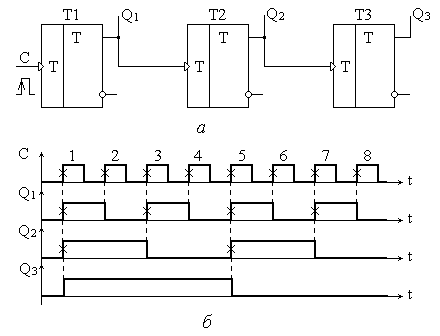

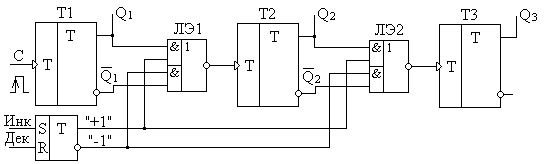

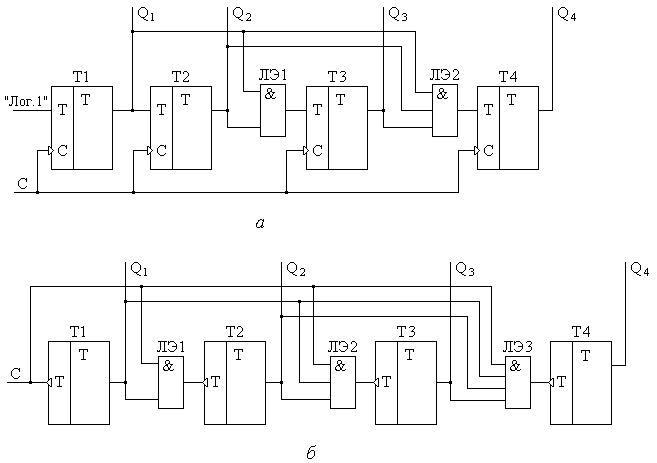

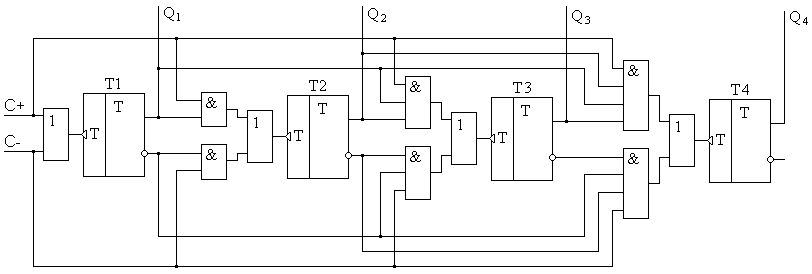

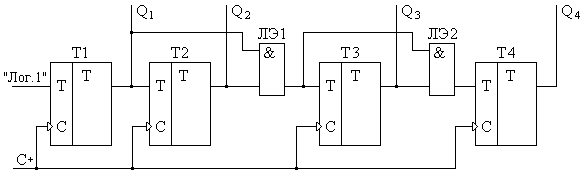

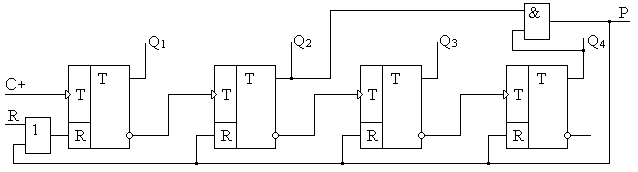

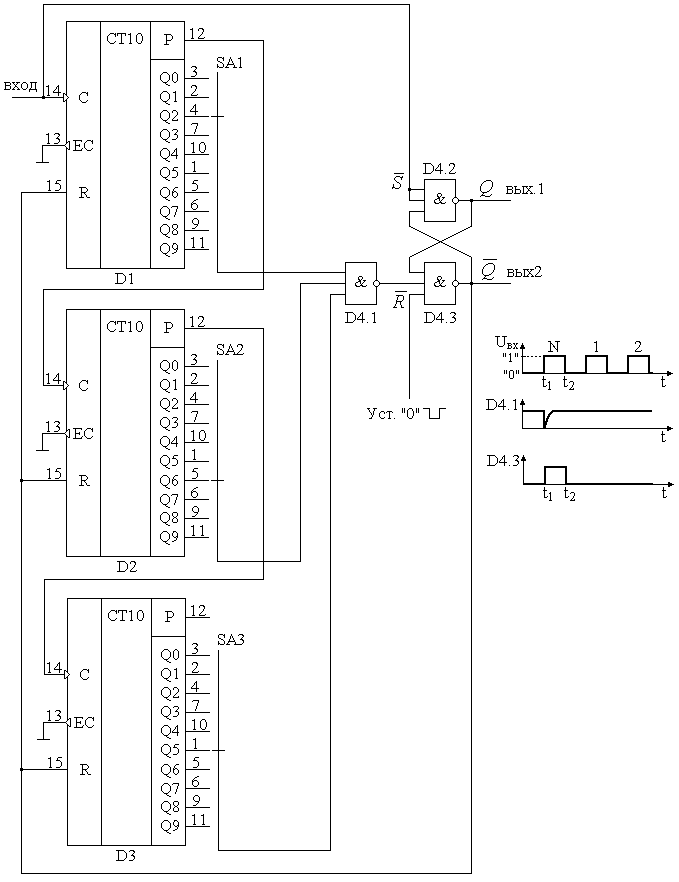

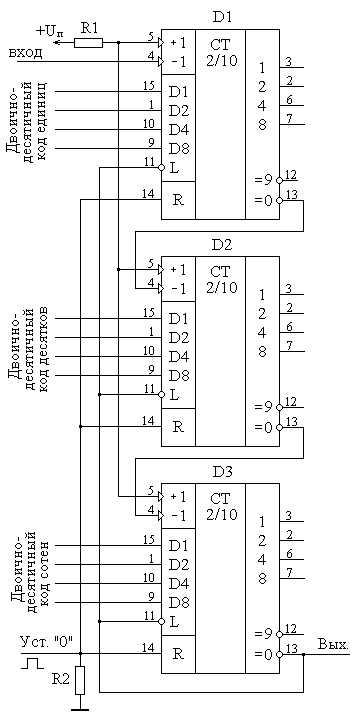

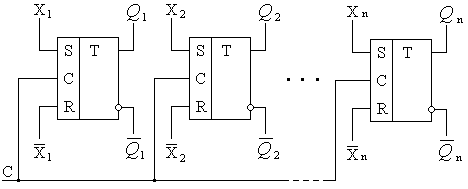

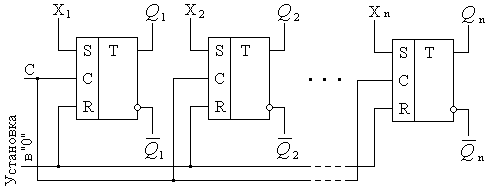

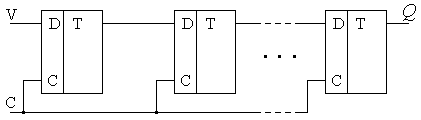

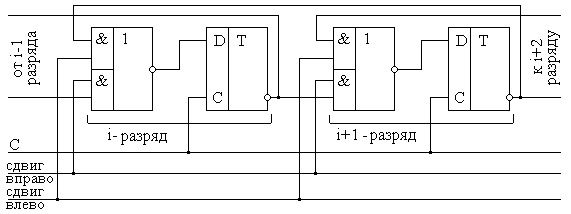

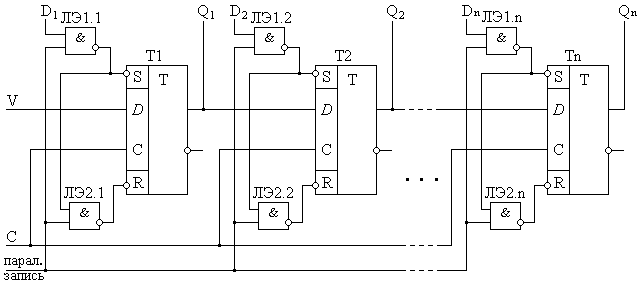

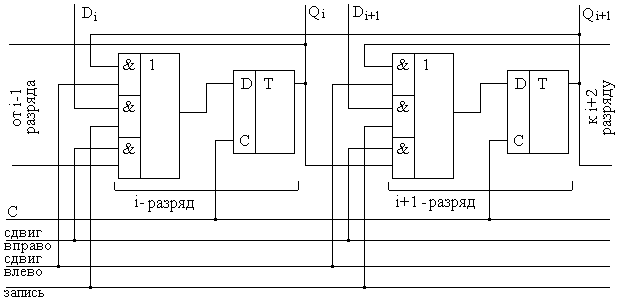

Суммирующий счетчик можно построить и на базе Т-триггеров с инверсным динамическим счетным входом. При этом, поскольку срабатывание триггеров происходит по заднему фронту счетного импульса, нет необходимости задействовать инверсные выходы  Рис. 9.16. Схема трехразрядного двоичного суммирующего счетчика на основе Т-триггеров с инверсным динамическим счетным входом (а) и его временная диаграмма (б). Для выполнения операции вычитания достаточно изменить в электрических связях соответствующих схем используемые выходы триггеров на выходы с обратными логическими уровнями, либо использовать триггеры с входами обратного типа динамического управления. Если вычитающий счетчик реализуется на базе Т-триггеров с прямым динамическим входом, то сигналы на входы последующих триггеров необходимо подавать с прямых выходов предыдущих триггеров (рис. 9.17,а). Временная диаграмма работы счетчика, псотренного по такой схеме, приведена на рис. 9.17,б. Из временной диаграммы видно, что с каждым последующим счетным импульсом выходной код уменьшается на единицу (декрементируется). С последним восьмым импульсом счетчик возвращается в исходное нулевое состояние.  Рис. 9.17. Схема трехразрядного двоичного вычитающего счетчика на основе Т-триггеров с прямым динамическим счетным входом (а) и его временная диаграмма (б). Таким образом, путем переключения выходов с инверсных на не инверсные и обратно, можно получить как суммирующие, так и вычитающие счетчики. Это свойство положено в основу построения реверсных счетчиков. Коммутацию прямых или инверсных выходов триггеров предыдущих разрядов на входы триггеров последующих разрядов удобно выполнять с помощью элементов 2И-ИЛИ или 2И-ИЛИ-НЕ. На схеме рис. 9.18 показан пример реализации трехразрядного реверсивного счетчика на основе T-триггеров с прямым динамическим счетным входом и элементов 2И-ИЛИ-НЕ в качестве комуутаторов. При логическом нуле на линии «-1» и логической единице на линии «+1», на выходе верхней структуры И элементов ЛЭ1 и ЛЭ2 формируется результат с выходов Q1 и Q2 соответствующих триггеров. На выходе нижней структуры И присутствует логический нуль, в результате чего выходы  Рис. 9.18. Схема трехразрядного одноканального двоичного реверсивного счетчика. В рассмотренных счетчиках срабатывание триггеров происходит поочередно друг за другом, т.е. последовательно. Такие счетчики также называются асинхронными. Их недостаток состоит в том, что увеличивается общее время установления tуст с увеличением числа триггеров. Кроме того, появление промежуточных комбинаций может привести к ложному срабатыванию следующего устройства, подключенного к счетчику. Между тем, из таблицы 9.7 видно, что если значение младшего разряда меняется каждый раз с приходом счетного импульса, то в остальных разрядах значения будут меняться на противоположные только в тех случаях, когда в предшествующем состоянии выходного кода во всех предыдущих разрядах были единицы. Указанное правило положено в основу работы синхронных счетчиков. Идея синхронного счетчика заключается в построении внешней комбинационной схемы, формирующей сигналы, согласно которым будет происходить одновременное переключение только части триггеров в зависимости от текущего выходного кода. Причем эти сигналы должны быть сформированы до поступления очередного счетного импульса. Счетный импульс должен поступать на все триггеры одновременно. Для реализации такого счетчика можно использовать как тактируемые Т-триггеры, так и асинхронные. Пример построения синхронного счетчика на базе тактируемых T-триггеров приведен на рис. 9.19,а. В схеме синхронного счетчика Т-триггер текущего разряда должен включиться в счетный режим и поменять свое состояние на противоположное с приходом каждого тактового импульса только в том случае, если выходы всех триггеров предыдущих разрядов установлены в единицу. Для этих целей необходимо использовать схему совпадения единиц, т.е. вентили И (ЛЭ1 и ЛЭ2). Срабатывание всех триггеров происходит одновременно по общему тактовому сигналу синхронизации С, который является счетным импульсом для всего счетчика. Схема синхронного счетчика на базе асинхронных T-триггеров приведена на рис рис. 9.19,б. Принцип ее работы аналогичен принципу работы первой схемы. Отличие заключается лишь в том, что вентили И во второй схеме объединяют не только единичные состояния выходов триггеров младших разрядов, но и пропускают эти единичные сигналы на входы триггеров последующих разрядов только при наличии тактового сигнала синхронизации C, т.е. одновременно. Задержка в обоих схемах равна времени срабатывания одного триггера.  Рис. 9.19. Схема синхронного четырехразрядного суммирующего счетчика с параллельным переносом на основе T-триггеров синхронных (а) и асинхронных (б). Путем анализа работы обеих схем счетчиков рис. 9.19 несложно показать, что они являются суммирующими. Чтобы синтезировать схему вычитающего счетчика, необходимо использовать выходы триггеров с противополжными состояниями. Используя принцип коммутации прямых или инверсных выходов триггеров, можно реализовать реверсивный синхронный счетчик, изображенный на рис 9.20. Такой счетчик имеет два независимых тактовых входа для режимов суммирования C+ и вычитания C-, которые также являются и стробирующими импульсами для вентилей И, коммутирующих прямые или инверсные выходы триггеров предыдущих разрядов на входы триггеров последующих разрядов. Такой счетчик называется еще двухканальным.  Рис. 9.20. Схема двухканального синхронного четырехразрядного реверсивного счетчика с параллельным переносом Изображенные на рис.9.19 и рис.9.20 счетчики называются счетчиками с параллельным переносом, поскольку сигналы на все элементы И, формирующие единичные переносы, подаются с выходов триггеров одновременно в параллельном виде. Недостатком счетчиков с параллельным переносом является необходимость использования в случае увеличения разрядности счетчика элементов И с большим числом входов. При этом выходы триггеров должны обладать высокой нагрузочной способностью. Поэтому многоразрядные счетчики строят по групповому принципу. Согласно этому принципу, весь счетчик структурно реализуется путем соединения отдельных групп небольшой разрядности с параллельным переносом внутри этих групп. Сигнал переноса из очередной группы формируется элементом И, объединяющим выходы всех триггеров данной группы. Сформированный сигнал переноса предыдущей группы подается на счетный вход последующей группы. Общая задержка такого счетчика определяется суммой задержек каждой группы. Другой вариант построения синхронного счетчика – это структура со сквозным переносом. В таких структурах перенос формируется с выходов триггеров только соседних разрядов, имеющих единичные уровни. Для этих целей достаточно использовать только двухвходовые элементы И при любой разрядности счетчика (рис. 9.21). Перенос между разрядами осуществляется через каждый элемент И (ЛЭ1 и ЛЭ2) в их последовательной структуре. Отсюда следует, что общее время срабатывания всего счетчика определяется временем срабатывания одного триггера и суммарным временем задержки последовательной цепи логических элементов И. Выигрыш по быстродействию в такой структуре осуществляется за счет меньшего времени срабатывания одного логического элемента по сравнению со временем срабатывания одного триггера. При достаточно большой разрядности счетчика, суммарное время задержки во всех элементах И может оказаться значительным и сравняться с временем срабатывания одного триггера, что недопустимо.  Рис. 9.21. Схема четырехразрядного суммирующего счетчика со сквозным переносом. 9.2.2. Недвоичные счетчики. Как было сказано раньше, недвоичные счетчики имеют модуль счета Наибольший интерес среди недвоичных счетчиков представляют двоично-десятичные счетчики с Ксч=10, которые строятся на основе четырех счетных триггеров. Важность этого класса счетчиков заключается в том, что с их помощью легко может быть осуществлен вывод содержимого счетчика в десятичном коде. Действительно каждый двоично-десятичный счетчик имеет десять устойчивых состояний и соответствует одному разряду десятичной системы счисления. Пример организации схемы асинхронного двоично-десятичного суммирующего счетчика показан на рис.9.22. Для того, чтобы счетчик имел модуль счета Ксч=10, необходимо его обнулить десятым счетным импульсом, т.е. из выходного кода 10102 сформировать обратную связь, обнуляющую все триггеры счетчика. Такой сигнал обратной связи будет сформирован схемой совпадения единиц (вентилем И) второго и четвертого разрядов. Этот же сигнал будет являться сигналом переноса P в счетчик следующей старшей десятичной декады при построении многорязрядного двоично-десятичного счетчика. Вентиль ИЛИ в схема используется для пропускания на триггеры как сигнала сброса по обратной связи, так и внешнего сигнала сброса R.  Рис.9.22. Схема асинхронного двоично-десятичного суммирующего счетчика. Аналогично рис.9.22 можно строить счетчики с любым модулем счета как суммирующие, так и вычитающие, как синхронные, так и асинхронные. В условном графическом обозначении функция двоичного счетчика определяется символами «СТ» или «СТ2». В случае если счетчик не двоичный, то его модуль счета в УГО определяется соответствующей цифрой рядом с обозначением «СТ». В маркировке микросхем счетчики кодируются символами «ИЕ». Существуют микросхемы счетчиков, в которых интегрирован выходной дешифратор. В таких счетчиках выходной код будет унитарным. Двоично-десятичный счетчик с внутренним дешифратором называется десятичным. В качестве примера можно привести микросхему ИЕ8 десятичного счетчика КМОП-серии (напрмер, К176ИЕ8 и К561ИЕ8). Интересно использование данной микросхемы в схеме делителя частоты с переключаемым коэффициентом деления (рис.9.23). Сама микросхема работает следующим образом. При подаче сигнала высокого уровня на вход сброса R высокий потенциал устанавливается на выходе Q0 и на выходе переноса Р, на остальных выходах устанавливаются логические нули. Работа счетчика осуществляется положительными перепадами на входе С. В этом случае, вход ЕС является входом разрешения счета, и счет будет осуществляться при подаче на него логического нуля. При подаче на вход ЕС логической единицы счет прекращается, и состояние счетчика сохраняется. Можно подавать счетные импульсы и на вход ЕС. В этом случае вход С становится входом разрешения счета. Счет будет производиться при логической единице на входе С по отрицательным перепадам на входе ЕС. По мере счета логическая единица последовательно перемещается по выходам от выхода Q0 до Q9, после чего снова на выход Q0 и весь цикл повторяется. На выходе переноса Р низкий уровень появляется в момент, когда логическая единица появляется на выходе Q5. Снова логическая единица на выходе переноса Р появляется в момент появления логической единице на выходе Q0. Выход переноса Р используется для наращивания разрядности путем последовательного соединения счетчиков друг с другом.  Рис.9.23. Схема делителя частоты с переключаемым коэффициентом деления и временная диаграмма работы триггера. Переключателем SA1 в схеме устанавливают единицы необходимого коэффициента деления, переключателем SA2 – десятки и переключателем SA3 – сотни. Когда микросхемы устанавливаются в состояния, набранные на переключателях, на выходе элемента D4.1 появляется логический ноль. До этого момента асинхронный RS-триггер на элементах И-НЕ D4.2 и D4.3 счетными импульсами, подаваемыми на вход При большом разбросе длительности переходных процессов и порогов срабатывания счетчиков D1 - D3 по входам R возможен случай, когда одна из микросхем устанавливается в нуль раньше других и сигнал низкого уровня на выходе D4.1 снимается раньше, чем остальные микросхемы установятся в нуль. В случае же использования триггера на элементах D4.2 и D4.3 длительность сигнала на входах сброса в нуль всех микросхем счетчиков равна длительности положительного импульса на входе делителя, т.е. t2-t1. Принцип организации недвоичного модуля счета путем предварительной записи в триггеры счетчика определенного числа проиллюстрируем схемой рис.9.24. В схеме используются микросхемы параллельных двоично-десятичных реверсивных счетчиков К155ИЕ6 (D1, D2, D3). Микросхемы снабжены входами D1…D4 предварительной установки выходного кода, на которые подается параллельный четырехразрядный двоично-десятичный код модуля счета всего делителя частоты. Передача этого кода на соответствующие выходы 1, 2, 4, 8 микросхем осуществляется логическим нулем на входе L. Положительный счет в микросхеме К155ИЕ6 осуществляется подачей тактовых импульсов на прямой динамический вход «+1». При этом на входе «–1» и L должны быть логические единицы. Если счетные импульсы подавать на прямой динамический вход «–1», а на входы «+1» и L – логические единицы, то счетчик будет выполнять операцию обратного счета. При каждом десятом импульсе будет формироваться короткий выходной нулевой импульс на выходе «=9» в режиме суммирования и на выходе «=0» в режиме вычитания.  Рис.9.24. Схема делителя частоты с цифровым управлением модулем счета. Таким образом, если соединить выходы «=0» счетчиков предыдущих разрядов с входами «–1» последующих разрядов, а на входы «+1» подать логическую единицу (подключить к потенциалу питания через ограничительный резистор R1), счетчики делителя будут работать в режиме декремента. На объединенные входы предварительной записи L всех микросхем счетчиков подается сигнал с выхода переноса микросхемы счетчика декады сотен, благодаря чему при достижении нулевого значения в цикле отрицательного счета во все микросхемы будет записываться двоично-десятичный код модуля счета. Цикл счета будет начинаться не с максимального значения 999, а с заданного двоично-десятичным кодом. При необходимости обнуления делителя микросхемы счетчиков снабжены прямым статическим входом сброса R. Резистор R2 подтягивает потенциал входов сброса микросхем счетчиков к пассивному нулевому уровню в отсутсвии сигнала их обнуления. Подобная схема удобна в тех случаях, когда модулем счета необходимо управлять цифровым кодом с выхода какого-либо устройства, например, микроконтроллера. 9.3. Регистры. Регистрами называются последовательностные цифровые устройства, выполняющие функции приема, хранения и передачи информации. Информация в регистре хранится в виде двоичного кода, т.е. представлена комбинацией сигналов логического нуля и логической единицы. Каждому разряду кода, записанному в регистр, соответствует свой разряд регистра, выполненный, на основе триггеров RS-, D- или JK-типов. Регистры выполняют роль запоминающих устройств размером в одно n-разрядное слово, буферных элементов и преобразователей последовательно-параллельных кодов в цифровой аппаратуре, в том числе и измерительного назначения. Основным классификационным признаком, по которому различают регистры, является способ записи информации или кода числа в регистр. По этому признаку можно выделить регистры следующих типов: параллельные; последовательные; последовательно-параллельные. В параллельные регистры запись (считывание) числа осуществляется параллельным кодом, т.е. во все разряды регистра одновременно. Последовательные регистры характеризуются последовательной записью (считыванием) кода числа, начиная с младшего разряда или старшего путем последовательного сдвига кода тактирующими импульсами. В последовательно-параллельных регистрах ввод или вывод информации может осуществляться как в параллельном, так и в последовательном кодах. Время ввода числа в регистр параллельного типа равно времени ввода одного разряда. Время ввода числа в регистр последовательного типа равно nT, где n - число разрядов вводимого числа, а T - период следования тактирующих сигналов, осуществляющих ввод (вывод) информации. По способу представления вводимой информации различают регистры однофазного и парафазного типов. В однофазных регистрах информация вводится по одному каналу (прямому или инверсному). Информация на выходе регистра представляется в прямом, обратном или в обоих кодах. В парафазных регистрах ввод информации осуществляется по двум каналам одновременно (прямому и инверсному), т.е. информация на входе должна быть представлена одновременно в прямом и обратном кодах. Информация на выходе парафазного регистра, как правило, также представляется в прямом и инверсном кодах. В условном графическом обозначении функция регистра задается символами «RG», а в маркировке микросхем – символами «ИР». 9.3.1. Параллельные регистры. Параллельный регистр используется для кратковременного хранения чисел, представленных в параллельном двоичном коде. Поэтому параллельные регистры называются еще регистрами памяти. Рассмотрим способы построения регистров памяти на триггерах RS-типа. Каждый триггер служит для хранения одного разряда числа, значит, для хранения n-разрядного двоичного числа необходимо иметь n RS-триггеров. Как следует из правила работы RS-триггера, для записи в него единицы необходимо подавать единицу на вход S и ноль на вход R, а для записи нуля – наоборот – единицу на вход R и ноль на вход S. Полученный регистр будет парафазным, причем вход S - прямой, а вход R - инверсный. Для синхронной записи во все триггеры одновременно их тактовые входы необходимо объединить в одну шину C (рис. 9.25).  Рис. 9.25. Схема параллельного парафазного регистра на синхронных RS-триггерах. Если требуется синтезировать однофазный параллельный регистр на RS-триггерах, т.е. их входы R при записи не использовать, необходимо до записи установить все триггеры в нулевое состояние. Для этого нужно объединить все входы R и при подаче на информационные входы S сигнала с уровнем логического нуля, подать на объединенные входы R логические единицы (рис. 9.26). Таким образом осуществляется предварительная установка триггеров в нулевое состояние. Если теперь на входы S соответствующих триггеров подать значения записываемых разрядов исходного кода, то они зафиксируются на выходах триггеров. Таким образом, при реализации регистров на основе RS-триггеров требуется подача разрядов исходного числа в прямом и инверсном коде, либо предварительное обнуление всех триггеров, что не всегда является удобным. В этом отношении удобны регистры на D-триггерах. В них информация может быть установлена по одному входу и без предварительной установки в ноль. Структура параллельного регистра на D-триггерах приведена на рис. 9.27.  Рис. 9.26. Схема параллельного однофазного регистра на синхронных RS-триггерах.  Рис. 9.27. Схема параллельного регистра на D-триггерах. 9.3.2. Последовательные регистры. Последовательный регистр предназначен для кратковременного хранения информации, но, в отличие от параллельного регистра, в нем осуществляется логическая операция сдвига кода хранимого числа на любое количество разрядов. Ввод информации в последовательный регистр осуществляется по одному последовательному каналу V. Сдвиг кода числа происходит с помощью синхронизирующих импульсов С, в результате подачи которых осуществляется сдвиг всех разрядов кода числа со входа к выходу или наоборот. Как и в случае параллельных регистров, последовательный регистр может быть синтезирован на базе триггеров RS-типа (JK-типа), но наиболее удобным для этих целей является использование D-триггеров (рис. 9.28). Из рисунка видно, что информация с первым тактирующим импульсом с входа V передается на выход первого и вход второго триггеров. С приходом второго тактирующего импульса информация из первого триггера перепишется на выход второго триггера. На выход первого триггера запишется новое значение с входа V. Таким образом, будет осуществляться сдвиг исходного кода вправо. Отсюда последовательные регистры называются еще регистрами сдвига. Информация выводится из триггера по одному выходу Q.  Рис. 9.28. Схема последовательного регистра. Для построения последовательного реверсивного регистра, в котором код числа может сдвигаться как влево, так и вправо, необходимо между триггерами регистра включить устройства управления направлением сдвига. Эти устройства в зависимости от значения управляющих сигналов «сдвиг вправо» и «сдвиг влево» должны переключать входы каждого триггера регистра либо к выходам предыдущего, либо к выходам последующего триггера (рис. 9.29). Поскольку элемент 2И-ИЛИ-НЕ, выполняющий роль коммутатора, инвертирует значения сигналов, то для подачи на входы соответствующих разрядов сдвигаемого кода в прямом виде, необходимо использовать инверсные выходы триггеров. Информацию на самый первый элемент 2И-ИЛИ-НЕ с входа V последовательного ввода необходимо подавать через инвертор. В практических схемах для упрощения процесса управления режимами направления сдвига вместо двух сигналов «сдвиг вправо» и «сдвиг влево», используется только один из этих сигналов. Второй сигнал формируется через инвертор.  Рис. 9.29. Схема последовательного реверсивного регистра. 9.3.3. Последовательно-параллельные регистры. Последовательные регистры находят ограниченное применение. Широкое распространение получили последовательно-параллельные регистры. На их базе строятся преобразователи кодов из последовательного в параллельный и из параллельного в последовательный. Для реализации параллельного вывода информации в последовательном регистре достаточно использовать выходы Qi всех триггеров. Чтобы реализовать ввод информации как в последовательном, так и в параллельном виде, можно использовать D-триггеры с асинхронной установкой в ноль или единицу. Пример такой схемы приведен на рис. 9.30. Как и в последовательном регистре, ввод информации в последовательном коде осуществляется по входу V. Для тактирования сдвига синхровходы всех триггеров объединены. Для возможности введения кода числа в параллельном виде используются элементы И-НЕ ЛЭ1i и ЛЭ2i в i-х разрядах. Элемент ЛЭ1i осуществляет функцию стробирования и инвертирования разряда Di при единичном уровне управляющего сигнала «параллельная запись». В результате на вход S установки в единицу триггера Тi проходит инверсное значение разряда  Рис. 9.30. Схема последовательно-параллельного регистра. На рис.9.31 приводится еще один вариант схемы реверсивного регистра, но с функцией параллельной записи. Схема идентична рассмотренной ранее на рис.9.29 схеме последовательного реверсивного регистра, но вентили И-ИЛИ-НЕ в этой схеме используются не только для выбора разряда подключаемого триггера, но и для записи во все триггеры параллельного кода. Сигнал синхронизации C в схеме используется как для сдвига, так и для записи.  Рис.9.31. Схема реверсивного последовательно-параллельного регистра. Если выход последнего триггера в регистре сдвига соединить с входом первого, то получится кольцевой регистр сдвига. Записанная в его разряды информация под воздействием сдвигающих импульсов будет циркулировать по замкнутому кольцу. Кольцевой регистр иначе называется кольцевым счетчиком. Его модуль счета равен числу разрядов n последовательного кода. Единица, записанная в один из разрядов, периодически будет появляться в нем после того, как будут поданы n сдвигающих импульсов. Если в регистре сдвига к входу первого триггера подключить не прямой выход последнего триггера, а инверсный, то получится так называемый счетчик Джонсона. В счетчике Джонсона в первом цикле сдига будет происходить сдвиг прямого кода, а во втором – инверсного. После чего в счетчик будет записываться уже дважды проинвертироанный код, т.е. прямой. Таким образом, модуль счета его будет вдвое больше, чем у обычного кольцевого счетчика, т.е. будет равен величине 2n. Контрольные вопросы Поясните принципы организации ПЦУ. В чем состоит отличие синхронного RS-триггера от синхронного JK-триггера? Что такое входы асинхронной установки в нуль и единицу? В каких типовых ПЦУ используются в качестве элементной базы D- и T-триггеры? Приведите схемы реализации триггеров RS-, D- и T-типов на базе синхронных JK-триггеров. Чем отличается динамическое управление от статического и каким образом динамическое управление реализуется схемотехнически? Чему равны Kсч восьмиразрядного двоичного и восьмиразрядного двоично-десятичного счетчиков? Изобразите схему и временные диаграммы работы трехразрядного двоичного вычитающего счетчика на основе T-триггеров с инверсным динамическим счетным входом. В чем отличие схем и принципов функционирования счетчиков с параллельным и сквозным переносами? В чем заключается принцип построения недвоичных счетчиков и как реализовать счетчик с Ксч=18 на базе двоичных счетчиков? Объясните принцип работы последовательно-параллельного регистра. |